随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层 PCB的设计,即叠层结构设计。

好的叠层设计不仅可以有效地提高电源质量、减少串扰和EMI、提高信号传输性能,还能节约成本,为布线提供便利,这是任何高速PCB设计者都必须首先考虑的问题。

一.PCB叠层结构设计10大通用原则

1.信号层与地层或电源层相邻,避免两信号层直接相连

在多层PCB中,通常包含有信号层(S)、电源层(P)平面和地层(GND),三者如何排布呢?

电源层和地层通常是没有分割的实体平面,能为相邻信号走线的电流提供一个好的低阻抗的电流返回路径。因此,信号层多与电源层或地层相邻。而且电源层和地层使用大面积铺铜(故电源层和地层也叫铺铜层),其大铜膜能为信号层提供屏蔽,利于阻抗控制和提高信号质量。

另外,应尽量避免两信号层直接相邻。相邻的信号层之间容易引入串扰,从而导致电路功能失效。在两信号层之间加入地层可以有效地避免串扰。

2.顶层和底层多是信号层

多层PCB的顶层和底层通常用于放置元器件和少量走线,因此多是信号层。一般顶层是元器件,那元器件下面(第二层)可设为地层,提供器件屏蔽层以及为顶层布线提供参考平面。

另外,注意顶层与底层的这些信号走线不能太长,以减少走线产生的直接辐射。

3.参考平面优先选择地层

电源层和地层都可以作为参考平面,且有一定的屏蔽作用。

两者的区别在于:电源层具有较高的特性阻抗,与参考电平存在较大的电位势差;而地层一般作接地处理,并作为基准电平参考点,其屏蔽效果远远好于电源层。

所以,在选择参考平面时,优先选择地层。

4.高速信号层位于信号中间层

电路中的高速信号传输层应该是信号中间层,并且夹在两个铺铜层之间。这样两个铺铜层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个铺铜层之间,不对外造成干扰。

5.电源层与地层最好成对出现

电源层与地层成对出现,缩短电源和地层的距离,可以降低电源的阻抗,利于电源的稳定和减少EMI。尤其是主电源尽可能与其对应地层相邻。在高速情况下,可以加入多余的地层来隔离信号层,但建议不要多加电源层来隔离,因为电源层会带来较多的高频噪声干扰。

6.铺铜层平衡设计

铺铜层,即电源层或地层最好成对称排布,如6层板的第2层与第5层,或者第3层与第4层要一起铺铜,这是考虑到工艺上平横结构的要求,因为不平衡的铺铜层可能会导致PCB膨胀时的翘曲变形。

7.多电源层远离高速信号层

多电源层要注意远离高速数字信号布线。因为多电源层会被分割成几个电压不同的实体区域,如果紧靠多电源层的是信号层,那么其附近的信号层上的信号电流将会遭遇不理想的返回路径,使返回路径上出现缝隙。

8.采用偶数层结构

经典的PCB叠层设计几乎全部是偶数层的,而不是奇数层的。偶数层印制电路板具有成本优势,同时偶数层比奇数层更能避免电路板翘曲。

9.布线组合安排在邻近层

为了完成复杂的布线,走线的层间转换是不可避免的。一个信号路径所跨越的两个层称为一个“布线组合”。最好的布线组合设计是避免返回电流从一个参考平面流到另一个参考平面,而是从一个参考平面的一个点(面)流到另一个点(面)。

因此,布线组合最好安排在邻近层,因为一个经过多层的路径对于返回电流而言是不通畅的。虽然可以通过在过孔附近放置去耦电容或者减小参考平面间的介质厚度等来减小地弹,但也非一个好的设计。

10.相邻信号层布线方向正交

在同一信号层上,应保证大多数布线的方向是一致的,同时应与相邻信号层的布线方向正交。例如,可以将一个信号层的布线方向设为"Y轴”走向,而将另一个相邻的信号层布线方向设为“X轴”走向。

以上是我们进行叠层结构设计时遵循的一些规则,但在实际情况中,有些规则是相互制约的,因此需要根据实际的情况进行权衡决定,得到合理的叠层方案。

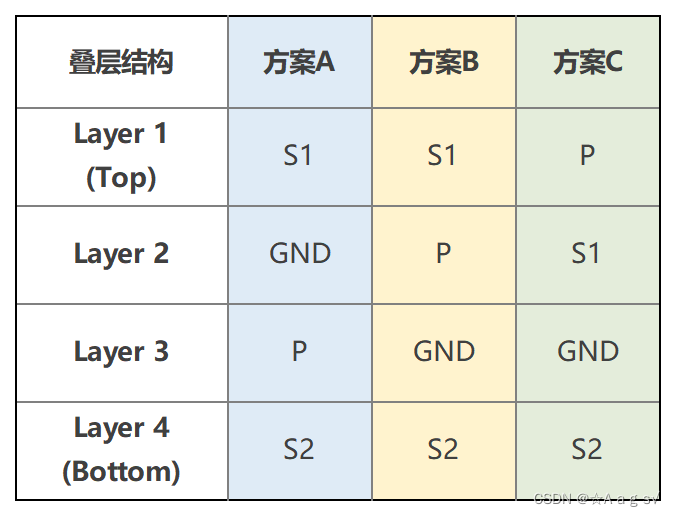

以常用的四层板为例,以下几种叠层方式怎么选?

显然,方案C的电源层和地层缺乏有效的耦合,不应该被采用。那么方案A和方案B应该如何进行选择呢?

一般情况下,设计人员都会选择方案A作为四层板的结构。选择的原因并非方案B不可被采用,而是一般的PCB板都只在顶层放置元器件,所以采用方案A较为妥当。

但是当在顶层和底层都需要放置元器件,而且内部电源层和地层之间的介质厚度较大,耦合不佳时,就需要考虑哪一层布置的信号线较少。对于方案A而言,底层的信号线较少,可以采用大面积的铜膜来与 POWER 层耦合。反之,如果元器件主要布置在底层,则应该选用方案B来制板。

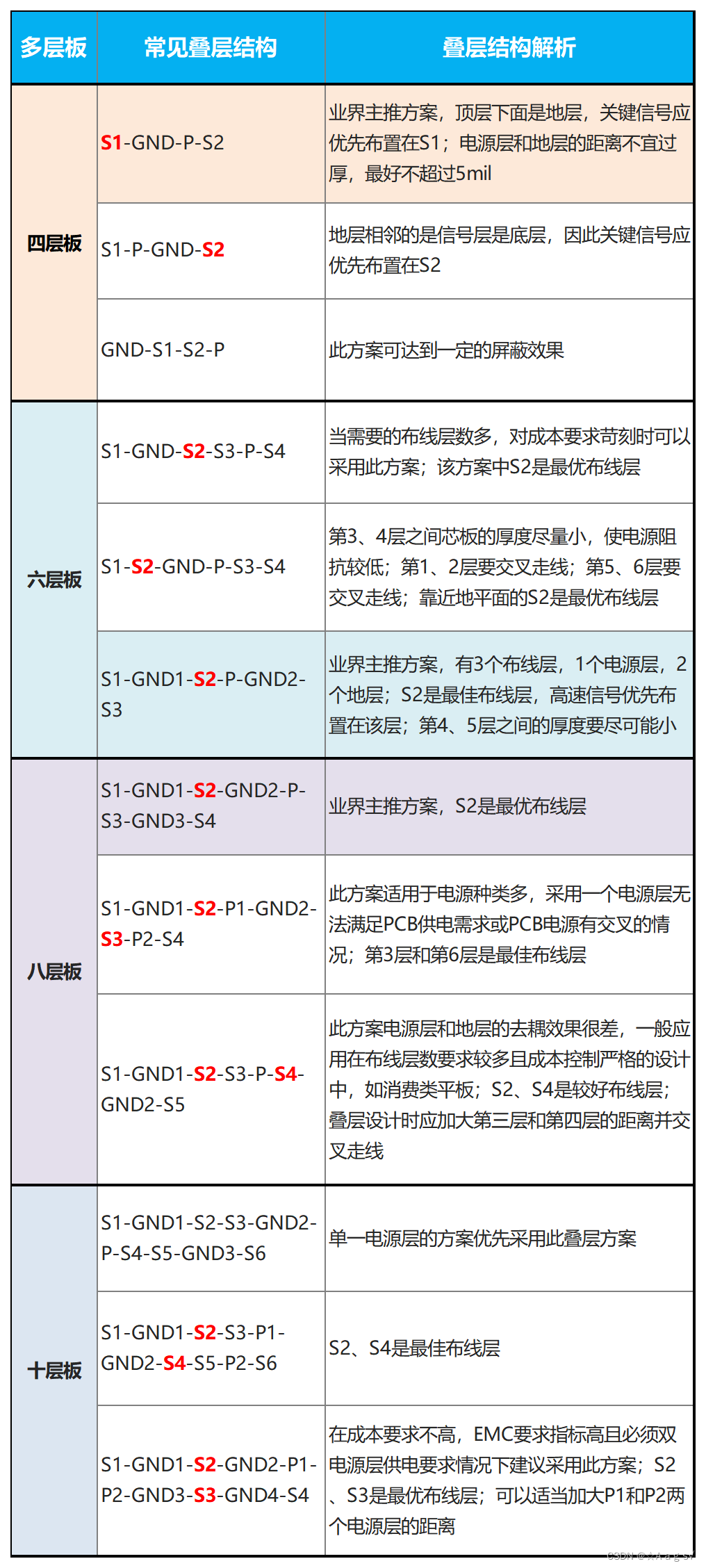

二.多层板常用的叠层结构

下面是常见的4~10层板的叠层结构,每一种叠层都有他的利与弊,有的是便于布局布线,有的是EMC性能比较好,有的是信号完整性比较好,有的是成本较低…实际使用的时候会根据不同的需求选取不同的叠层结构。

2858

2858

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?