数字系统作业之程序改错

前言

本次作业所用软件为Quartus||9.0,所用板载为EPF10K20T144-4。本篇博客仅供参考学习。

注意事项

(1)创建VHDL工程时选择板载系列一定要按照板载芯片上的系列选中。

(2)目前使用的Quartus || 9.0不支持输入汉字的功能,只支持显示汉字的功能,所以想要在上面显示汉字,得先在记事本中写好自己要写的汉字内容,然后再复制粘贴到Quartus || 9.0上的文件中。

(3)安装驱动程序前一定要记得禁止驱动程序签名。

(4)配置完引脚以后一定要记得要再编译一次。

创建一个VHDL工程

1、点击File->new project Wzarid。

2、默认Next即可。

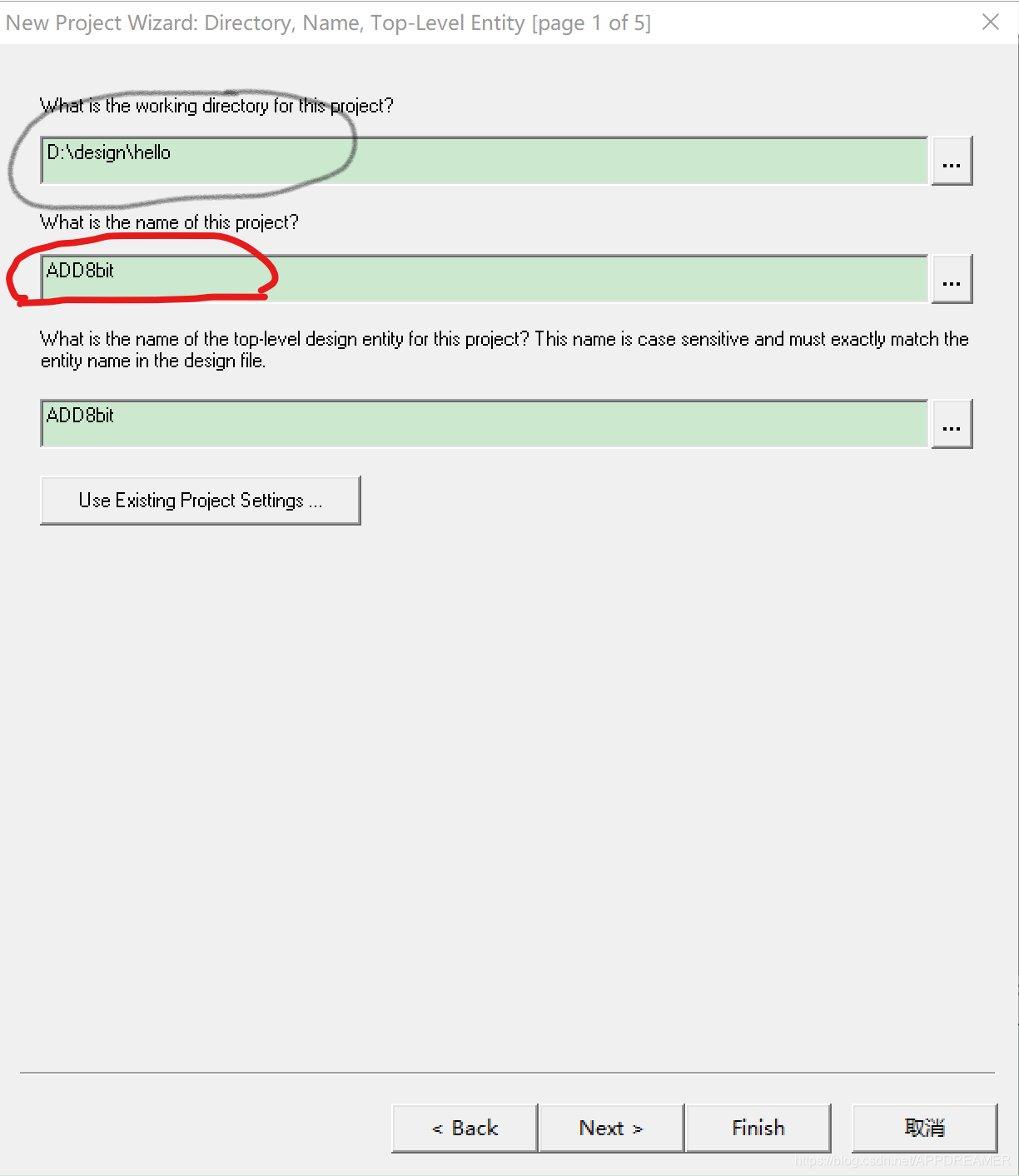

3、在图中灰圈所圈中地方选择工程保存文件,红圈所圈中地方输入项目名称(注:项目名称为自定义,不要出现空格,且当使用VHDL语言编写硬件程序时,要注意实体名一定要和工程名一致,要不然会编译报错),然后点击Next即可。

4、如果需要添加自己已经写好的文件,在红圈圈中的地方找到文件路径,然后点击Add即可添加,若不需要,则默认Next即可。

5、在图中灰圈所圈中地方选择程序所要烧入板载系类,红圈所圈中地方选择板载芯片上所标系列,然后点击Next即可。

6、默认Next即可。

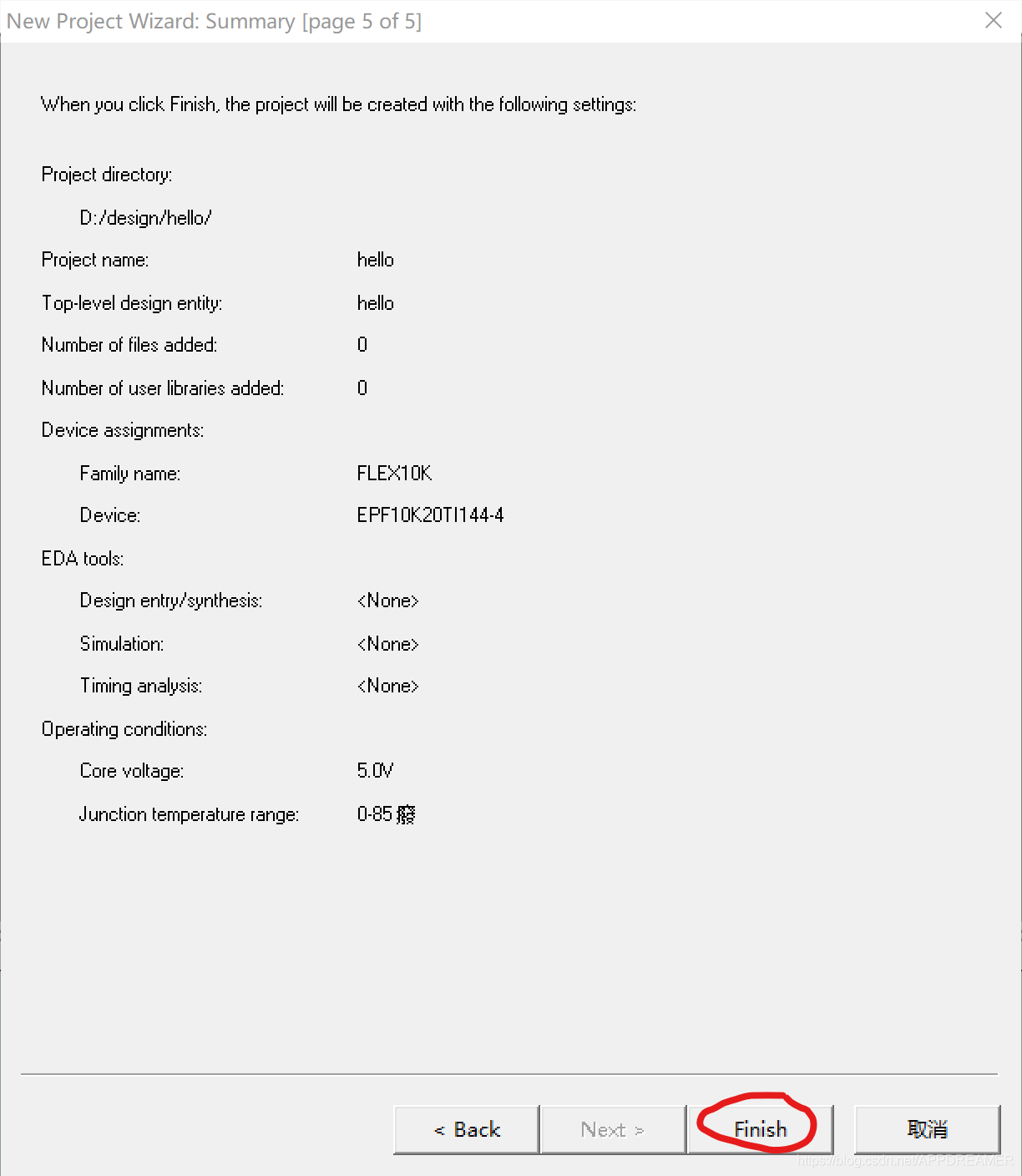

7、默认Finish即可。

创建一个VHDL程序文件

1、点击File->new或直接点击图中红线所圈按钮即可。

2、点击VHDL File即可。

3、在此界面输入自己要写的程序即可。

更改VHDL程序中的错误

1、错误程序如下

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164

ENTITY ADD8bit IS

PORT(A

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1809

1809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?