摘要:本文全面深入地探讨了软错误这一半导体器件领域的关键问题。通过对其基本概念、成因、特点、危害以及预防措施的详细阐述,并结合具体的芯片抗辐照测试数据作为论据,旨在为研究人员提供一份详实可靠的参考依据,帮助其更好地理解软错误问题并探索有效的解决方案。

一、软错误的概念界定

软错误是与硬错误相对的一种半导体器件错误类型。硬错误源于器件本身的不可逆损伤,导致其无法完成预定工作。而软错误则不同,尽管器件功能正常,但在执行任务时会出现错误,例如存储单元内容改变或逻辑状态翻转。幸运的是,这类错误通常可以通过重启系统或重新读写等操作使器件恢复初始状态。这种可恢复性是软错误的一个重要特征,也是其与硬错误的根本区别之一。

二、软错误的成因探究

软错误主要由高能粒子对半导体器件的辐射效应引发。自苏联发射首颗人造卫星以来,人类已发射了众多卫星。这些卫星在太空环境中面临着大量高能粒子的辐射威胁。据统计,超过40%的地球同步卫星故障归因于高能粒子对半导体器件的影响,凸显了软错误对系统正常运行的严重威胁。

高能粒子种类繁多,研究表明,α粒子、重离子、中子易引发单粒子效应,电子辐射主要产生总剂量效应,质子辐射则可导致单粒子效应、总剂量效应和位移损伤效应三种辐射效应。当高能粒子撞击半导体器件时,会在器件内部产生电离现象,形成电荷。这些额外电荷被器件电极收集后形成瞬态电流,进而导致器件状态在未经正常指令的情况下发生改变。

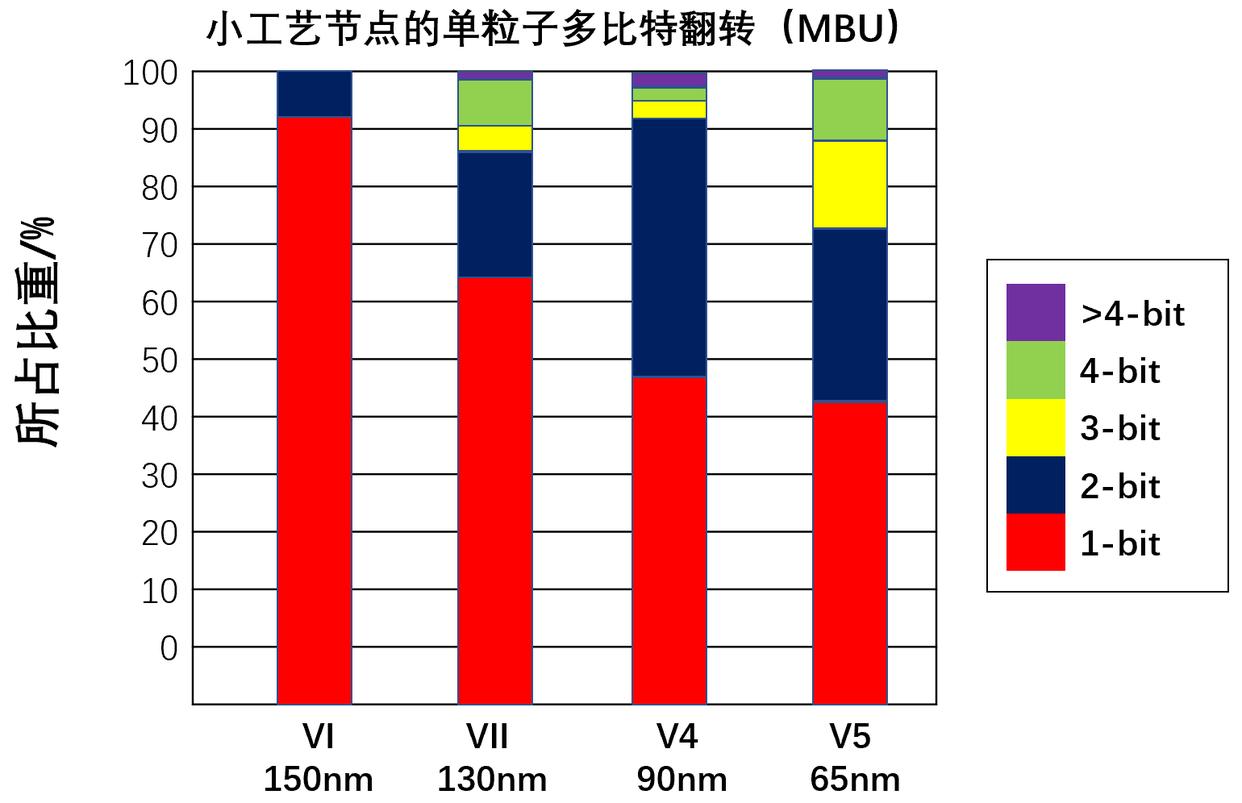

随着半导体工艺的不断进步,器件的小型化、集成化和低功耗程度日益提高,高能粒子对器件的影响也愈发显著,软错误发生的概率不断增加,软错误的种类也日益增多。常见的软错误类型包括单粒子翻转(SEU)、单粒子瞬态(SET)、多位翻转(MBU)、单粒子快速反向(SES)和单粒子功能中断(SEFI),其中SEU和SET对数字集成电路的稳定性影响尤为突出。

三、软错误的特点分析

隐蔽性:软错误在传播过程中极为隐蔽,在正常运行的程序中,系统未必会给出错误提示,用户难以察觉其存在。在海量数据中定位软错误的具体地址更是困难重重,目前尚缺乏特定模式来有效判断软错误。

随机性:由于软错误是由高能粒子轰击引发,其导致的位翻转具有随机性和偶然性。软错误可能发生在器件的不同部位,任何位置都存在发生概率,若在关键位置发生,则可能导致任务失败。

累积性:即使存在软错误,系统仍能继续工作,这意味着软错误会在系统持续运行的同时不断累积。随着累积量的增加,系统的故障率将不断上升,器件的可靠性会持续下降,甚至可能演变为硬错误,即器件发生不可逆损坏。

高发性:研究表明,软错误率往往远高于硬错误率。在大型RAM器件中,软错误率甚至可能比硬错误率高出三个数量级。正因如此,软错误已受到高度重视,并在IEC61508-2:2010等标准中被明确考虑。广泛接受的SiemensSN29500系列标准倡导的软错误率为1200FIT/兆位,而1000FIT/兆位也已被行业普遍接受。

四、软错误的危害阐述

软错误会对系统造成多方面的破坏,包括损坏重要信息、导致系统故障率随软错误累积而提升,以及引发程序控制错误,使系统出现指令之外的动作。例如,在卫星通信系统中,软错误可能导致数据传输错误,进而影响地面控制中心对卫星的指挥和控制;在工业自动化控制系统中,软错误可能引发设备的异常运行,甚至导致生产事故。

依据AEC-Q100与IEC61508这两套权威标准的相关阐述,以130纳米工艺制程的1MbitRAM芯片为研究对象,大气中子单粒子效应所导致的软错误概率逾越了1000FIT的阈值(FIT的明确定义为:在10^9小时的时间跨度内,发生一次故障即计为1FIT。例如,若某一器件的失效率为100FIT,则其平均预期可安全工作时长为10^7小时)。这一数据在表观上虽具有一定规模,但对于具有严格安全等级要求的器件(如应用于汽车制动系统的关键部件),则其潜在风险不容小觑。

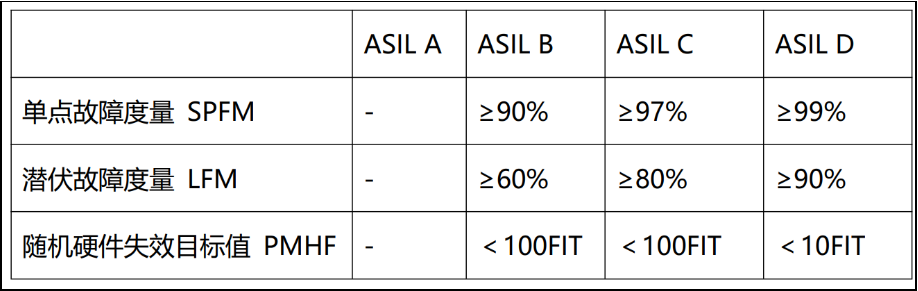

汽车芯片根据其应用场景的危险程度,划分为不同安全等级(QM、ASIL-A至ASIl-D),其中ASIl-D的等级最高,说明其安全要求最严格。行业内通过对芯片的三个指标的计算来划分安全等级,如下图所示。由此可见,1000FIT的故障率远远超过ASIL-B的等级要求。也意味着,对于130nm工艺下的CMOS工艺设计,随着时序存储容量的变大,对于安全设计的要求则越高。

汽车系统的安全等级对于器件是有要求的,特别是ASIL-D等级的动力能源、汽车制动、EBS等系统,对于控制芯片往往要求ASIl-D等级,这些芯片如果在涉及安全控制的环节中出现其后果不堪设想。比如某个刹车系统中指令出现“随机故障”导致需要的制动没有执行,则对于驾驶员和乘客的危害不可估量。而且,软错误的故障来源具有不确定性,设计者需要在每一层都考虑到出现错误的应对方案。

随着工艺水平的提升,现在大多芯片采用28nm,甚至7nm的工艺进行生产,器件的容软错误能力更差,甚至出现了更难进行故障恢复的MBU错误(多bit翻转错误)。实际上,采用28nmCMOS工艺设计的器件比130nm在出现软错误的概率上至少超过3个数量级,这对系统的安全性设计提出了更大的挑战。

五、软错误的预防措施

针对软错误,目前主要有两类预防方法。一类是软件检测技术,通过对软错误引发的控制流错误和数据流错误进行检测来排查问题。另一类是抗辐照加固技术,主要通过工艺设计、电路设计以及算法设计来实现。商业系统常采用电路设计实现抗辐照加固,因为它能在传统制造工艺基础上,利用更精妙的电路设计达到抗辐照加固效果。常见的软错误电路加固方法包括延时加固和冗余技术。延时加固通过采用延时电路来过滤单粒子效应导致的瞬态脉冲;冗余技术则使用重复的电路来实现加固效果,如DICE锁存器等。这些方法虽能有效降低软错误导致的故障、异常及失效问题,但会占用较大面积。例如,在对国科安芯的AS32S601型MCU进行的单粒子效应脉冲激光试验中,温度为24℃,湿度为42%RH。通过扫描方法对芯片进行全芯片扫描,设定不同的激光能量和注量,观察芯片是否出现单粒子效应。在5V工作条件下,从120pJ(对应LET值为(5±1.25)MeV・cm²・mg)的激光能量开始进行全芯片扫描,未出现单粒子效应。当能量提升至1585pJ(对应LET值为(75±16.25)MeV・cm²・mg)时,才监测到芯片发生了单粒子翻转(SEU)现象。这一试验结果为国内在软错误研究领域提供了重要的实测数据和经验参考,有助于进一步理解软错误的产生机制和影响因素,从而为开发更有效的抗软错误技术提供支持。

六、结论

软错误作为半导体器件领域的重要问题,其隐蔽性、随机性、累积性和高发性使其对系统正常运行构成了严峻挑战。深入研究软错误的成因、特点、危害及预防措施,对于提升半导体器件的可靠性、长期稳定性和在恶劣环境下的工作能力具有极为重要的意义。

未来,随着半导体技术的不断发展,我们需要持续探索更为有效的软错误应对策略,以满足日益增长的高性能、高可靠性半导体器件需求。同时,加强国内外在软错误研究领域的合作与交流,共享测试数据和技术成果,将有助于推动整个行业的技术进步,为半导体器件在更广泛领域的应用提供坚实保障。

1156

1156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?