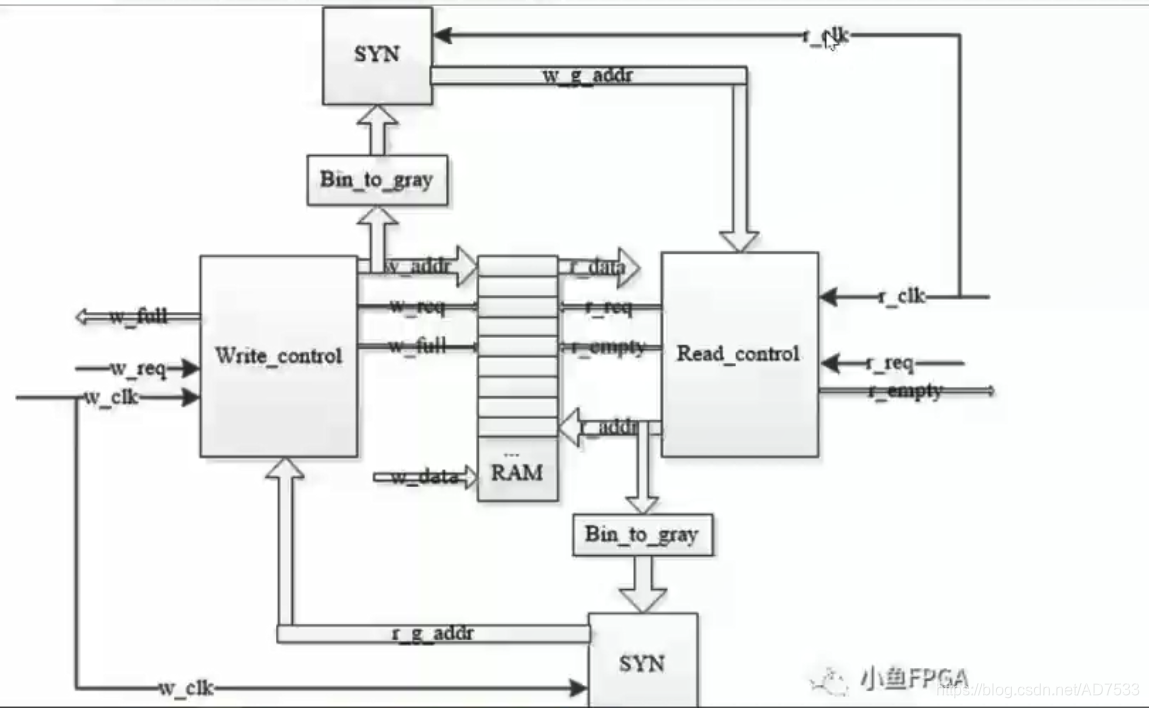

设计思路

w_clk与r_clk不同步,跨时钟域

需要模块:

1、读控制

2、写控制

3、双口RAM

4、Bin2Gray(跨时钟域---亚稳态---需要使用格雷码---减少亚稳态的概率)

5、SYN同步(将w_addr送到读控制模块----比较地址差判断空满,需要r_clk对w_addr同步)

(将r_addr送到写控制模块----比较地址差判断空满,需要w_clk对r_addr同步)

简单来说两级同步就是打两拍、用于跨时钟域设计

&n

本文介绍了一种在不同步时钟域间进行有效数据交换的设计方法。通过使用双口RAM和格雷码转换来减少亚稳态的影响,并采用两级同步技术确保数据一致性。详细解析了读写控制模块的工作原理。

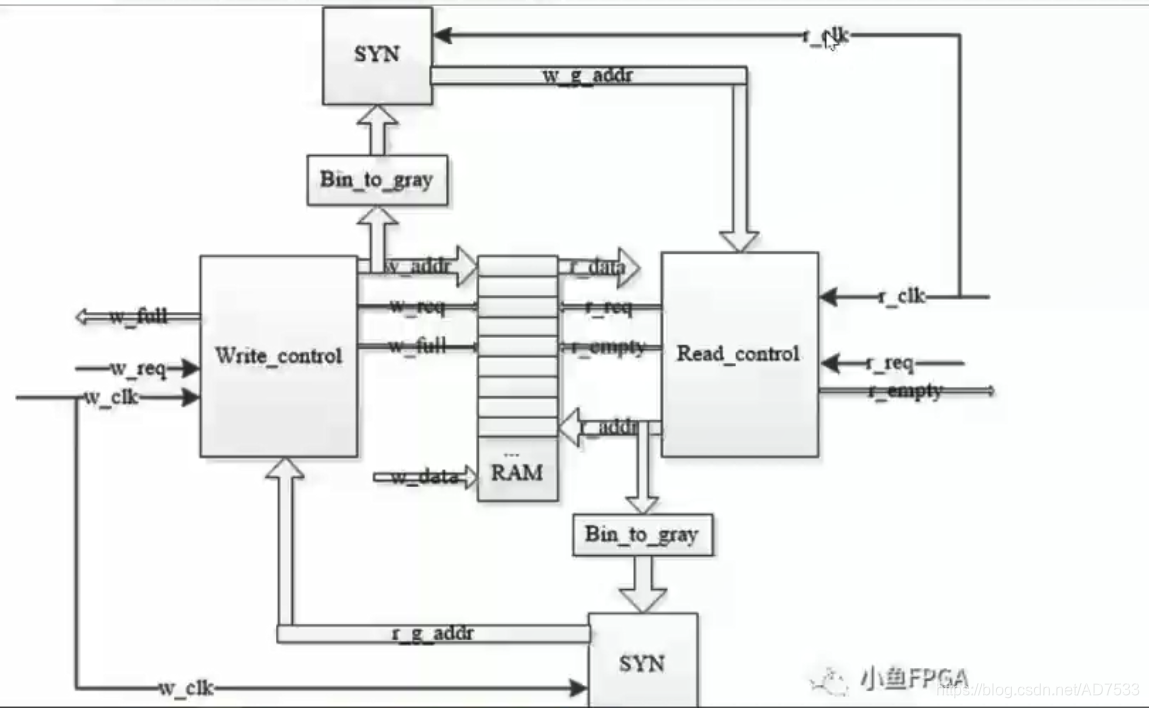

本文介绍了一种在不同步时钟域间进行有效数据交换的设计方法。通过使用双口RAM和格雷码转换来减少亚稳态的影响,并采用两级同步技术确保数据一致性。详细解析了读写控制模块的工作原理。

w_clk与r_clk不同步,跨时钟域

需要模块:

1、读控制

2、写控制

3、双口RAM

4、Bin2Gray(跨时钟域---亚稳态---需要使用格雷码---减少亚稳态的概率)

5、SYN同步(将w_addr送到读控制模块----比较地址差判断空满,需要r_clk对w_addr同步)

(将r_addr送到写控制模块----比较地址差判断空满,需要w_clk对r_addr同步)

简单来说两级同步就是打两拍、用于跨时钟域设计

&n

7985

7985

548

548

1006

1006

977

977

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?