🌈个人主页:小新_-

🎈个人座右铭:“成功者不是从不失败的人,而是从不放弃的人!”🎈

🎁欢迎各位→点赞👍 + 收藏⭐️ + 留言📝

🏆所属专栏: 计算机组成原理 欢迎订阅,持续更新中~~~

✨让小新带着你快乐的学习吧~✨

目录

一、主存扩展及其与CPU的链接

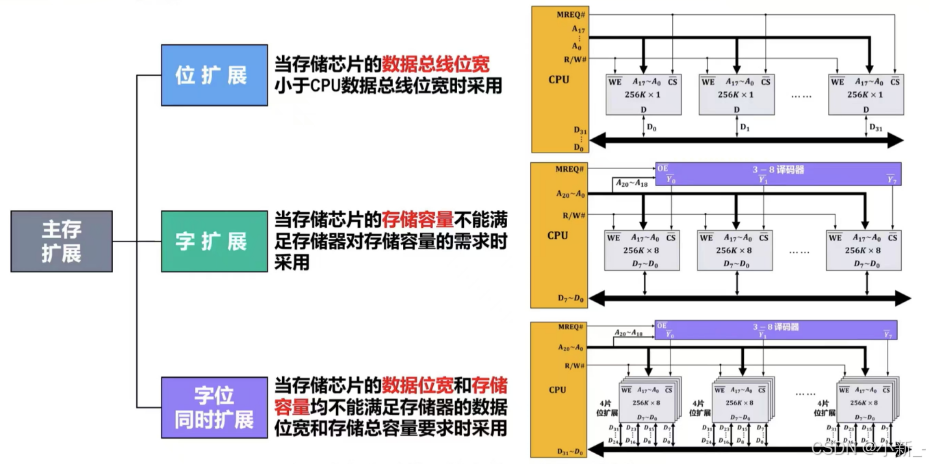

(一)位扩展

当存储芯片的数据总线位宽小于CPU数据总线位宽时,采用位扩展的方式进行扩展。

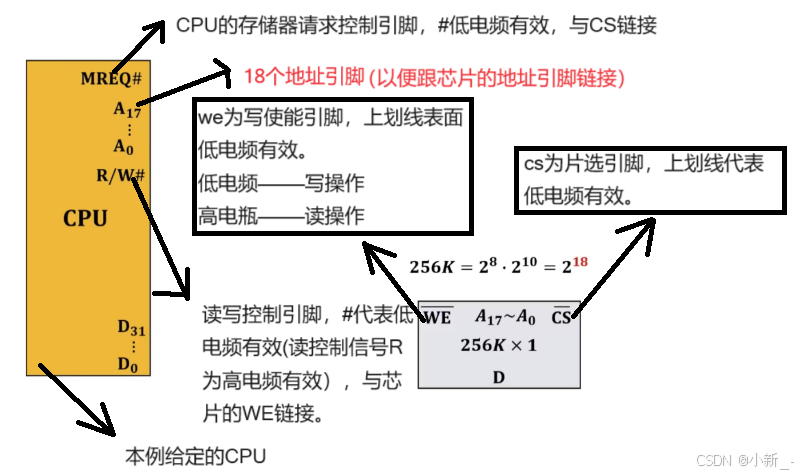

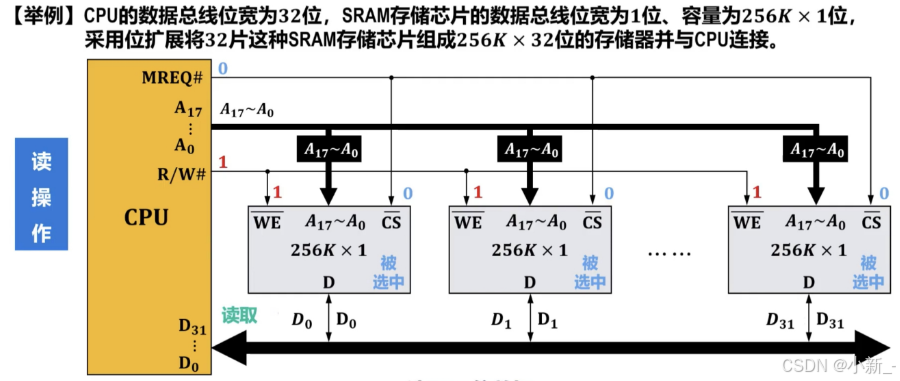

【举例】CPU的数据总线位宽为32位,SRAM存储芯片的数据总线位宽为1位、容量为256Kx1位采用位扩展将32片这种SRAM存储芯片组成256Kx32位的存储器并与CPU连接

本例的主存扩展与CPU链接示意图

接下来是主存对CPU的访问过程:

初始状态下,CPU的存储器请求控制引脚MREQ输出无效电频(高电频,用1来表示),各芯片的片选引脚CS收到该无效电频,因此不被选中工作,进而各自的1位数据线输出位高阻态(可认为未与CPU的数据总线键连接)。CPU的读写控制引脚RW输出高电频,各存储器芯片的写使能引脚WE收到该高电频,由于各存储芯片此时都未被选中工作,因此不理会该信号。而CPU的地址总线和数据总线的输出未知。

假设初始状态下,CPU要进行读操作,CPU的18位的地址总线送出18位地址,各芯片的WE会收到这18位地址,因此当各存储芯片被同时选中工作时,其各自内部该地址所对应的存储单元被同时选中,之后MREQ输出低电频,CS收到该有效电瓶,因此都被选中工作。此时芯片的WE上的信号,是之前R/W输出的高电频,各存储芯片将被选中的存储单元存储的1位数据通过各自的一位数据线传送到CPU的32位数据总线中相应的数据线。之后,CPU通过32位数据总线读取32位数据。

总结:

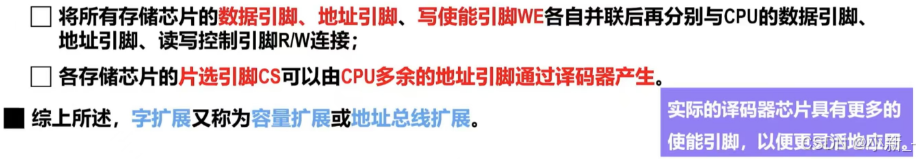

- 将所有存储芯片的地址引脚、写使能引脚WE分别并联后再分别与CPU的地址引脚和读写控制引脚RW连接

- 将各存储芯片的数据引脚依次与CPU的数据引脚进行相应连接

- 将所有存储芯片的片选引脚CS并联后与CPU的存储器请求控制引脚MREQ相连:

(二)字扩展

当存储芯片的存储容量不能满足存储器对存储容量的需求时,采用字扩展的方式进行扩展。

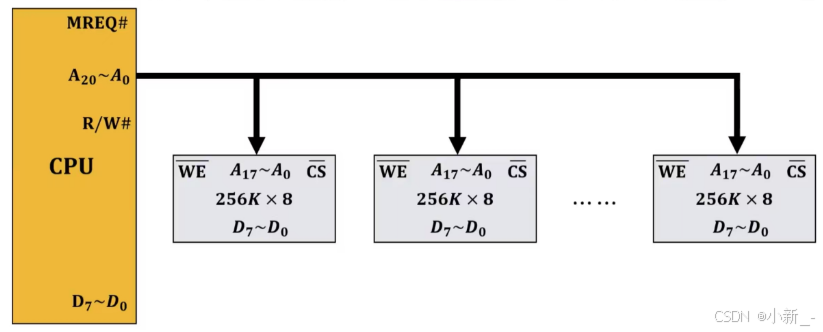

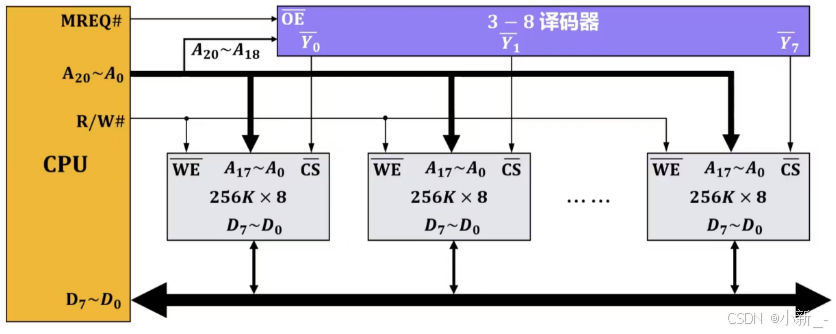

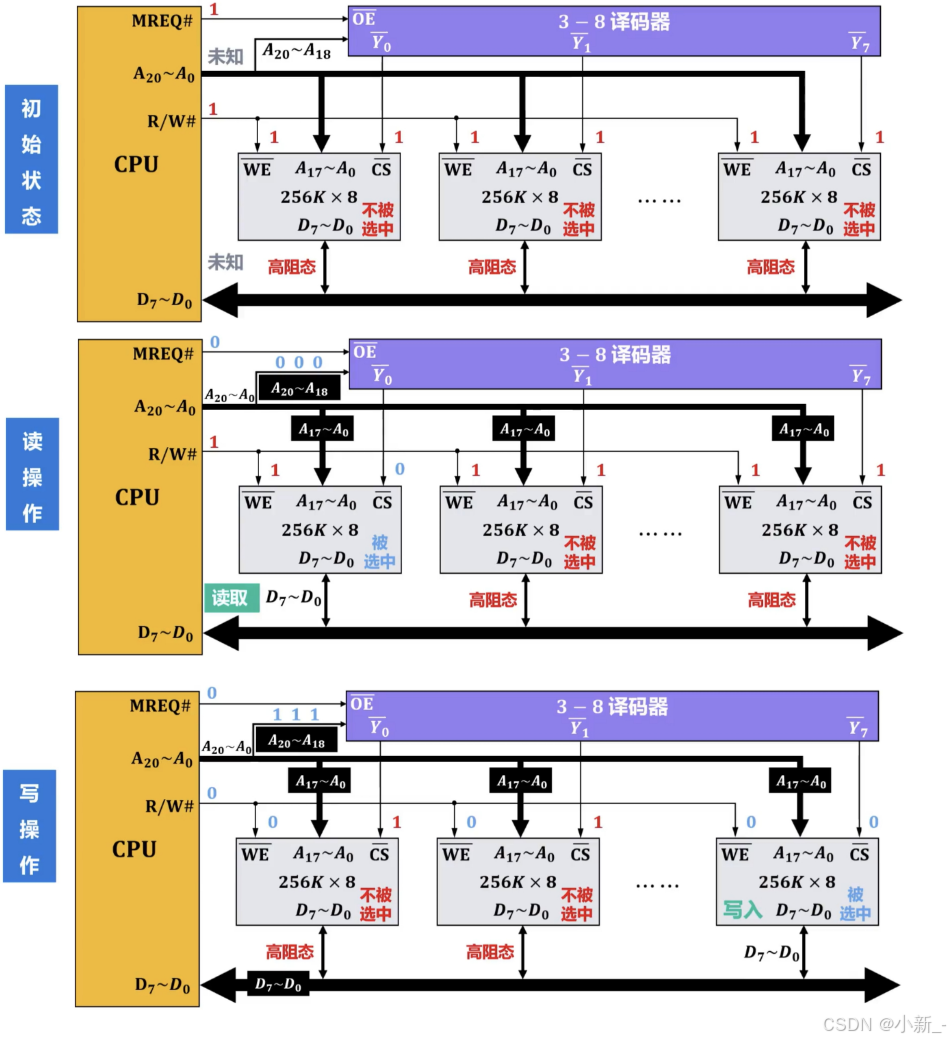

【举例】CPU的数据总线位宽为8位,地址总线位宽为21位,SRAM存储芯片的数据总线位宽为8位容量为256Kx8位,采用字扩展将8片这种SRAM存储芯片组成2Mx8位的存储器并与CPU连接

从图中我们可以知道,存储芯片的数据位宽等于存储器的数据位宽,因此不需要进行位扩展。而存储芯片的地址位宽为18,那么寻址空间位为2^18=256K小于存储器的地址寻址空间2^20=2M,因此需要进行字扩展。由于是八倍关系,因此需要8个芯片才能满足扩展需求。

本例的主存扩展与CPU链接示意图

这里的读写过程就不再赘述,可以参照上面的位扩展的读写过程进行学习。下面是读写过程的示意图。可以参照了解一下。

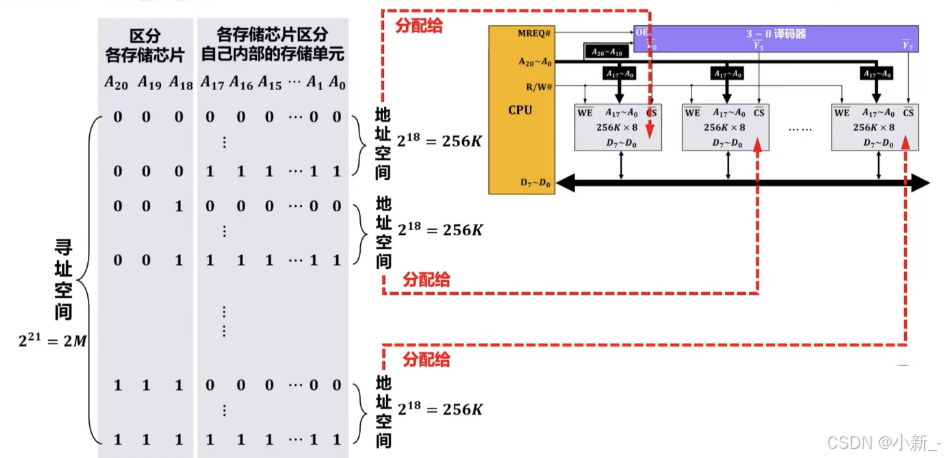

接下来,我们基于本例进一步分析字扩展中有关寻址问题。

我们发现,这与《计算机网络》这门课中的给IPV4划分子网的过程很相似

【总结】

(三)字位同时扩展

当存储芯片的数据位宽和存储容量均不能存储器的数据位宽和存储总容量要求时,采用字位同时扩展。

首先应该进行位扩展(满足数据位宽的要求),再进行字扩展(满足存储容量的要求)。

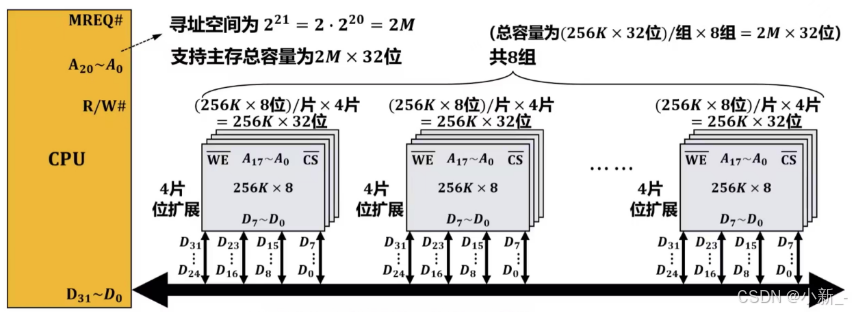

【举例】CPU的数据总线位宽为32位,地址总线位宽为21位,SRAM存储芯片的数据总线位宽为8位、容量为256Kx8位,采用字位同时扩展将32片这种SRAM存储芯片组成2Mx32位的存储器并与CPU连接、

分析:由题设我们知道存储芯片的数据位宽为8位小于存储器的数据位宽32位,所以我们需要4片存储芯片进行位扩展(一组)。存储芯片的地址位宽为18位小于存储器的地址位宽21位,因此我们需要进行字扩展,需要2^3=8组存储芯片进行字扩展。

本例的主存扩展与CPU链接示意图

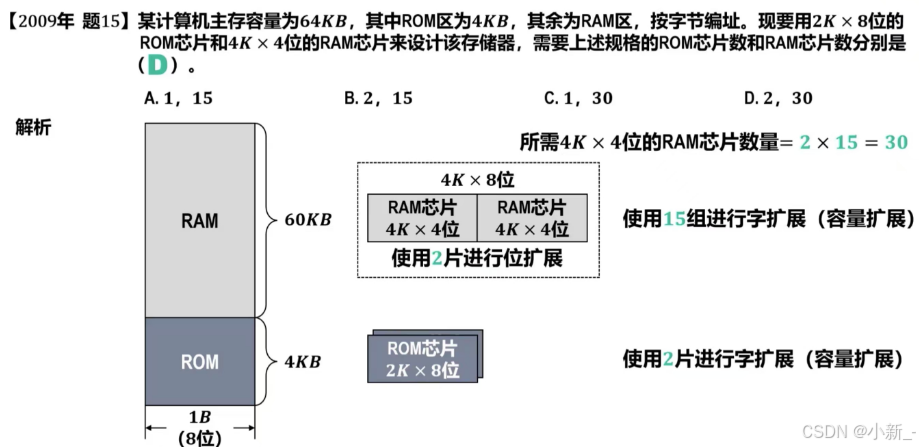

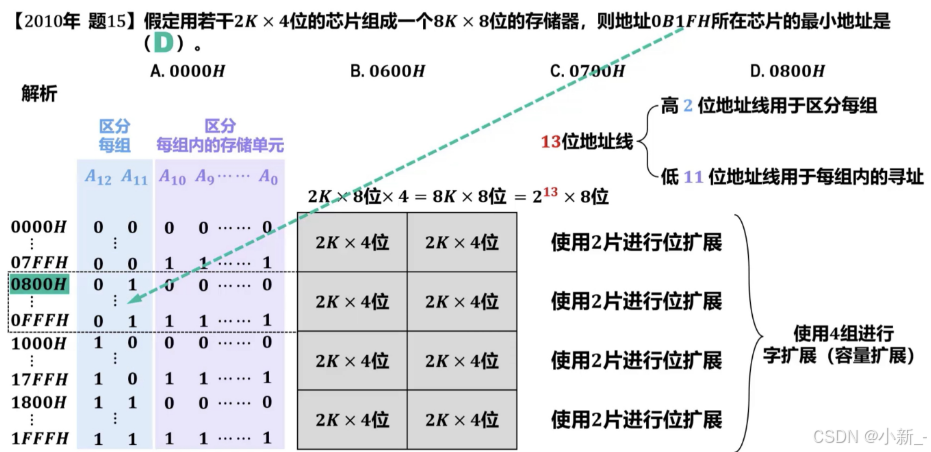

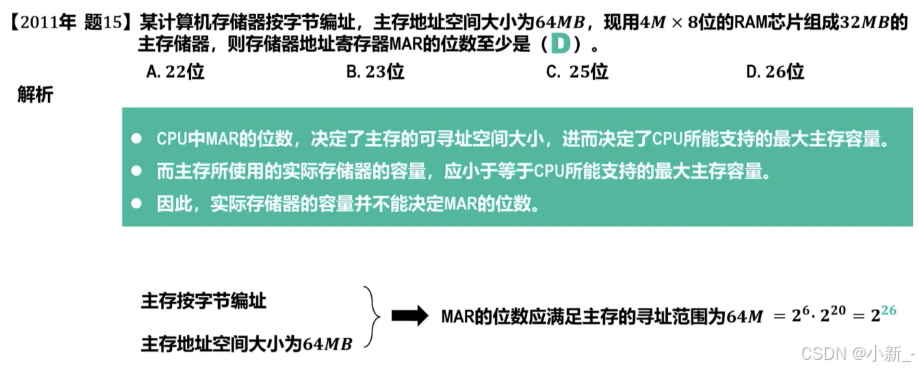

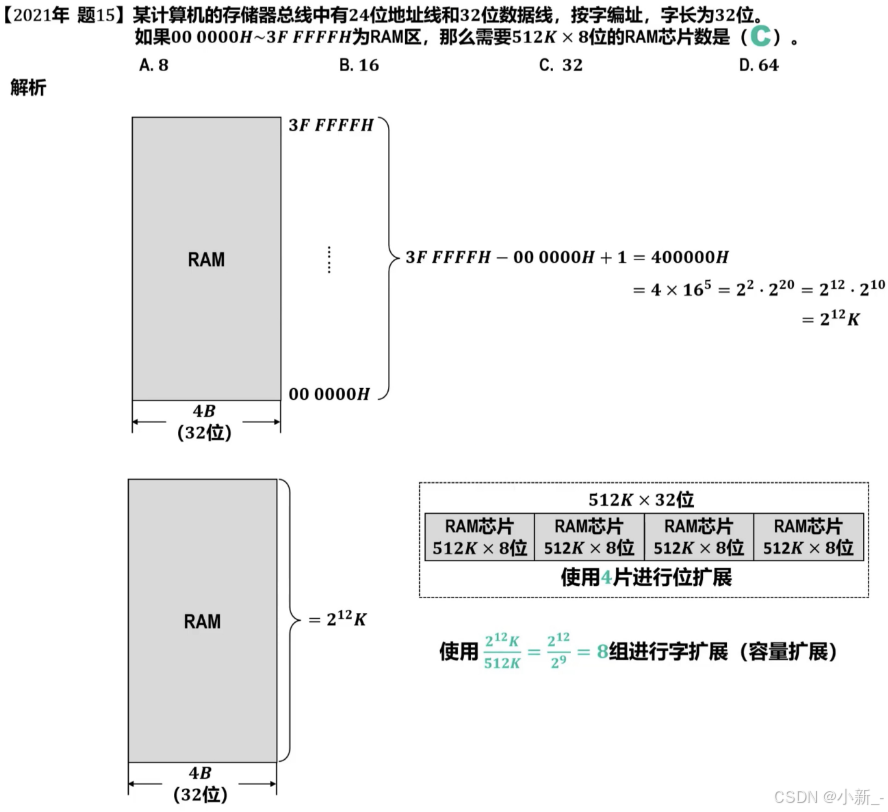

(四)主存与CPU的链接——习题

【复习】

【真题训练】

二、主存优化

随着计算机技术的发展,主存的存取速度已经成为提升计算机系统性能的瓶颈。因此,如何提高主存的存取速度,以缓解主存与CPU速度不匹配的问题,是值得研究的。

提高主存的存取速度的方法有:

- 使用高速元件来提高主存的访问速度。

- 通过存储器的并行工作来提高主存的访问速度。

- 双端口存储器

- 单体多字存储器

- 多体交叉存储器

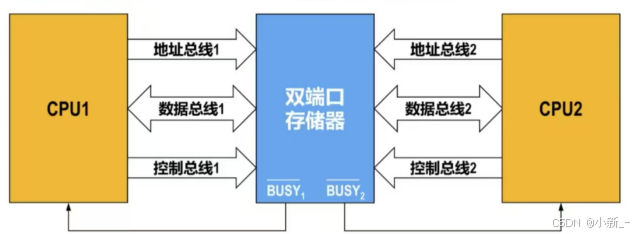

(一)双端口存储器

双端口存储器是一种特殊的存储器,具有两个独立的端口,可以同时进行读写操作。

工作原理:通过两套相互独立的控制电路、地址译码电路和读写电路,实现两个端口的并行访问。

当冲突发生时,由判断逻辑决定哪个端口优先进行读写操作,而将另一个端口的BUSY信号输出低电平,以延迟该端口对存储器的访问。高优先端口读写操作完成后,被延迟端口的BUSY信号输出高电平后,该端口就可以对存储器进行访问了。

由于冲突访问是不可避免的,因此双端口存储器的访问速度不可能提高1倍。

(二)单体多字存储器

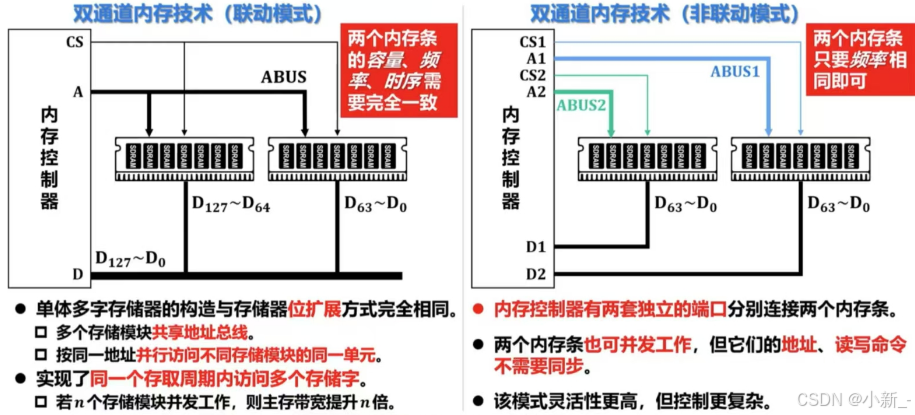

(三)多体交叉存储器

多体交叉存储器也由多个存储模块构成,这些模块的容量和存取速度相同,根据对多个模块编址方式的不同,又分为以下两种:

- 高位多体交叉

- 低位多体交叉

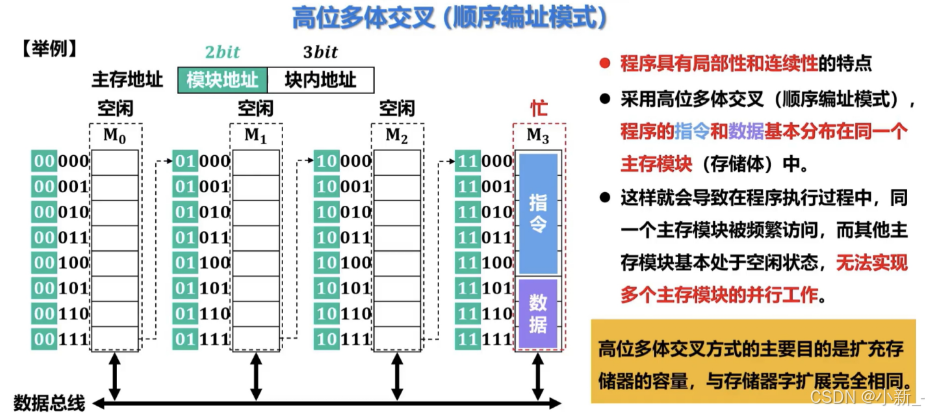

1、高位多体交叉(交叉编址模式)

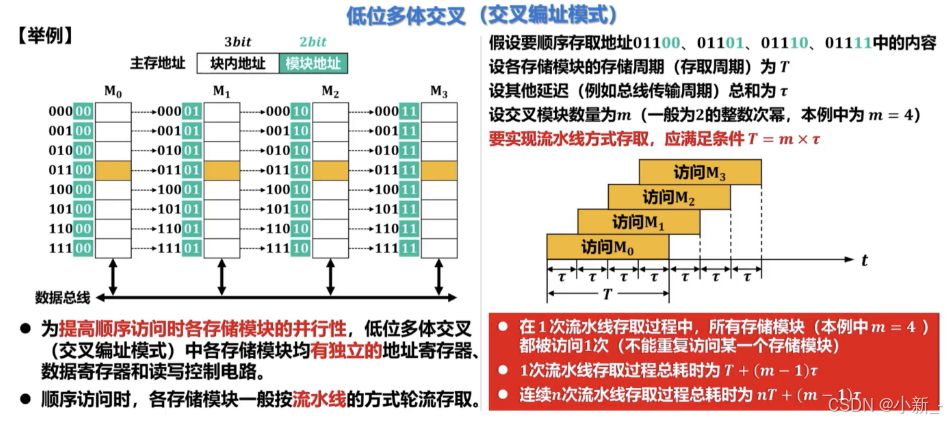

2、低位多体交叉(顺序编址模式)

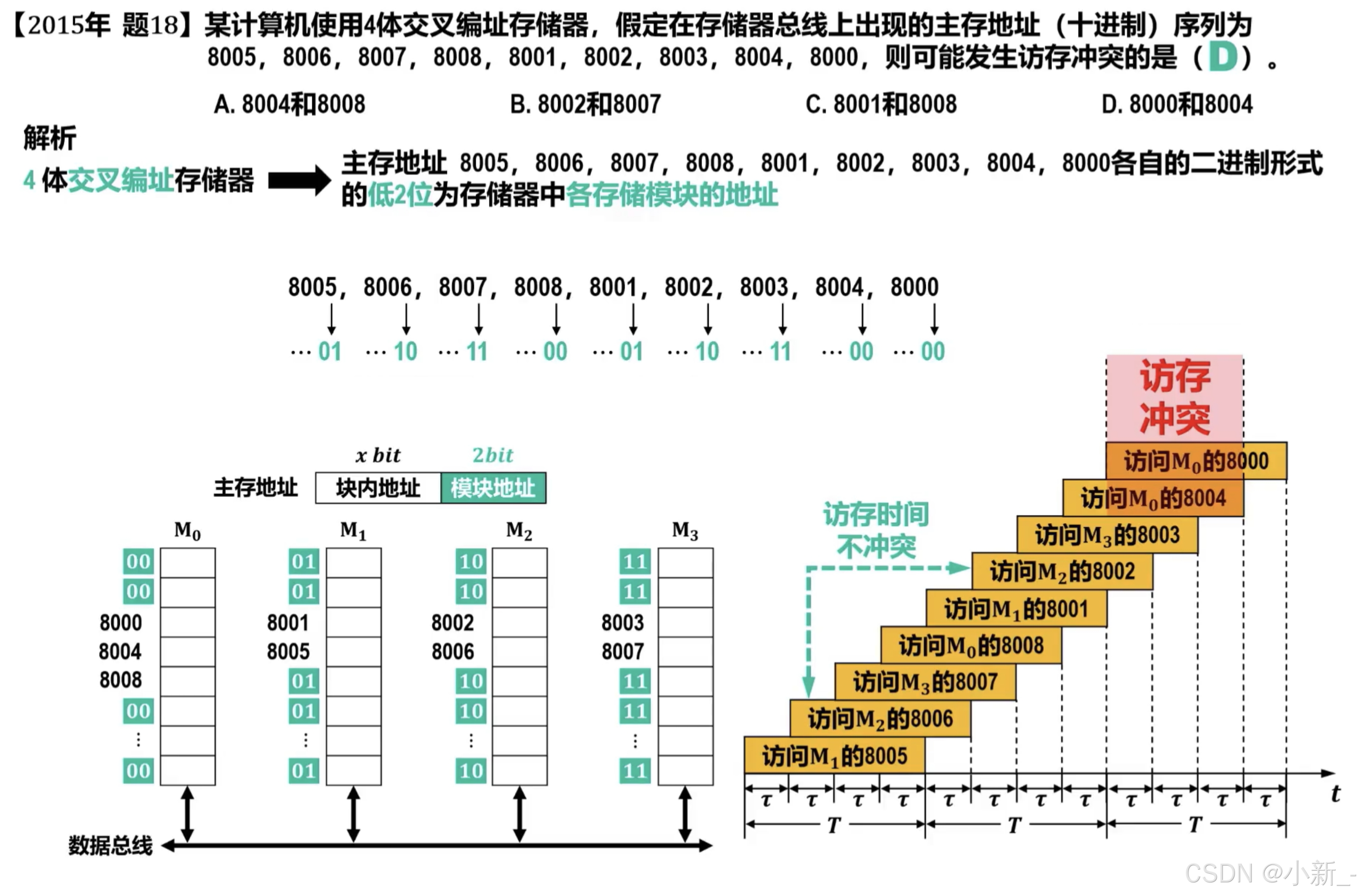

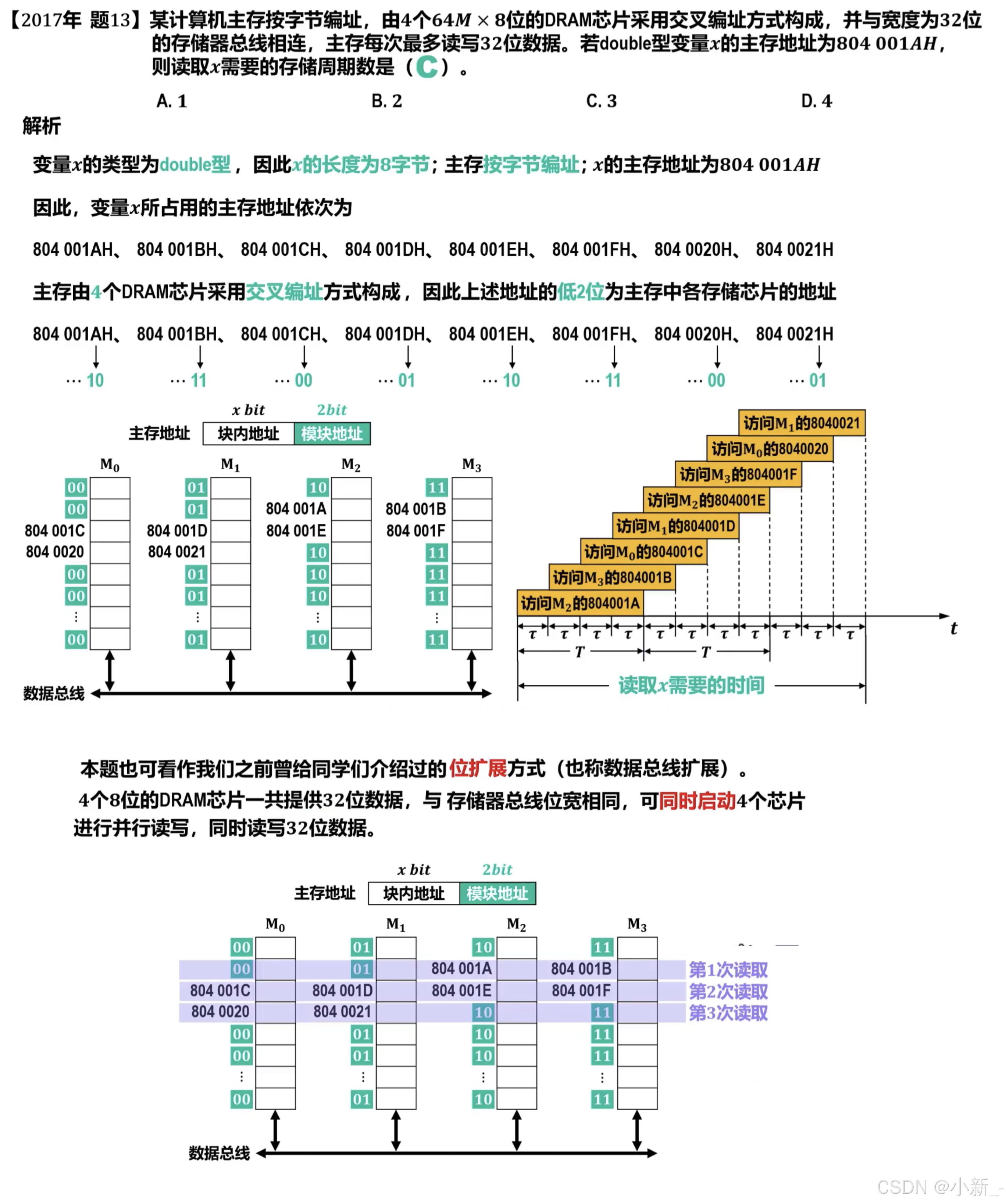

3、练习

最后,感谢大家的观看!

479

479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?