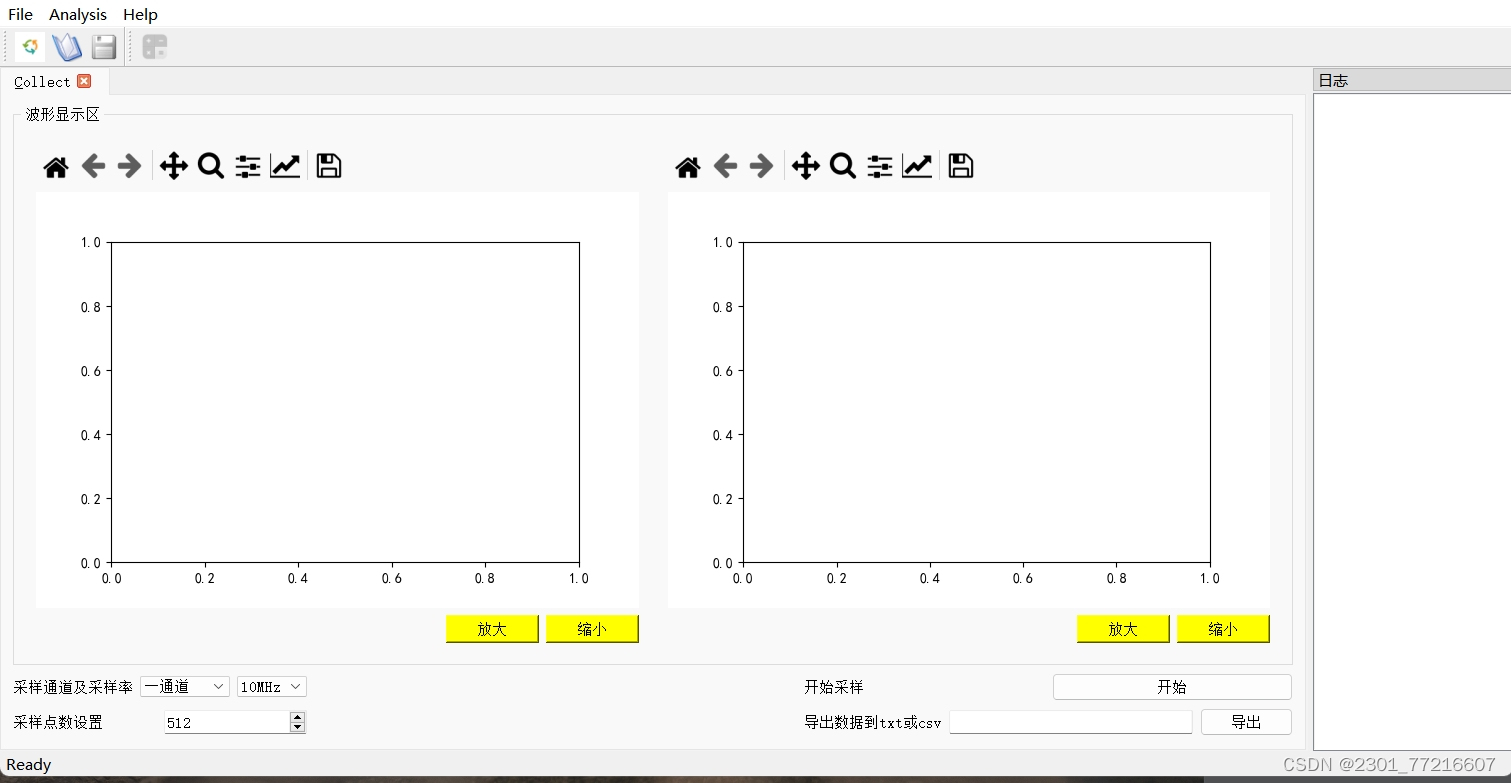

数据采集系统下位机与上位机代码。

下位机采用开发板来完成。

AD9226模数转换芯片,最大65MHz采样,12bit量化。

双通道采样。

上位机可以设置下位机的采样深度最大采集8K,采样率(1M,10M,20M,50M),可以保存波形,后续可以进行带通滤波与小波滤波。

可以配置为触发采样,当通道一电平大于2.5V采集通道二数据。

下位机与上位机以UDP协议通信。

下位机有两块主控芯片stm32与FPGA,二者通过FSMC总线通信。

提供Verilog,C,和上位机的python源代码。

上位机是pyqt5编写,python3.8。

ID:84100677860058750

1943

1943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?