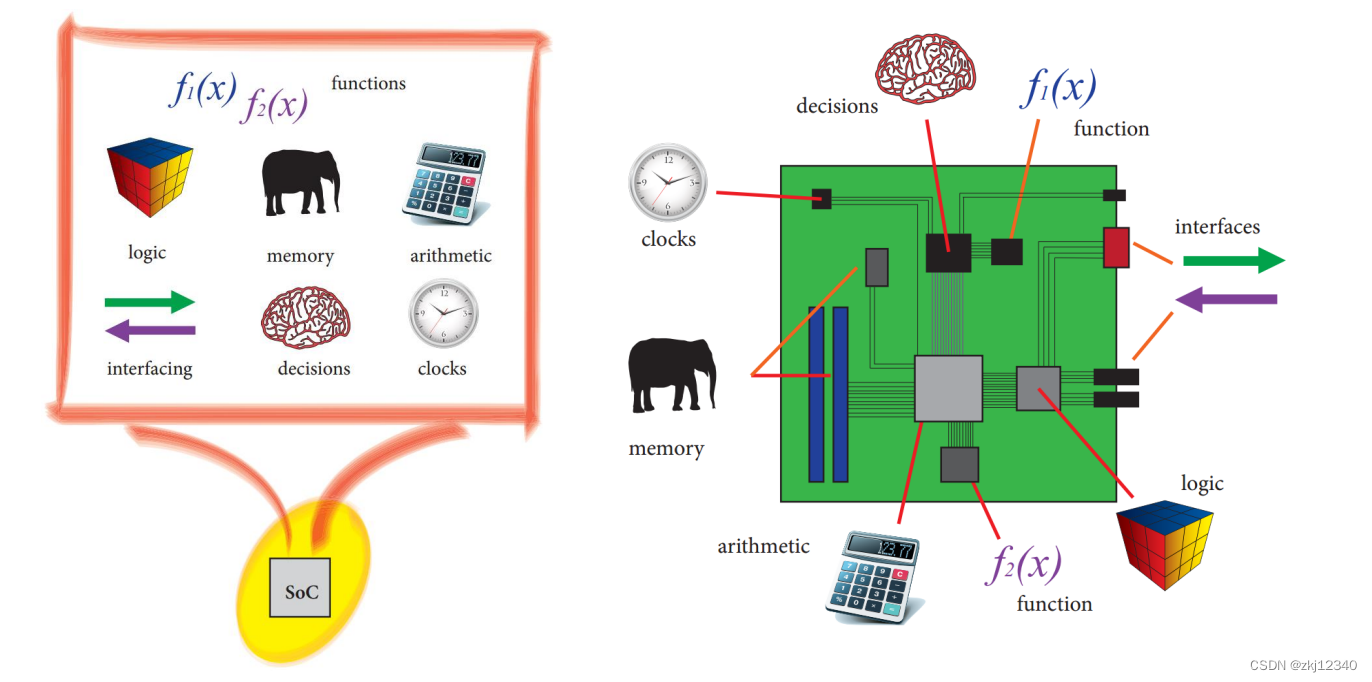

片上系统(SoC)和板级系统(SoB)

片上系统是所有存储器,处理器,接口,存储器,数模转换器等等都集成在一个芯片上,在单个硅芯片就可以实现整个系统的功能。

板级系统是CPU,接口,存储器,时钟等等都分布在电路板各个部分的电路系统设计,是需要印刷在PCB上进行走线的。

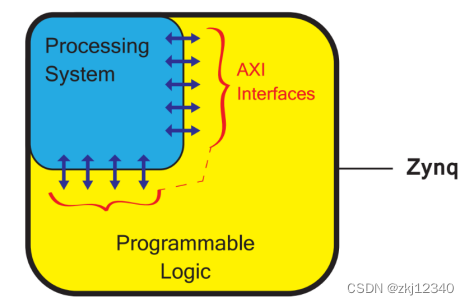

可编程的SoC叫做SoPC,FPGA就是这样的可编程配置的片上系统,ZYNQ则是在FPGA的基础上又加入了嵌入式系统部分。即ZYNQ=FPGA+ARM。

FPGA的优势

可编程逻辑器件 PLD 作为一种通用器件生产,但它的逻辑功能是由用户通过对器件进行编程来设 定的,PLD 的集成度很高,足以满足一般数字系统设计的需要。

这样就可以由设计人员自行编程 从而将一个数字系统“集成”在一片 PLD 上,做成“片上系统”(System on Chip,SoC),而不必去请芯片制造厂商设计和制作专用集成电路芯片了。

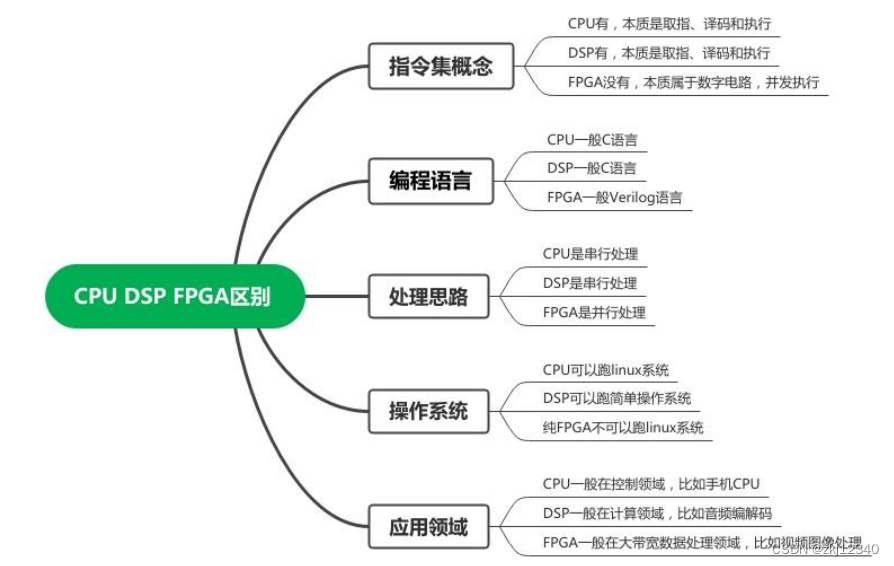

FPGA 打破了 CPU 顺序执行的思路,变为硬件并行处理,在每个时钟周期内可以完成更多的任务。FPGA 的行为是确定的,用作硬件加速器时没有 CPU 才有的时间片、线程或资源冲突的问题。它始终以完全相同 的速度执行一件事。因此 FPGA 具有高性能的特点。

应用领域

通信领域

在无线通信系统中,许多功能模块通常都需要大量的滤波运算,而这些滤波函数往往需要大 量的乘和累加操作。而通过 FPGA 来实现分布式的算术结构,就可以有效地实现这些乘和累加操作。

数字信号处理领域

数字信号处理方向:无线通信、软件无线电、高清影像编辑和处理等领域,对信号处理所需要的计算 量提出了极高的要求。FPGA 支持并行 计算,而且密度和性能都在不断提高,已经可以在很多领域替代传统的多 DSP 解决方案。例如,实现高清视频编码算法 H.264。

视频图像处理领域

FPGA 能进行实时流水线运算,能达到最高的实时性。因此在一些对实时性要求非常高的应用领域, 做图像处理基本只能用 FPGA。例如在一些分选设备中图像处理基本上用的都是 FPGA,因为在其中相机 从看到物料图像到给出执行指令之间的延时大概只有几毫秒,这就要求图像处理速度极快且延时固定,只 有 FPGA 进行的实时流水线运算才能满足这一要求。

高速接口设计领域

FPGA 可以用来做高速信号处理,一般如果 AD 采样率高,数据速率高,这时就需要 FPGA 对数据进行处理,比如对数据进行抽取滤波,降低数据速率,使信号容易处理、传输以及存储。

IC 验证领域

相比用仿真器,或者加速器等来跑仿 真,FPGA 的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。

人工智能领域

主要集中在前端和边缘侧

CPU DSP FPGA的区别

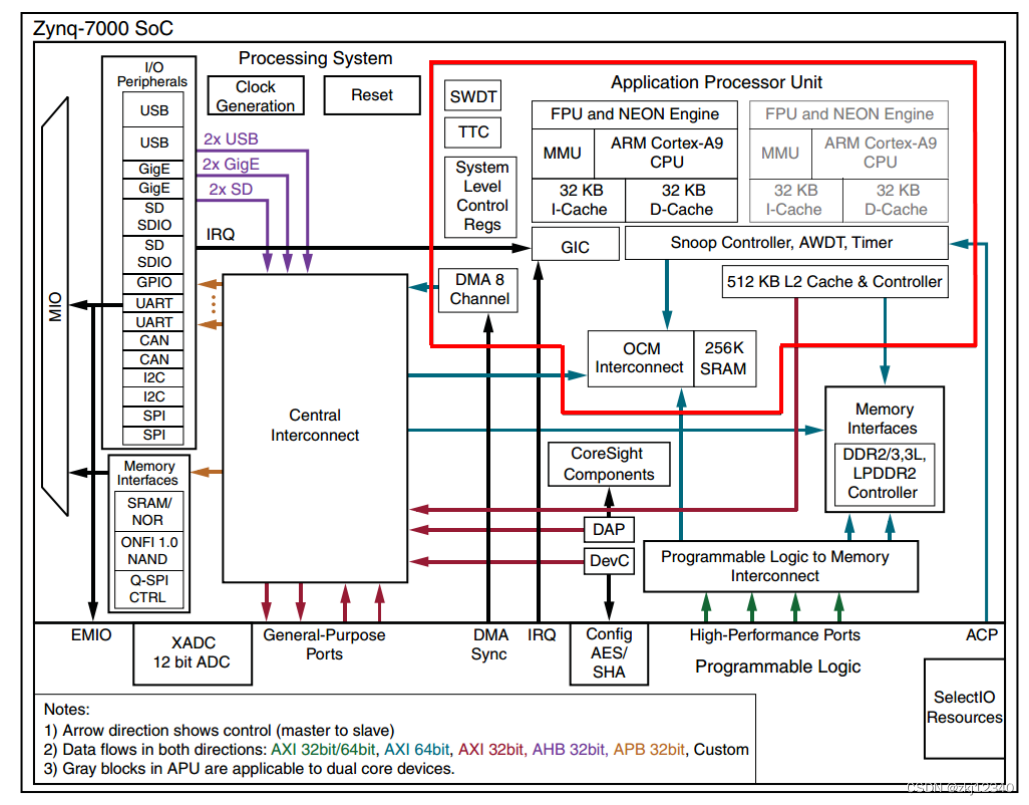

ZYNQ简介

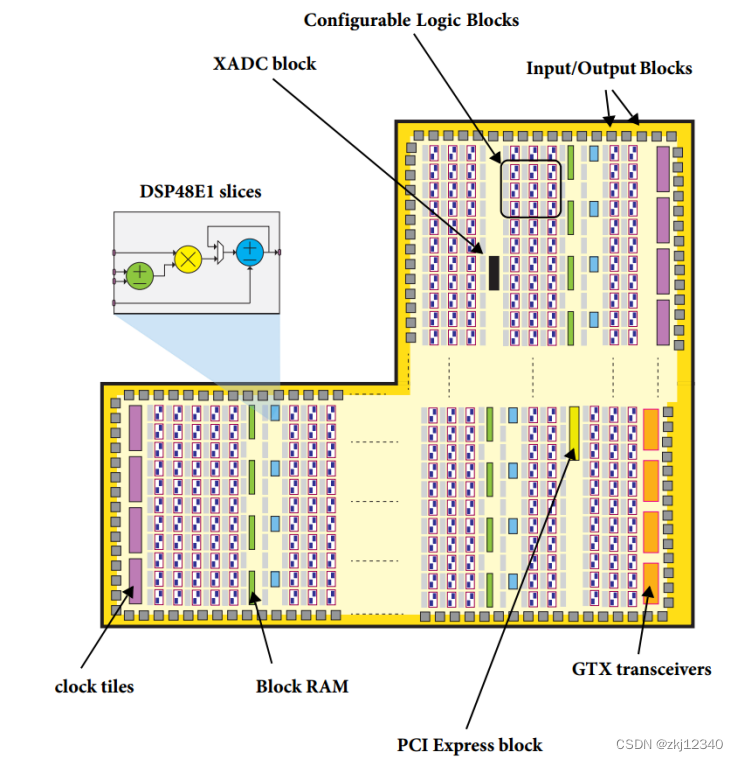

PL

可编程输入/输出单元

即可编程IO单元,可以设置引脚特性。Zynq 上的通用输入/输出功能(IOB)合起来被称作 SelectIO 资源,它们一般被组织成 50 个 IOB 一 组。每个 IOB 有一个焊盘,是与外部世界连接来做单个信号的输入或输出的。每个 IOB 还包含一个 IOSERDES 和 IODELAY 资源,可以做并行和串行数据的可编程转换。

基本可编程逻辑单元

FPGA 一般是基于 SRAM 工艺的,其基本可编程逻辑单元几乎都是由查找表(LUT,Look Up Table)和寄存器(Register)组成。Xilinx 7 系列 FPGA 内部查找表为 4 输入,查找表一般完成纯组合逻辑 功能。FPGA 内部寄存器结构相当灵活,可以配置为带同步/异步复位或置位,时钟使能的触发器,也可以 配置成锁存器,FPGA 依赖寄存器完成同步时序逻辑设计。

嵌入式块 RAM

目前大多数 FPGA 都有内嵌的块 RAM(Block RAM),FPGA 内部嵌入可编程 RAM 模块,大大地拓 展了 FPGA 的应用范围和使用灵活性。需要补充的一点是,除了块 RAM,还可以灵活地将 LUT 配置成 RAM、ROM、FIFO 等存储结构,这 种技术被称为分布式 RAM。

布线资源

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

第二类是长线资源,用以完成芯片 Bank 间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

IP 硬核单元

IP 硬核一般指的是通用程度较高的嵌入式功能模块,比如 PLL(Phase Locked Loop)、DLL(Delay Locked Loop)、DSP、CPU 等。随着 FPGA 的发展,这些模块被越来越多地嵌入到 FPGA 的内部,以满足不同场 合的需求。

PS

PL 和 PS 两部分的供电电路是独立的,这样 PS 或 PL 部分不被使用的话就可以被断电

APU

APU 主要是由两个 ARM 处理器核组成的,每个都关联了一些可计 算的单元

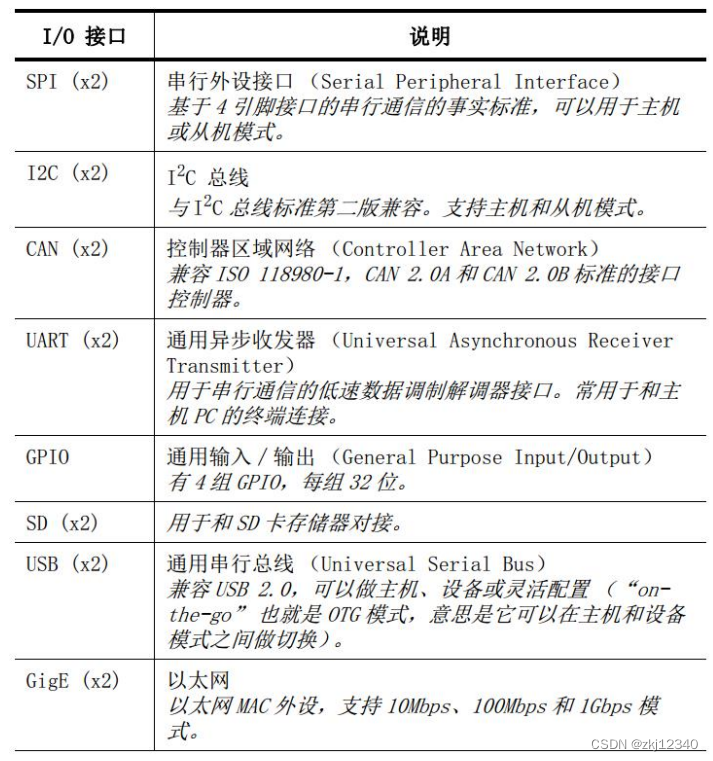

外部接口

通信接口

Zynq 芯片里含有嵌入在逻辑部分里的 GTX 收发器和高速通信接口块。这些是专用的硅片块(“硬 IP” 块),能支持一些标准接口,包括 PCI Express、串行 RapidIO、SCSI 和 SATA等。

存储器接口

包括一个动态存储器控制器和几个静态存储器接口模块。动态 存储器控制器可以用于 DDR3、DDR3L、DDR2 或 LPDDR2。静态存储器控制器支持一个 NAND 闪存接 口、一个 Quad-SPI 闪存接口、一个并行数据总线和并行 NOR 闪存接口。

片上存储器

片上存储器包括 256kB 的 RAM(OCM)和 128kB 的 ROM(BootROM),OCM 支持两个 64 位 AXI 从机接口端口,一个端口专用于通过 APU SCU 的 CPU/ACP 访问,而另一个是由 PS 和 PL 内其他所有的 总线主机所共享的。

AXI 接口

为设计带来了如减小 体积和功耗、降低设计风险、增加设计灵活性等诸多优点。在将不同工艺特征的处理器与 FPGA 融合在一 个芯片上之后,片内处理器与 FPGA 之间的互联通路就成了 Zynq 芯片设计的重中之重。这就要使用AXI协议进行通讯

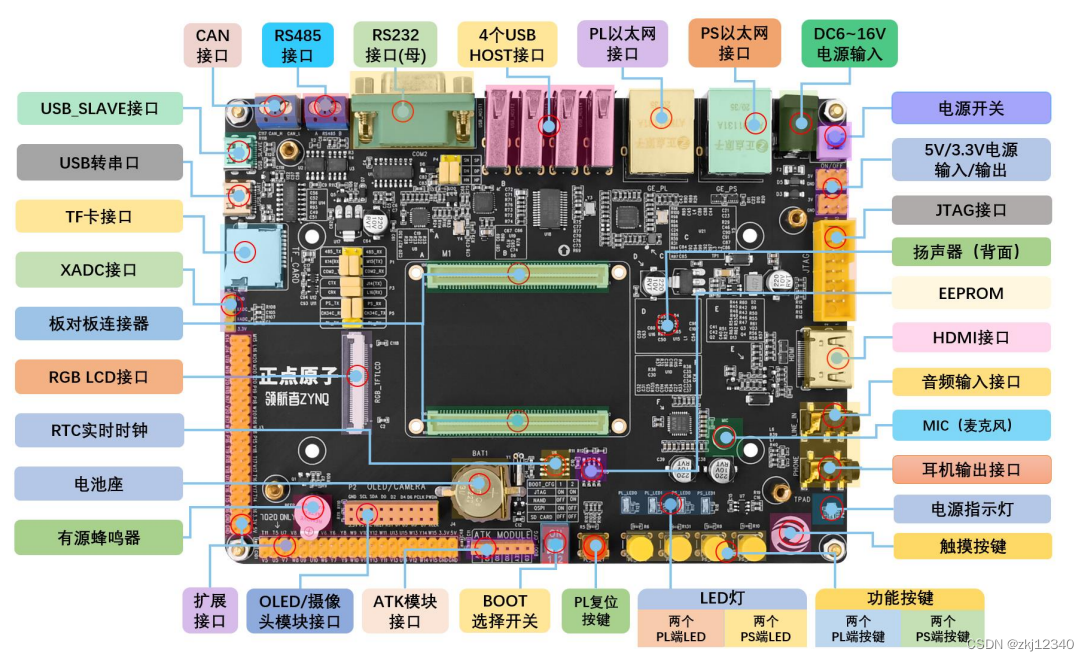

开发板资源

本文介绍了片上系统(SoC)和板级系统(SoB),重点讲解了FPGA的原理、优势以及在通信、数字信号处理、视频图像处理等领域的应用。同时提到了ZYNQ的独特结构,包括PLD、LUT、嵌入式块RAM等,并讨论了FPGA与CPU、DSP的区别,以及ZYNQ的PS、PL、APU和AXI接口等关键特性。

本文介绍了片上系统(SoC)和板级系统(SoB),重点讲解了FPGA的原理、优势以及在通信、数字信号处理、视频图像处理等领域的应用。同时提到了ZYNQ的独特结构,包括PLD、LUT、嵌入式块RAM等,并讨论了FPGA与CPU、DSP的区别,以及ZYNQ的PS、PL、APU和AXI接口等关键特性。

1504

1504

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?