The write data strobe signal is used by a manager to tell a subordinate which

bytes of the data bus are required. Write data strobes are useful for cache accesses for efficient

movement of sparse data arrays. In addition to using write data strobes, you can optimize data

transfers using unaligned start addresses.

The write channel has one strobe bit per byte on the data bus. These bits make the WSTRB signal.

A manager must ensure that the write strobes are set to 1 only for byte lanes that contain valid

data.

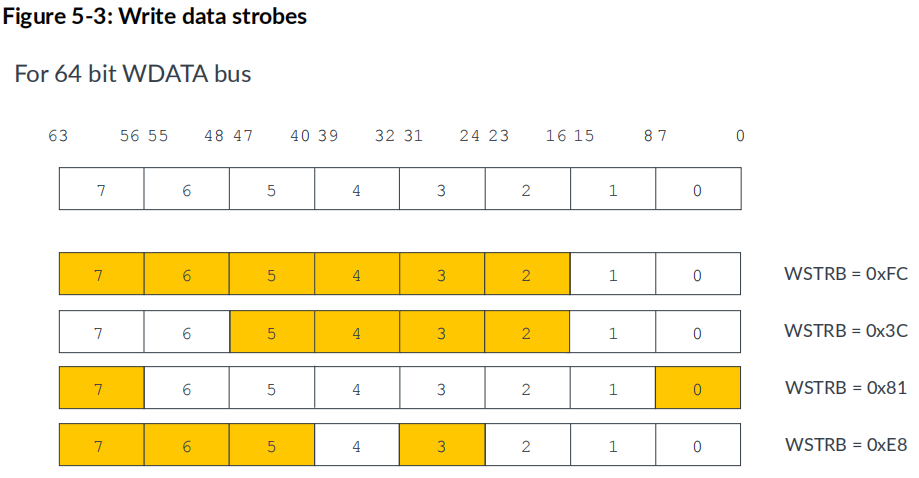

For example, consider a 64-bit write data bus. The WSTRB signal has 8 bits, one for each byte. The

following diagram shows how example WSTRB values specify which byte lanes are valid:

Looking at the first example, we suppose that the valid data are only in the top six significant bytes

of the data bus, from byte 7 to byte 2. This means that the manager has to control the WSTRB

signal with the hexadecimal value 0xFC.

Similarly, the remaining examples specify valid data bus byte lanes as follows:

• Valid data only in bytes 2, 3, 4, and 5 of the data bus requires a WSTRB signal value of 0x3C.

• Valid data only in bytes 0 and 7 of the data bus requires a WSTRB signal value of 0x81.

• Valid data only in bytes 3, 5, 6, and 7 of the data bus requires a WSTRB signal value of 0xE8.

Byte lane strobes offer efficient movement of sparse data arrays. Using this method, write

transactions can be early terminated by setting the remaining transfer byte lane strobes to 0,

although the remaining transfers must still be completed. The WSTRB signal can also change

between transfers in a transaction.

There is no equivalent signal for the read channel. This is because the manager indicates the

transfer required and can mask out any unwanted bytes received from the subordinate.

Write data strobes

最新推荐文章于 2025-10-29 16:09:31 发布

788

788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?