The AXI4 protocol introduces extra signals to support the quality of service (QoS).

Quality of service allows you to prioritize transactions allowing you to improve system

performance, by ensuring that more important transactions are dealt with higher priority.

There are two quality of service signals:

• AWQOS is sent on the Write Address channel for each write transaction.

• ARQOS is sent on the Read Address channel for each read transaction.

Both signals are 4 bits wide, where the value 0x0 indicates the lowest priority, and the value 0xF

indicates the highest priority.

The default system-level implementation of quality of service is that any component with a choice

of more than one transaction processes the transaction with the higher QoS value first.

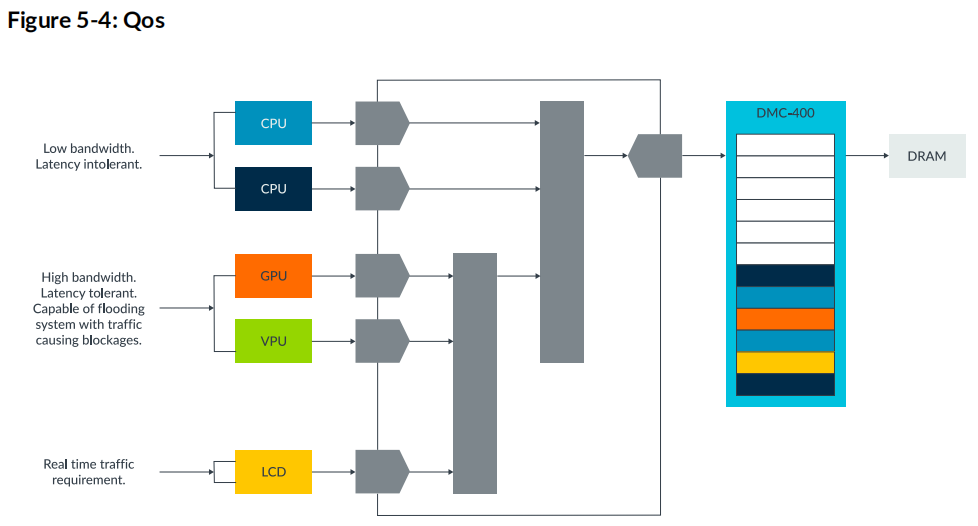

The following diagram shows an example system with a Direct Memory Controller (DMC),

specifically the DMC-400. This controller manages transactions to DRAM:

In practice, some elements, like the CPU, require memory accesses that are far more important than

those of other components, like the GPU or the VPU.

When appropriate QoS values are assigned to transactions, the interconnect can arbitrate higher

priority transaction ahead of lower priority transactions and the DMC reorders transactions to

ensure that the correct priority is given.

Quality of service

最新推荐文章于 2025-10-29 16:09:31 发布

2004

2004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?