内容基于中国大学MOOC的2023考研计算机组成原理课程所做的笔记。

感谢LY,他帮我做了一部分笔记。由于听的时间不一样,第四章前的内容看起来可能稍显啰嗦,后面会记得简略一些。

西电的计算机组织与体系结构课讲法和王道考研的课不太一样,要应付校内考试建议还是跟着老师学比较好。以下是20年西电计科院车向泉老师这门课的录播下载链接(请勿将录像上传到B站等网站!!):

链接:https://pan.baidu.com/s/1bFs3ajhy8ZcbHopS9izGsw

提取码:fdez

期中考试占20分,一般只考前两章内容,期末考试占60分,一般前两章内容不考,考察内容一般考前的复习课都会讲清楚,请务必认真听复习课。

其他各章节的链接如下:

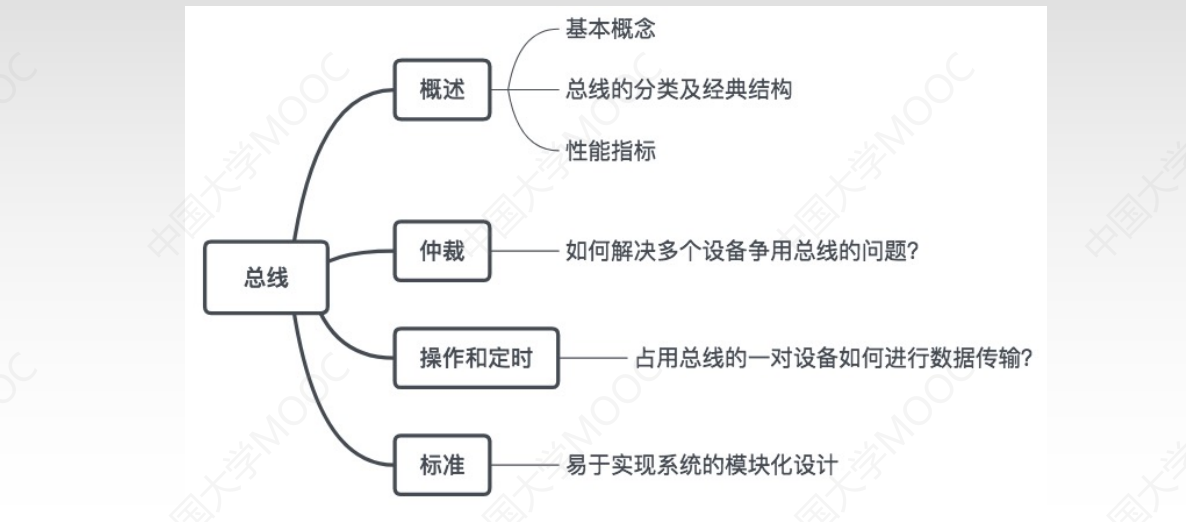

总线

总线概述

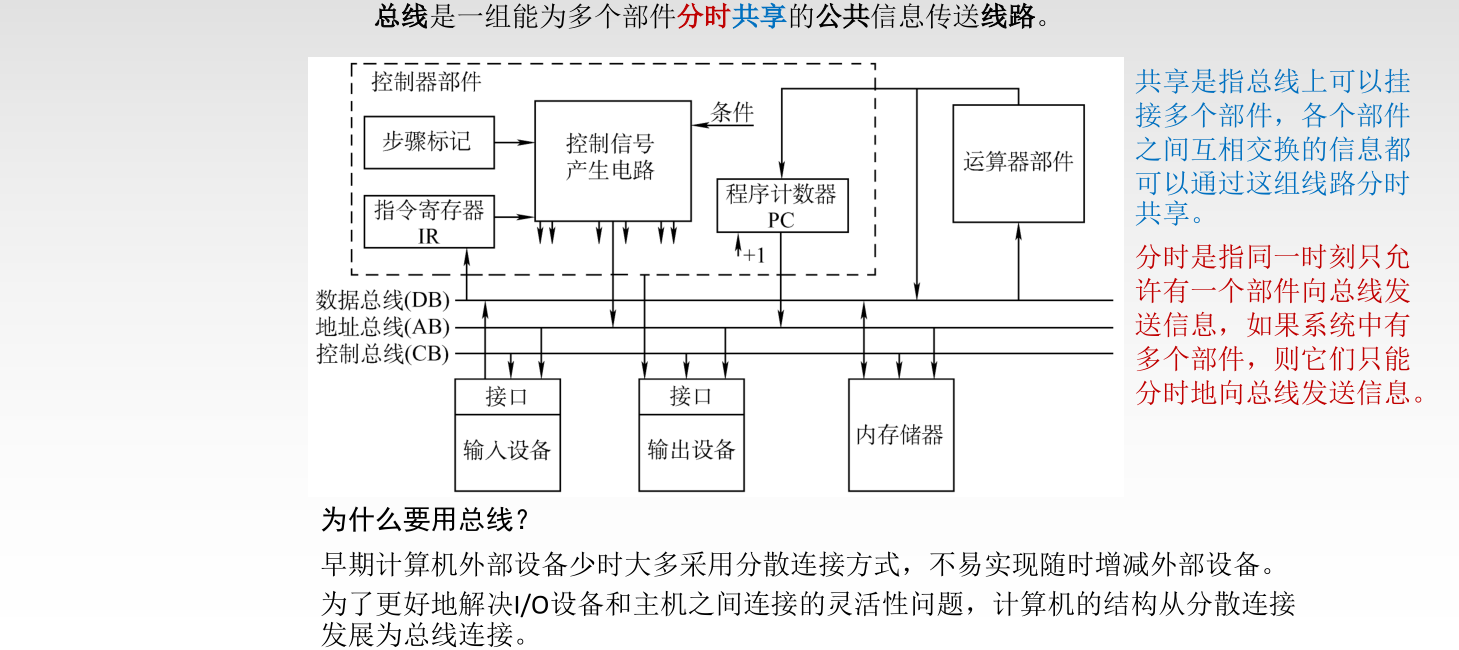

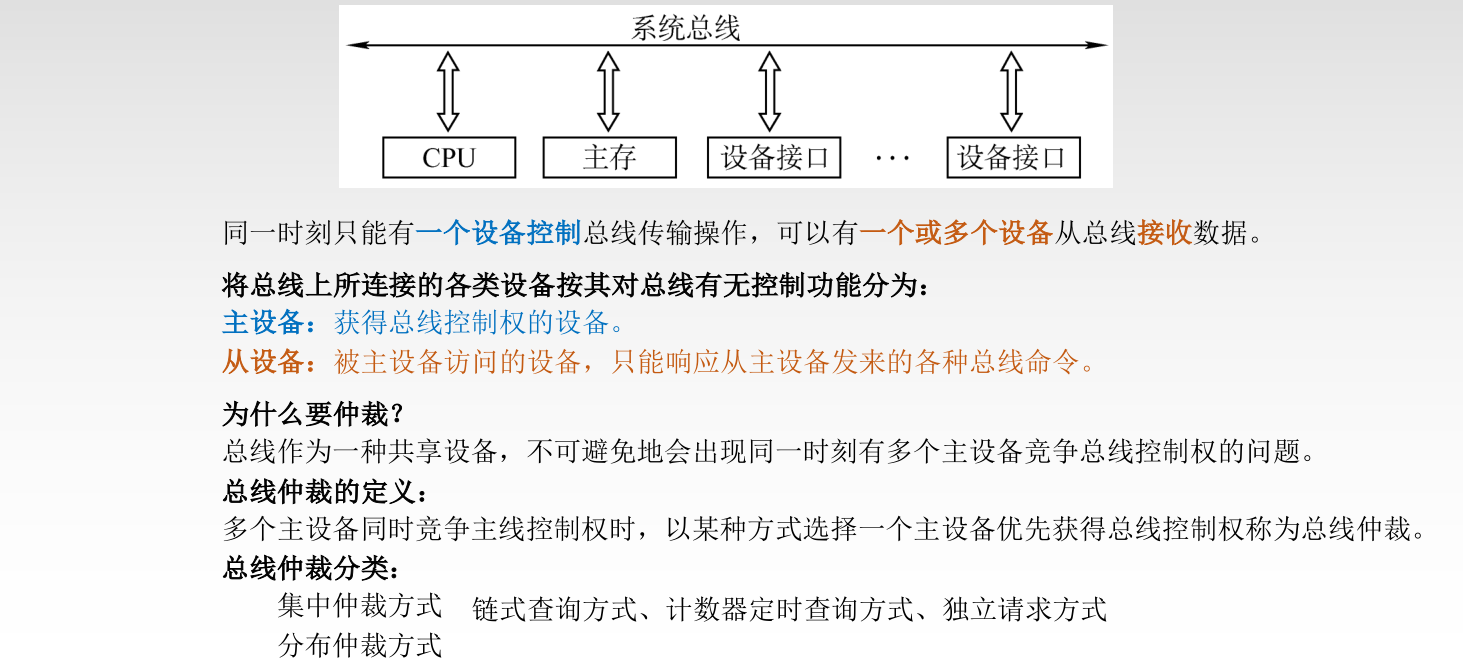

总线简图

总线的物理实现

主板上一根根细细的线都是用光刻机刻的,这些线其实就是总线。主板上会留下一个个插槽插CPU、内存条等等。插槽里面的线路已经和总线进行了连接,只要把CPU和内存条插上,两者就可以通过主板上的总线进行数据交互

这种总线的设计思想可以让电脑方便地扩充一些硬件部件

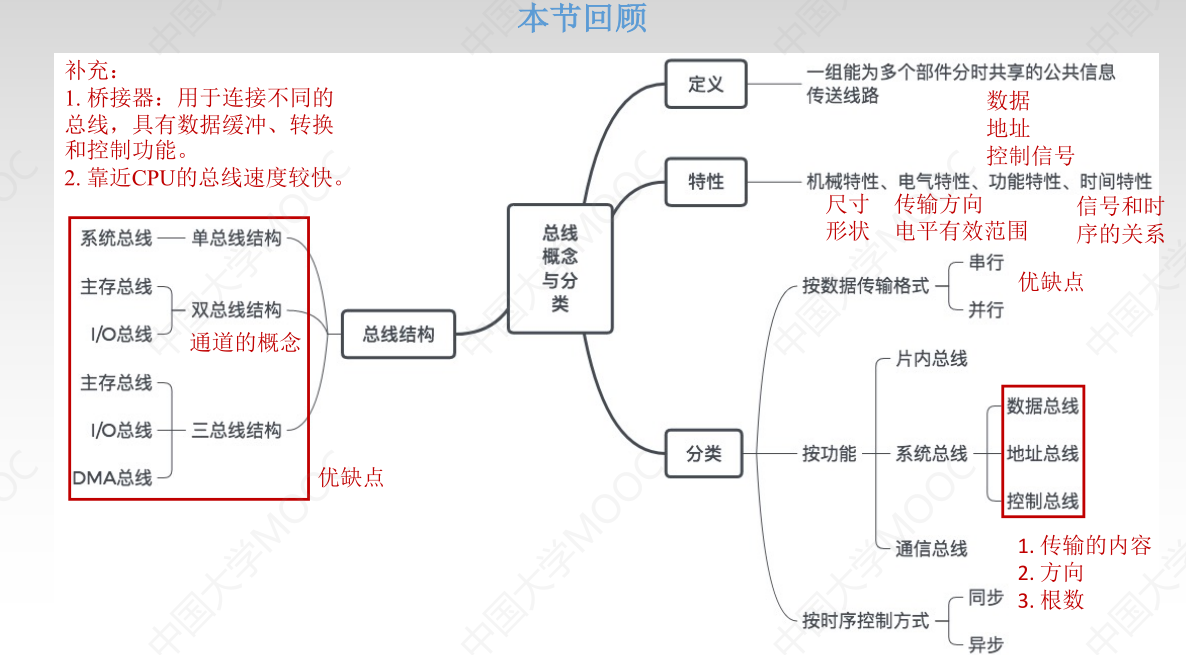

总线的定义

分散连接 —— 建立一条专门的数据传送线路

总线的特性

总线的分类

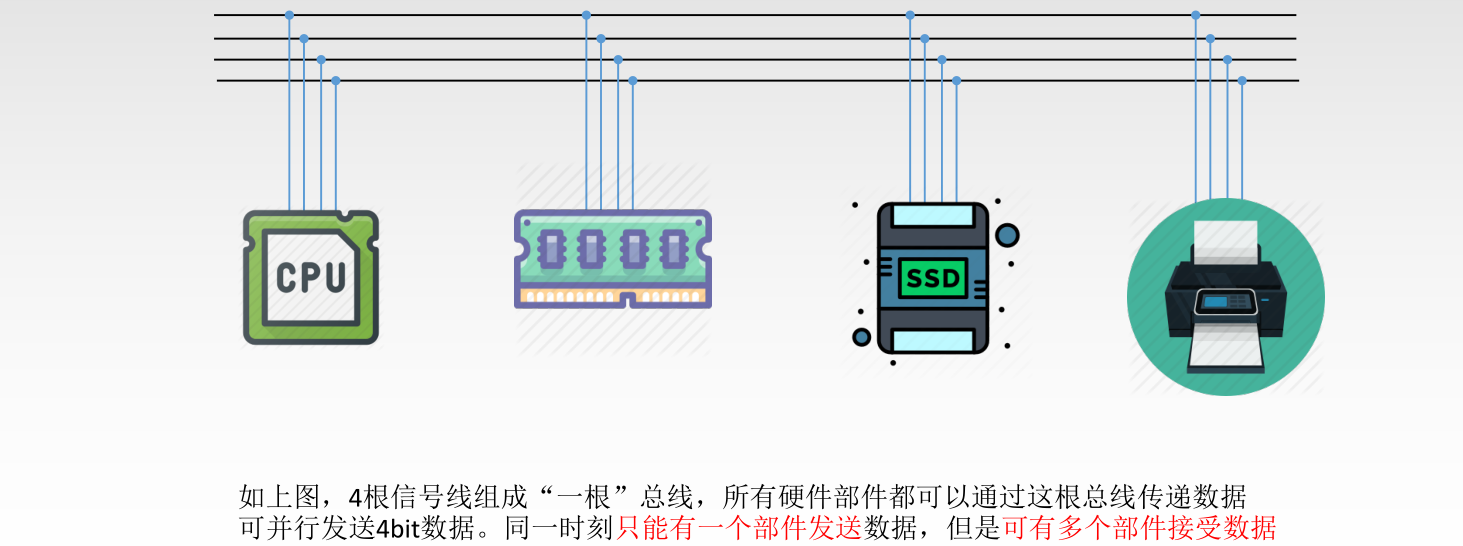

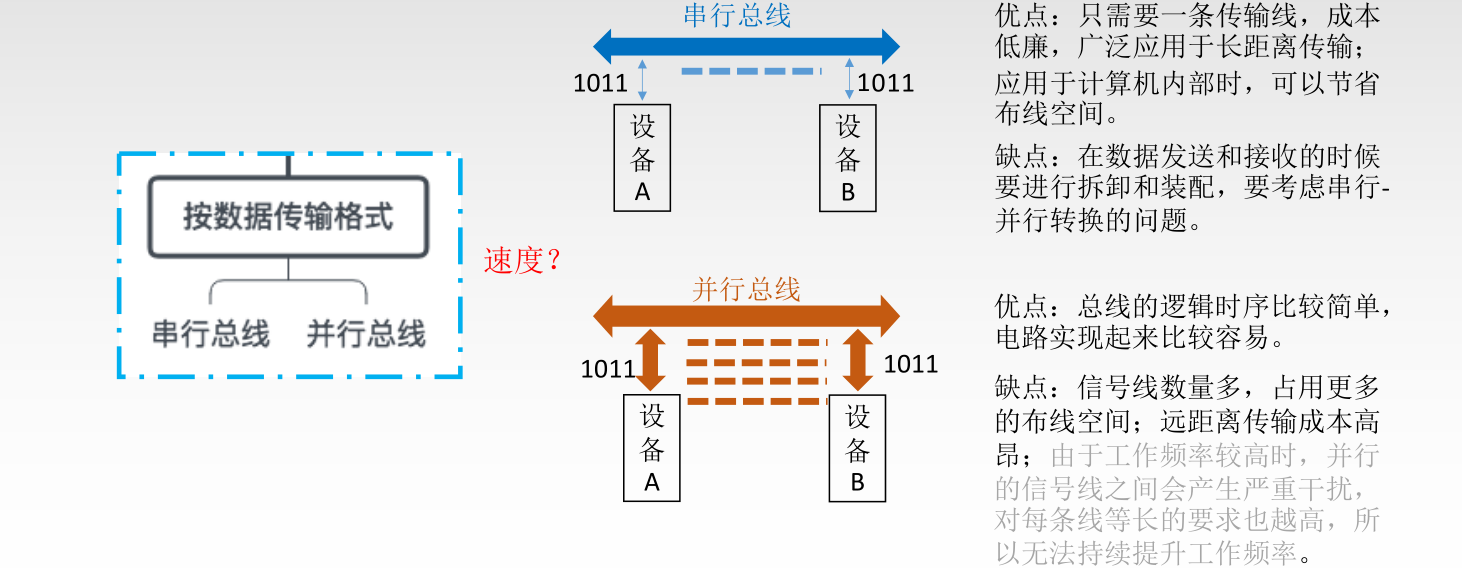

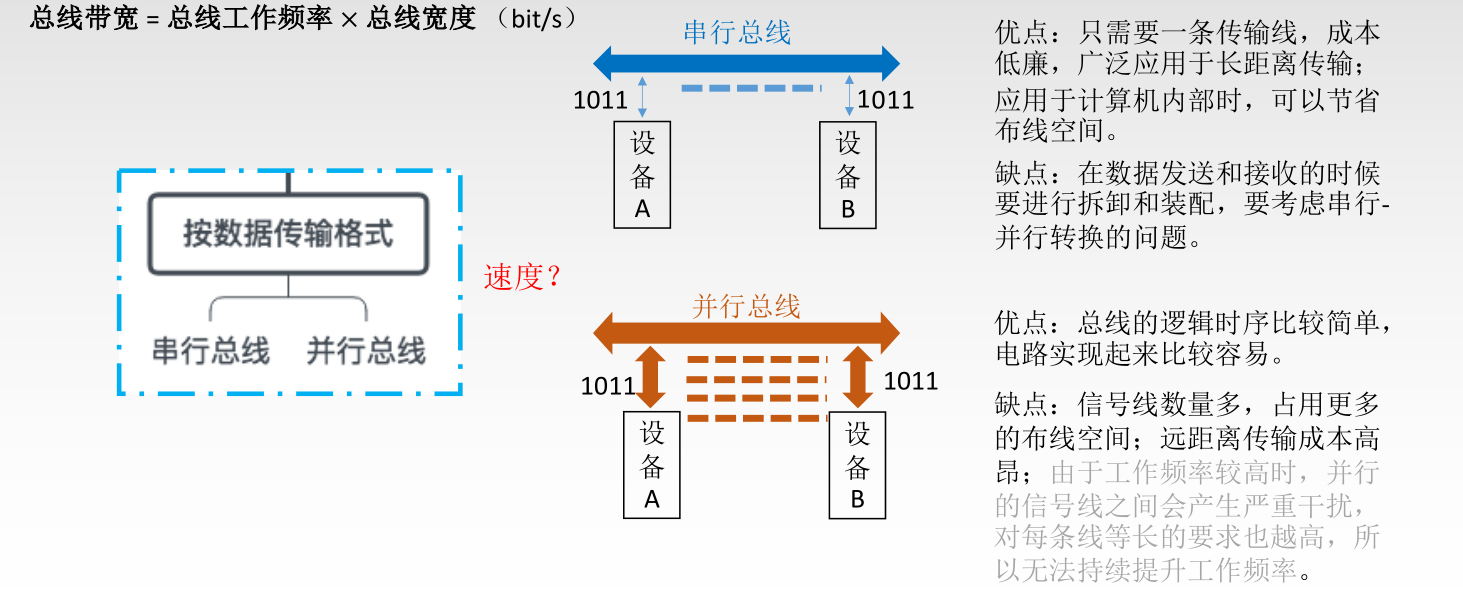

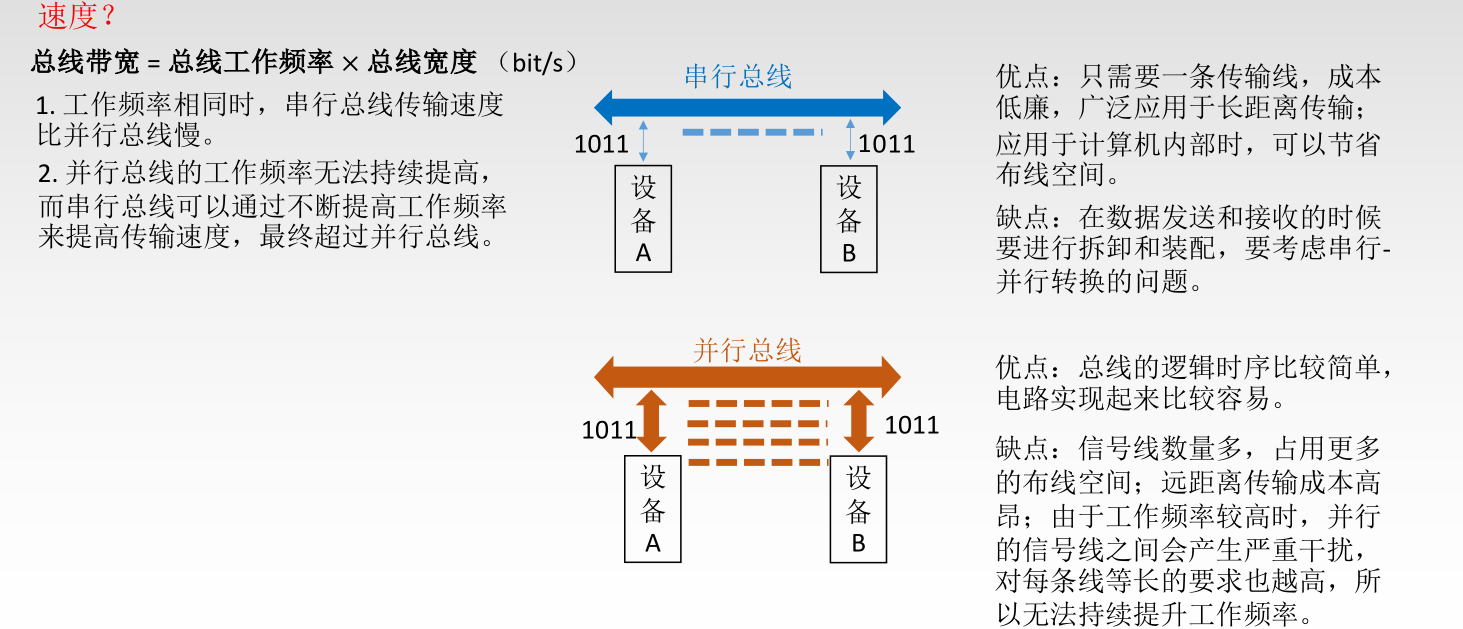

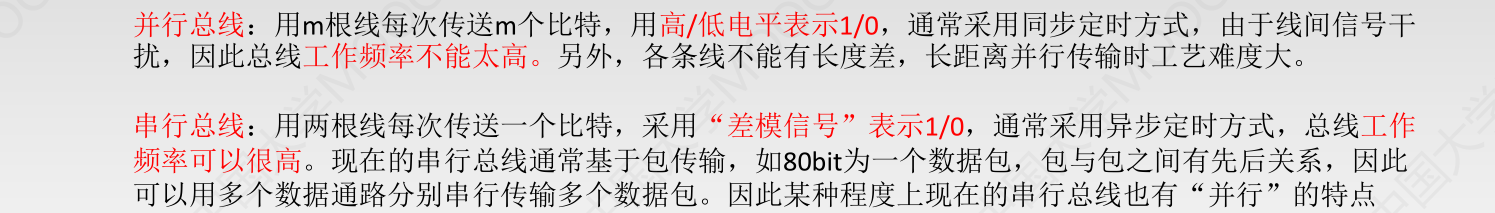

串行总线与并行总线

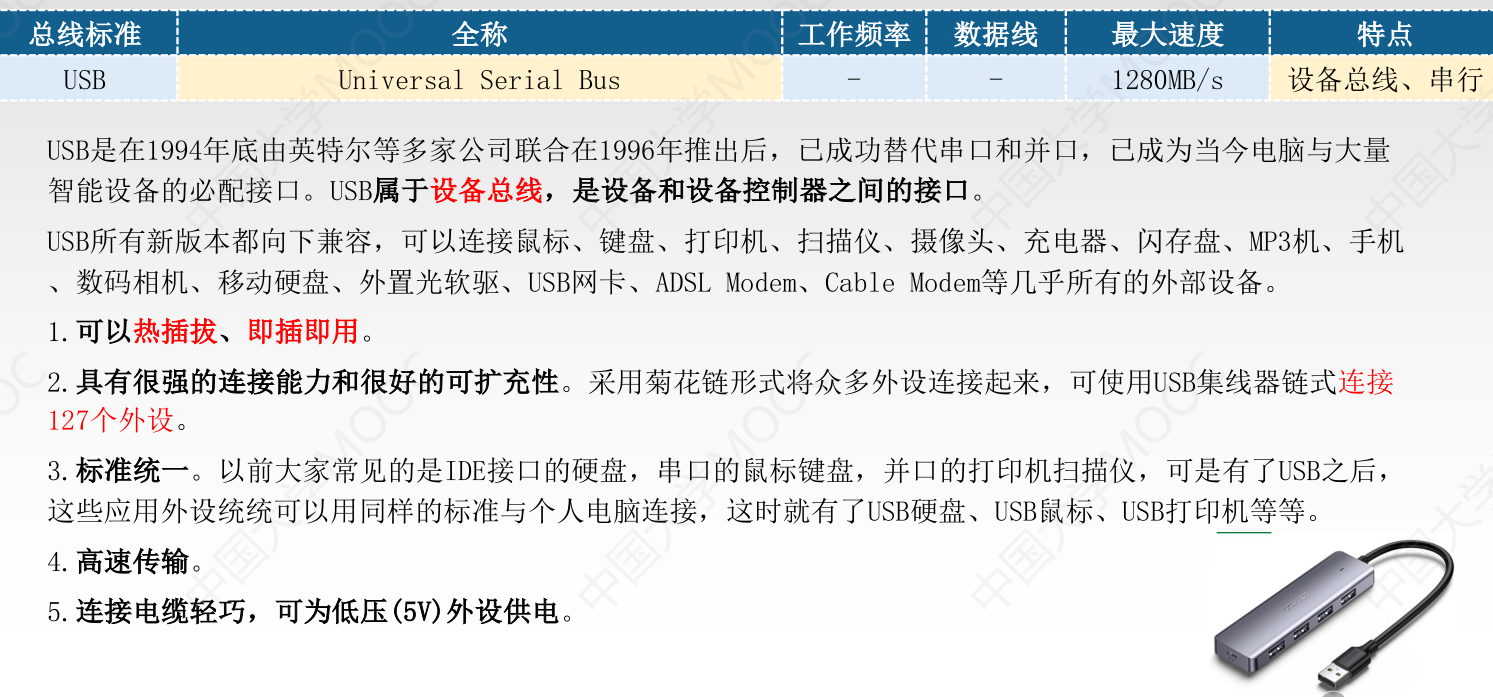

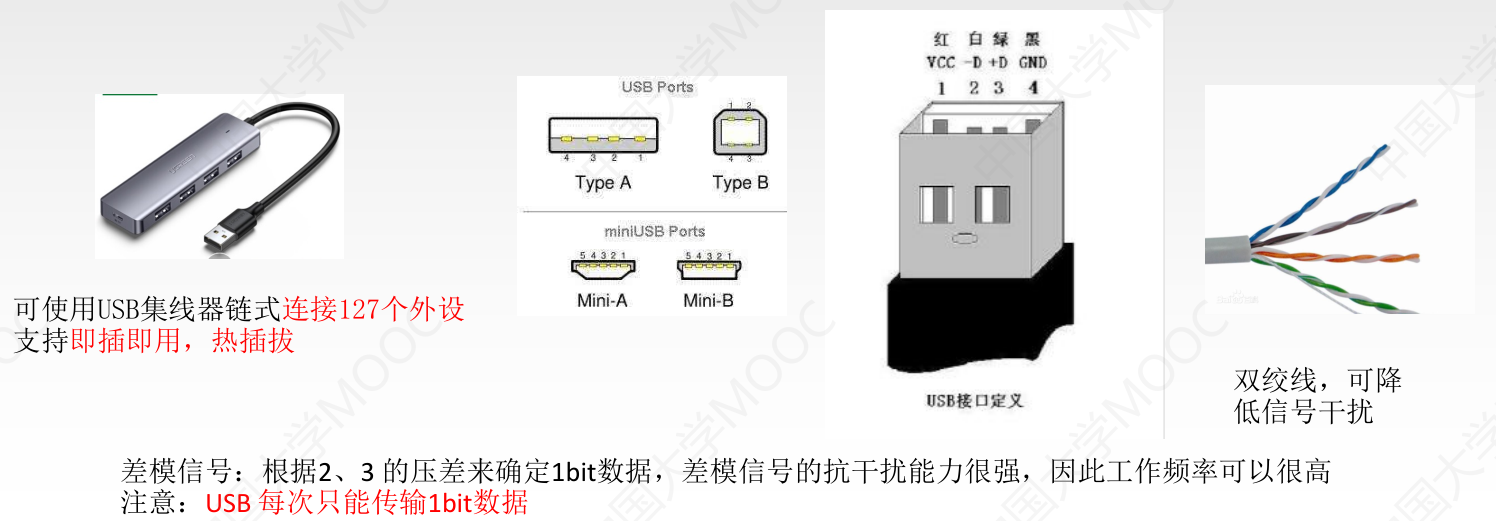

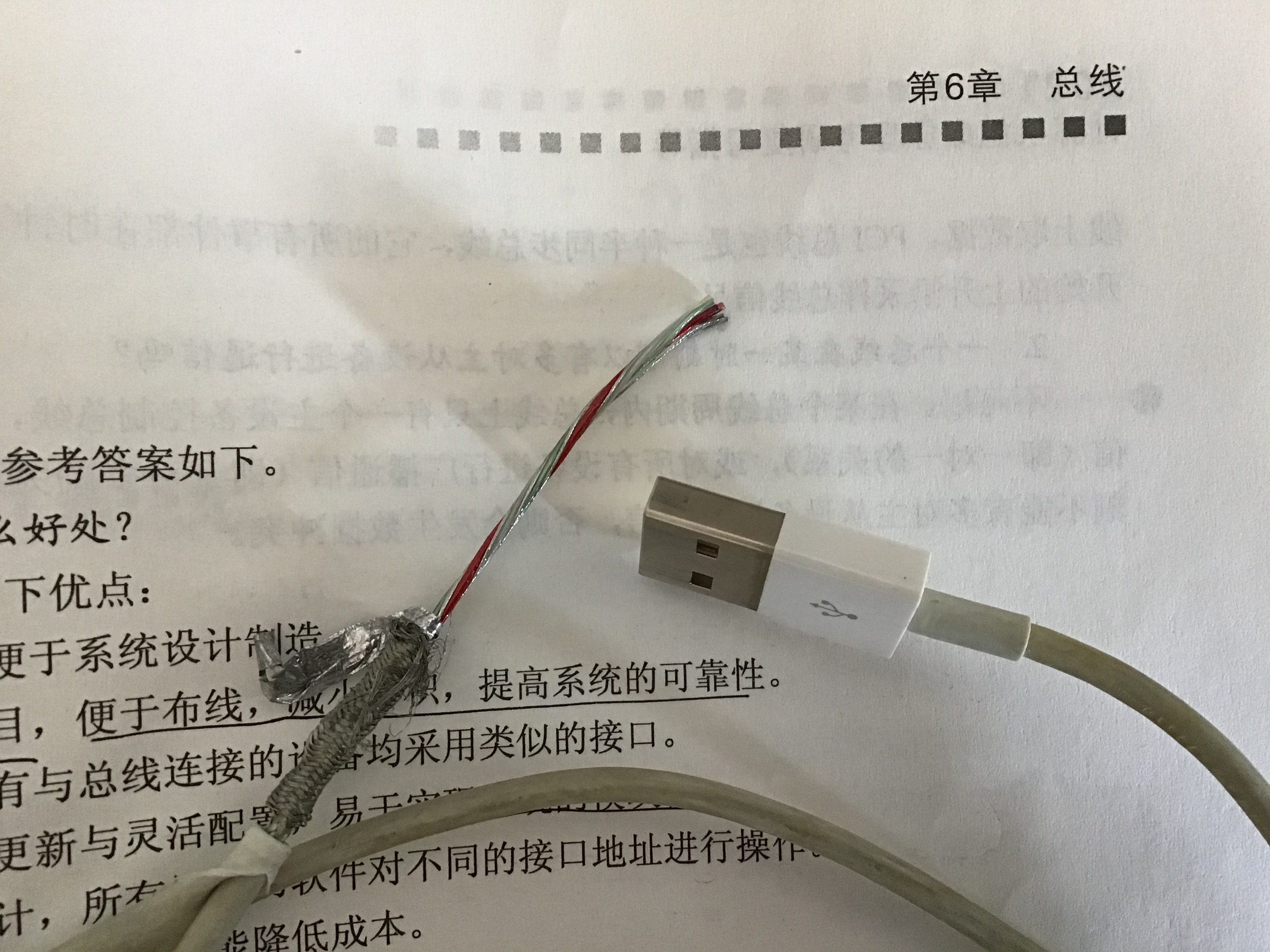

CPU和主存之间的数据总线就是并行总线。USB就是串行总线

只有一根传输线的串行总线抗干扰能力很强

通常发送一组有意义的二进制信息,肯定以一个或多个字节为单位,由于每次只能传递一个比特,因此就存在把一个完整的信息包拆卸和装配的过程

用USB给电脑主机发送数据都是一个个比特发送的,但是CPU不可能一个个比特地接收这些数据。所以串行发出的数据必须经过转换之后用并行的方式送给CPU

因为并行总线发送数据时发送频率有上限,并行总线并不一定比串行总线快

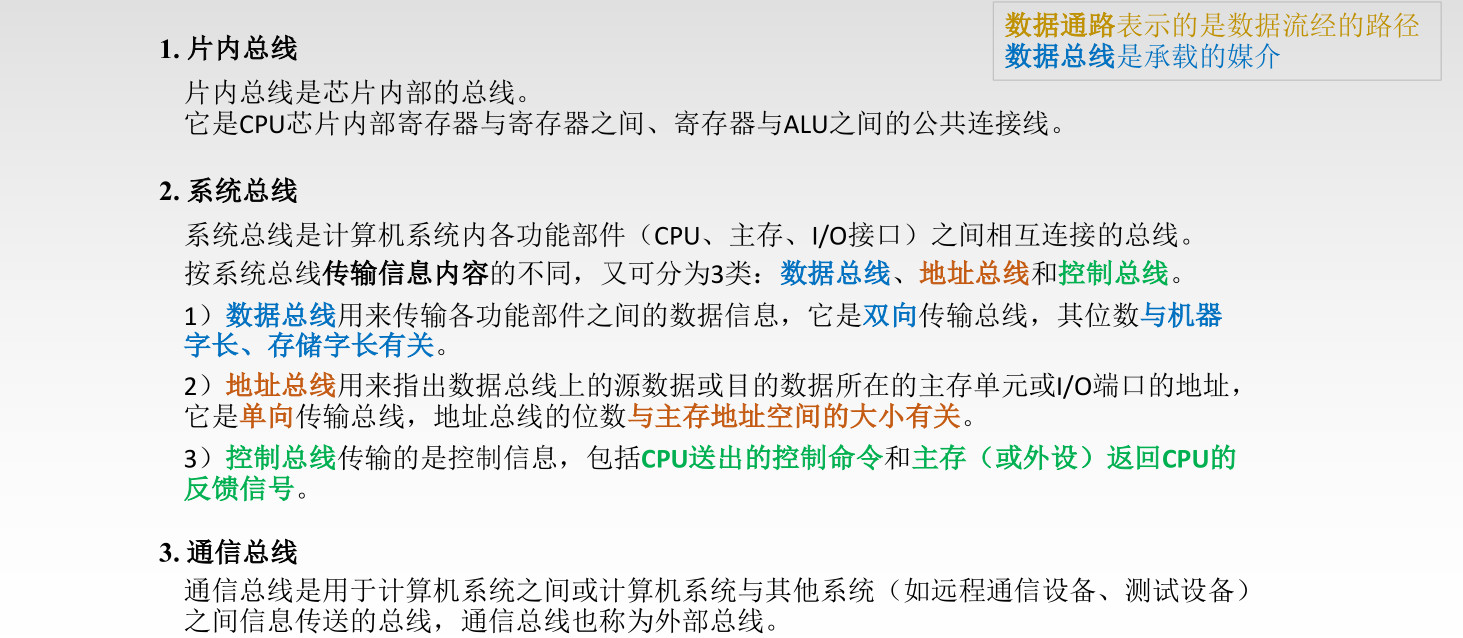

总线的分类(按总线功能)

这三种总线所连接的功能部件的层级是不一样的,片内总线连接CPU内部的各个功能部件,系统总线连接一台计算机里面的各个功能部件,而通信总线连接不同计算机

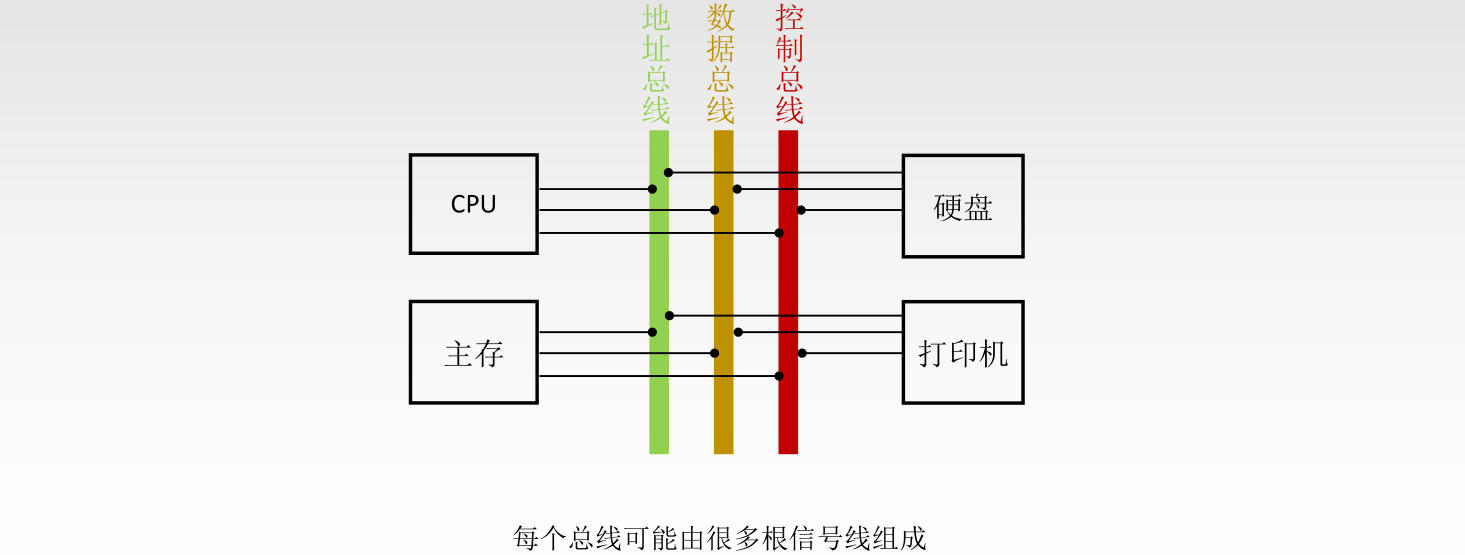

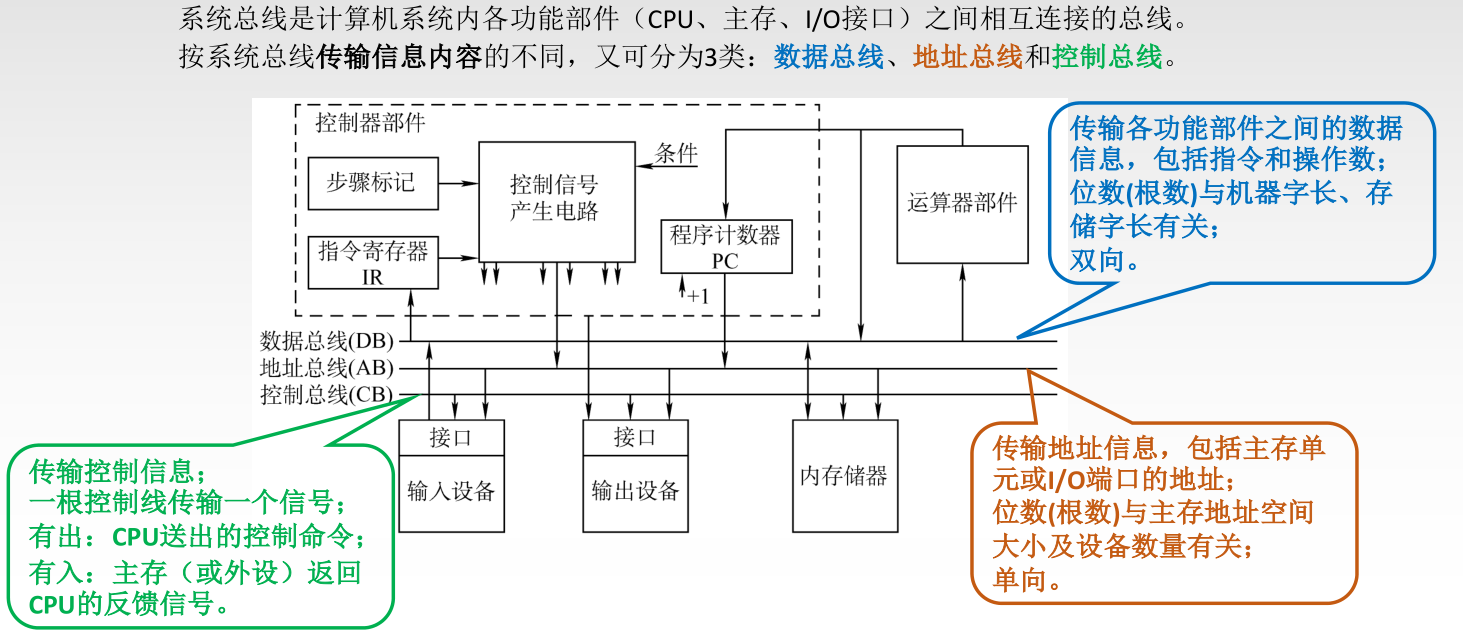

系统总线

当I/O设备和主存采用统一编址策略时,I/O设备的数量也会影响到地址总线应该设置的宽度

地址总线肯定是单向的,一定由CPU发送地址信号指明想要读写的设备或者主存的地址

单根控制线控制信号的传输是单向的

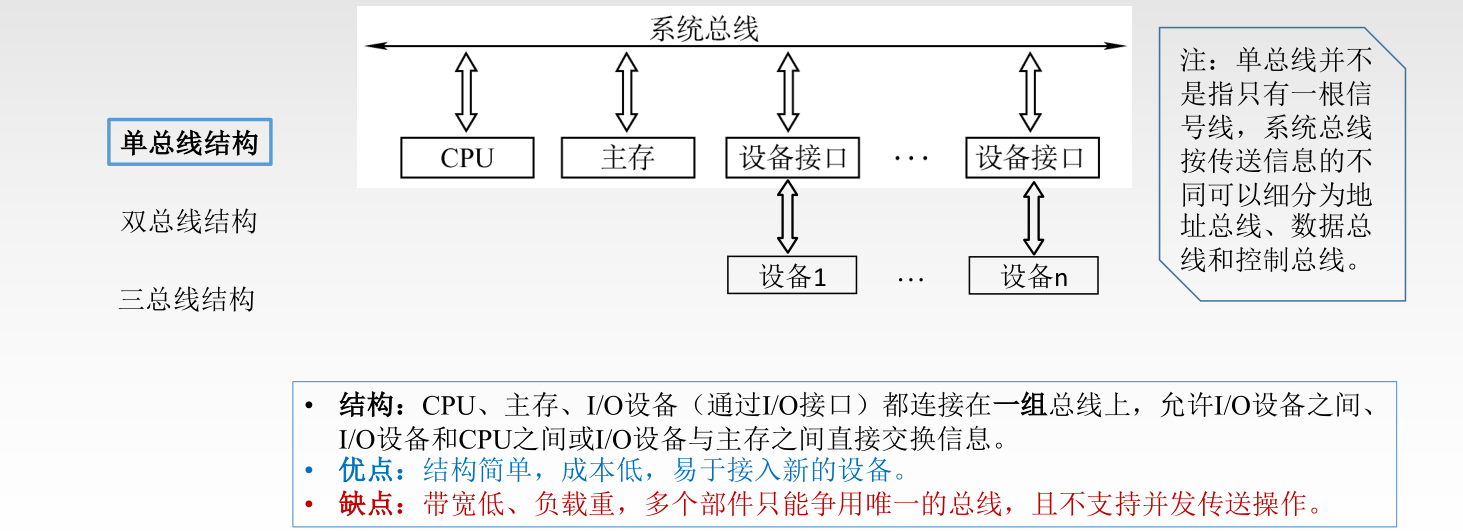

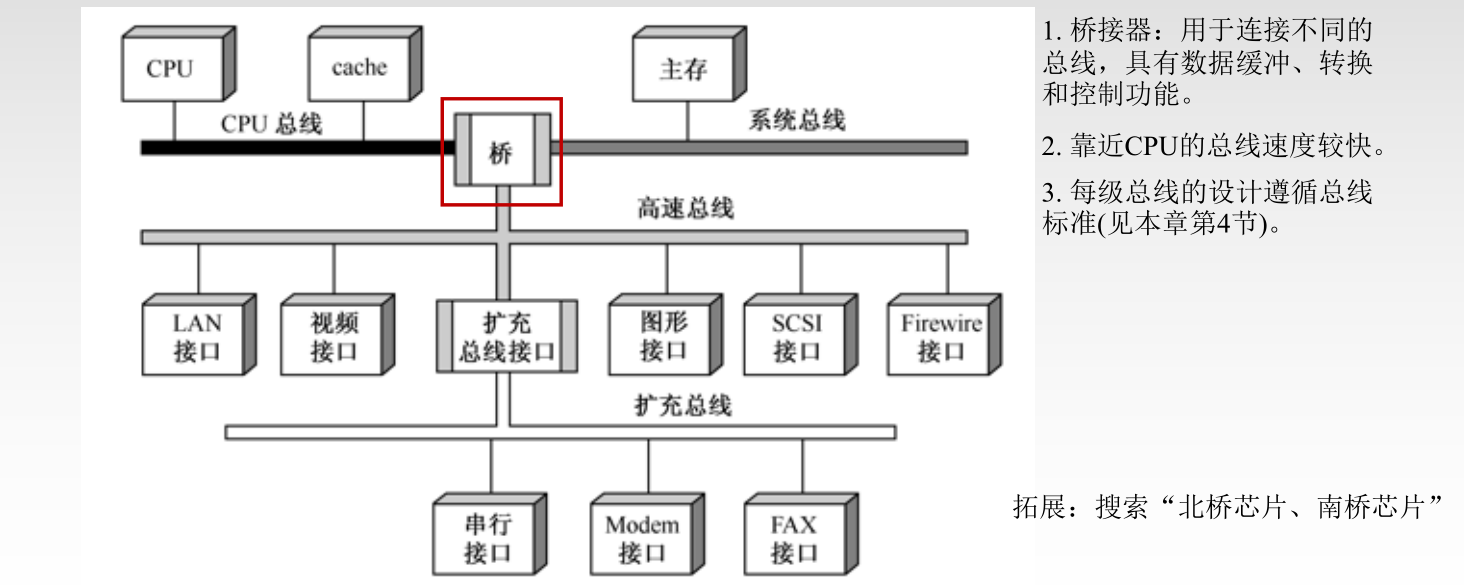

系统总线的结构

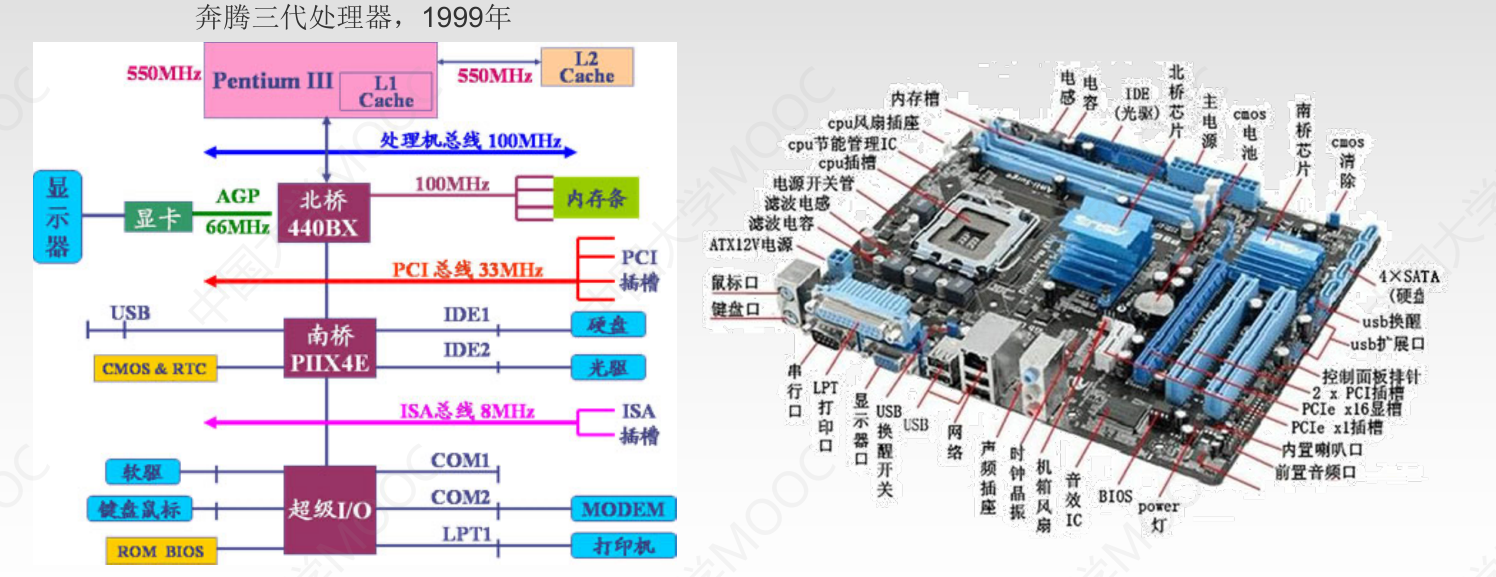

CPU和主存数据读写速度比较快,而键盘鼠标等外部设备数据传输速度很慢,当用快速的系统总线让慢速的设备传输数据时会造成性能的浪费

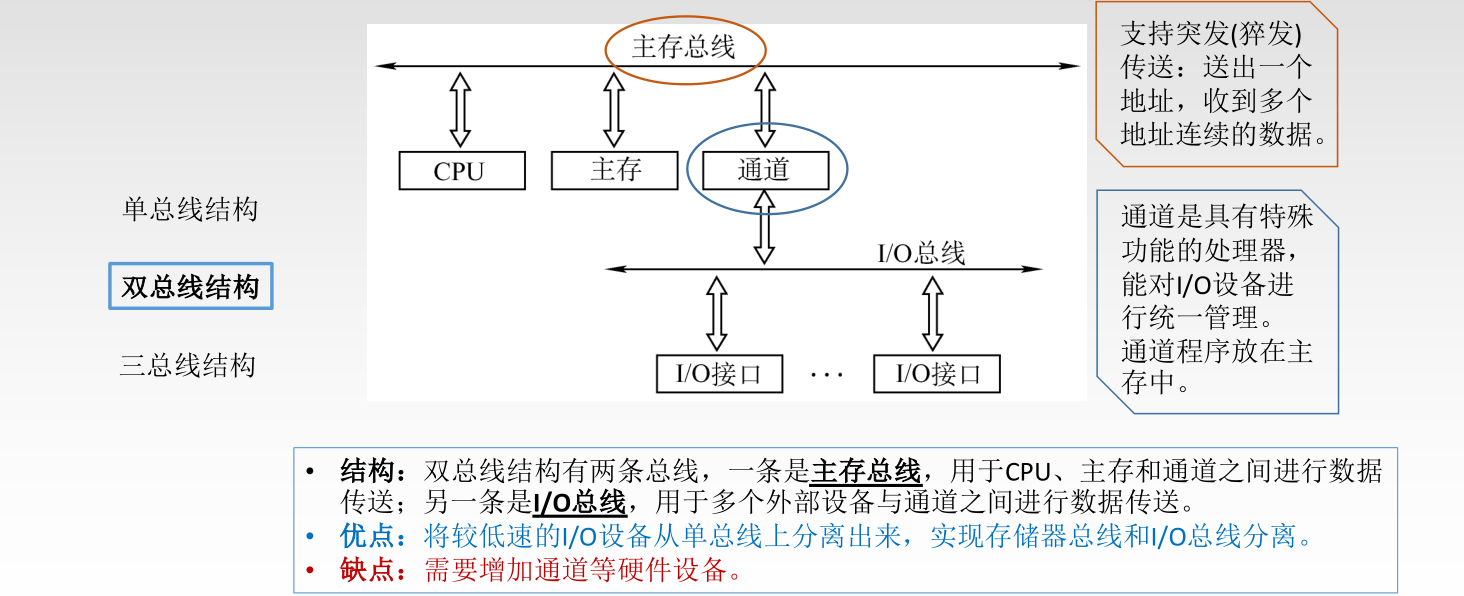

通道是一个小CPU,负责统一管理各种I/O设备,可以缓和CPU与各种I/O设备之间的速度矛盾。CPU给IO设备发出的命令还需要通过通道的处理再转发给I/O设备

通道与各个I/O设备之间的交互通过I/O总线进行,通道、主存和CPU之间的交互通过主存总线进行,显然主存总线的速度比I/O总线快

主存总线支持突发传送

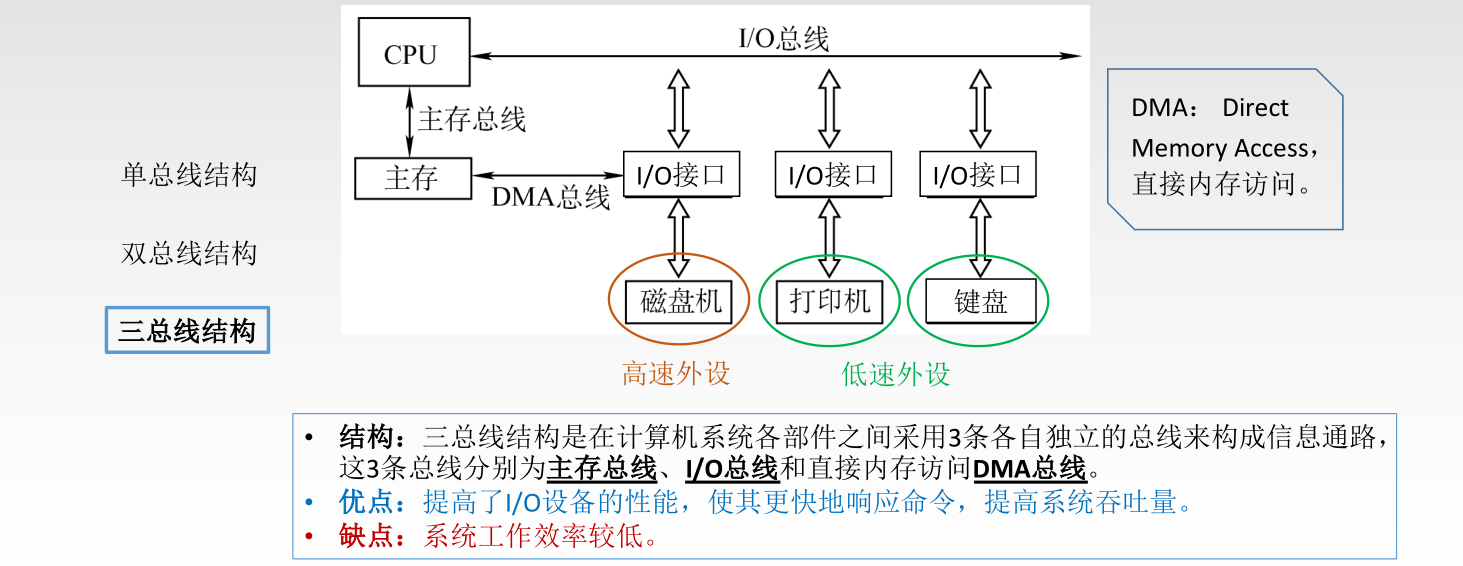

主存和某一些快速IO设备之间用DMA总线连接

对磁盘的数据读写以块为单位。CPU不需要通过慢速的I/O总线和磁盘机进行慢速的交互,而是可以先把CPU需要的数据从磁盘机通过DMA总线读入多个块到主存,CPU再直接从快速的主存当中取走数据

CPU可以直接通过I/O总线和某些慢速I/O设备进行交互

这三个总线同一时刻只能有一个总线在工作,这就导致了系统整体的工作效率较低

高速总线用于连接显卡等一些快速设备

不同总线之间速度存在差异,因此需要增加中间设备桥接器,可以把串行输入的数据并行地发给CPU,进行总线仲裁决定把CPU的使用权分配给哪一个设备。北桥芯片和南桥芯片就是桥接器

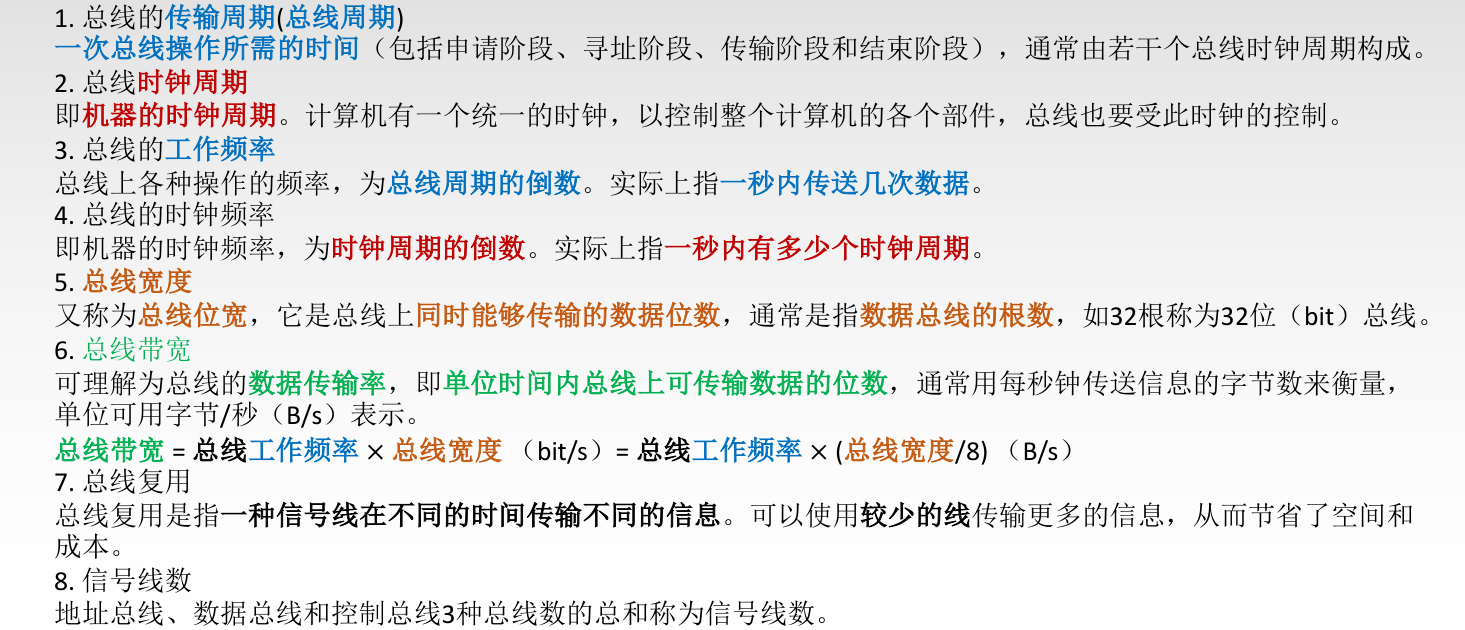

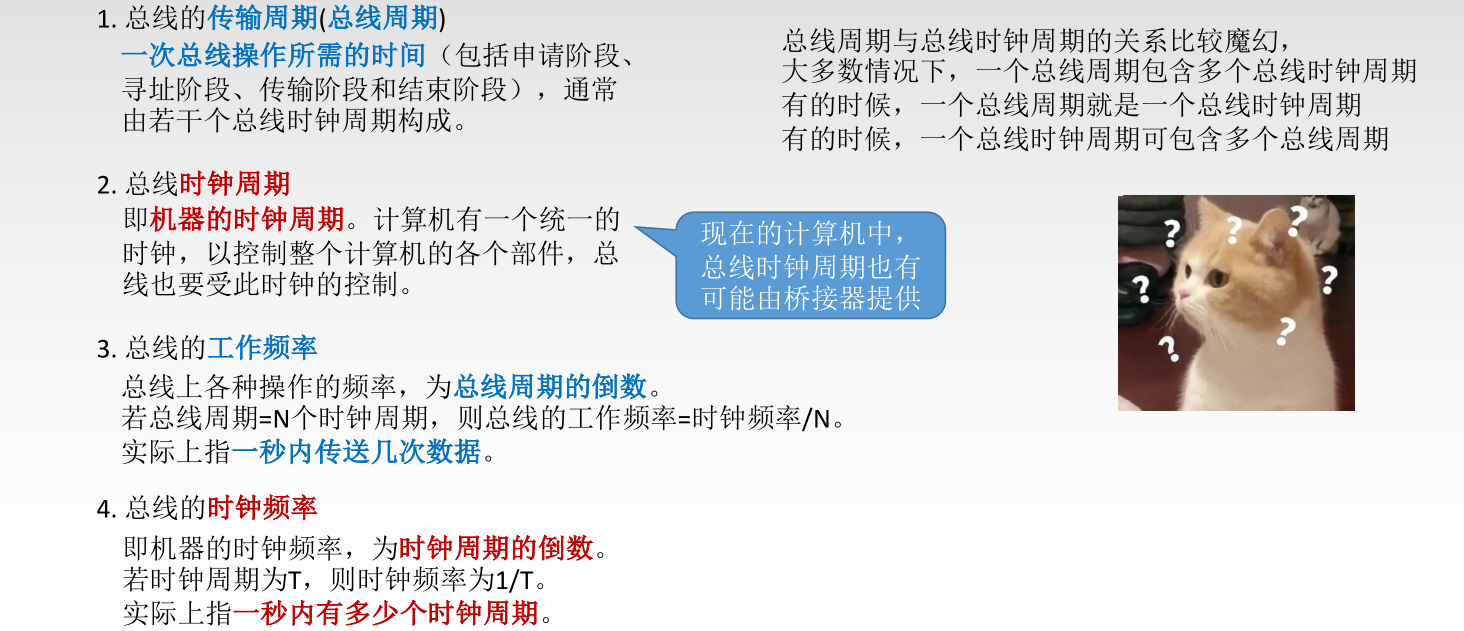

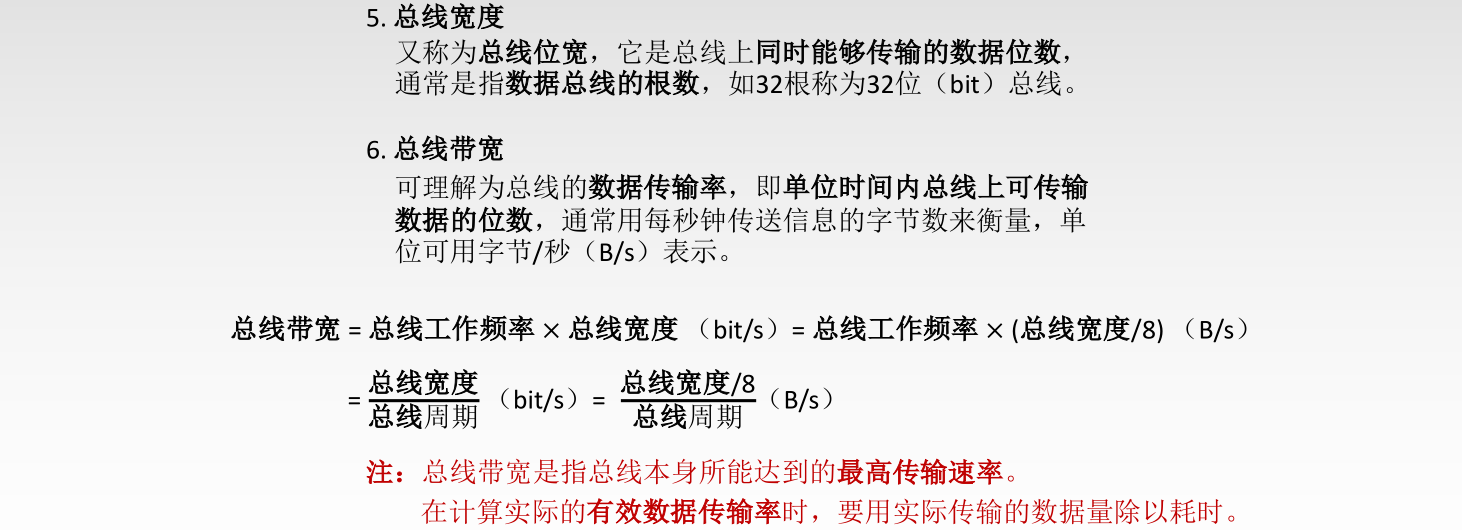

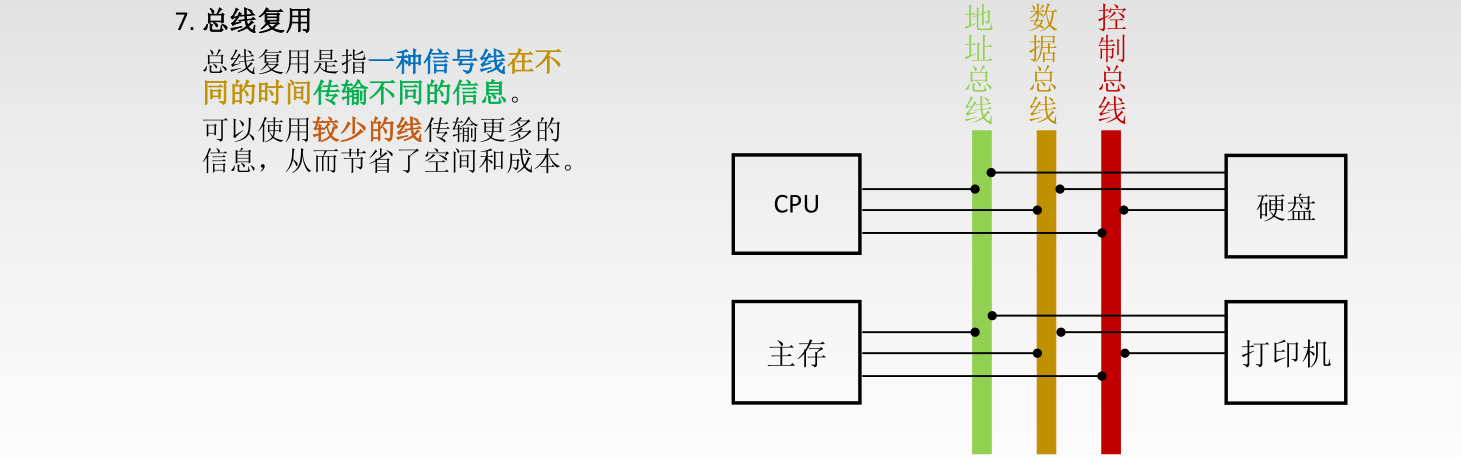

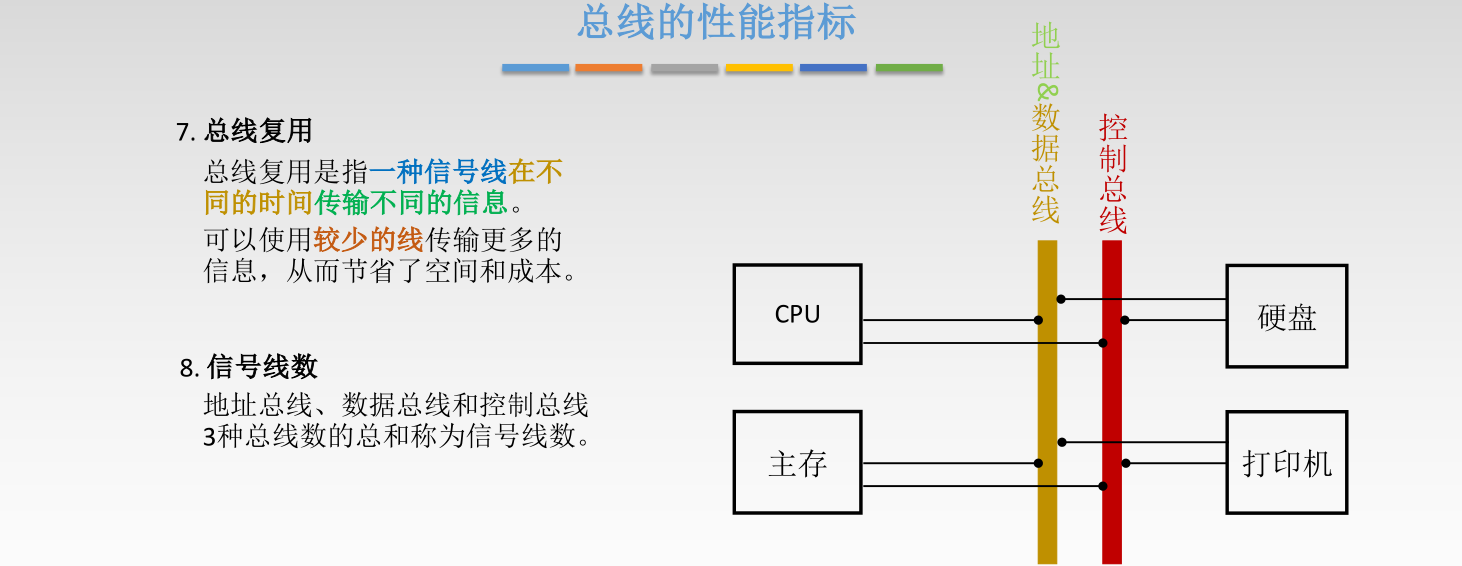

总线的性能指标

总线的性能指标

一个总线时钟周期可以包含多个总线周期 —— 有的总线当中当时钟部件发出时钟信号时,检测到上升沿和下降沿都会进行数据传输

通常总线的时钟周期跟机器的时钟周期一致,CPU发出的节拍信号决定了这个总线时钟周期的长度

桥接器也会发出时钟信号,这个时钟信号频率和CPU的不一样

总线传输的这些信息当中可能并不是所有的信息位都是有效信息,比如可能会加上一些校验位或者开头和结尾标志

串行总线与并行总线

总线的性能指标2

总线仲裁

408考生可不看

基本概念

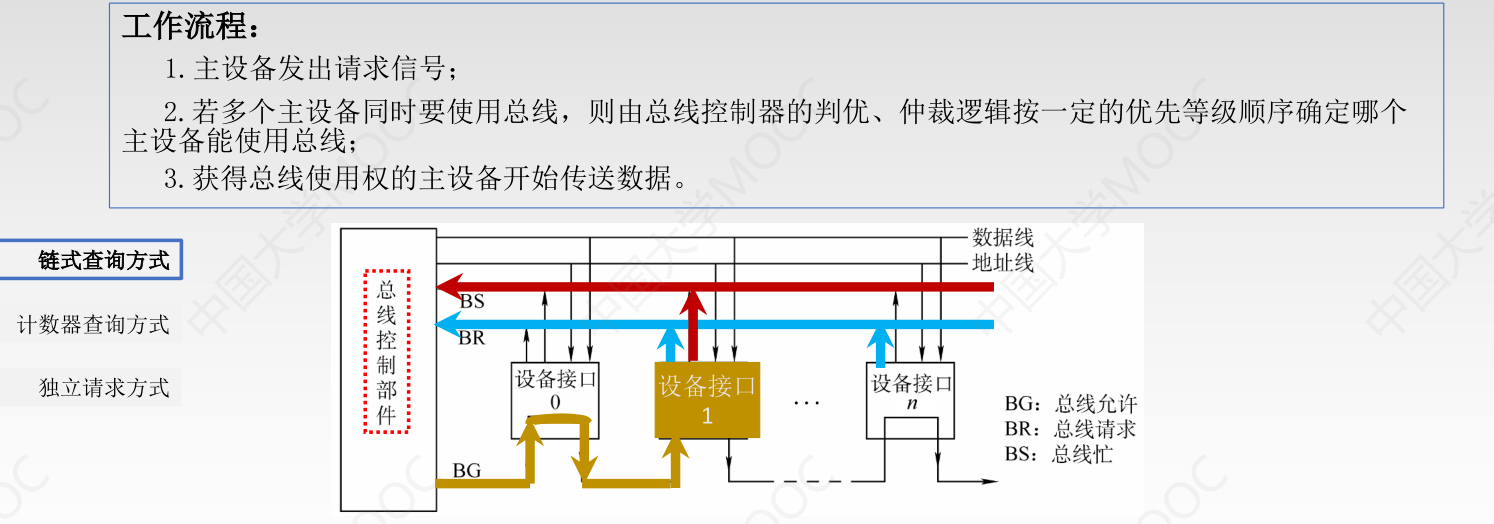

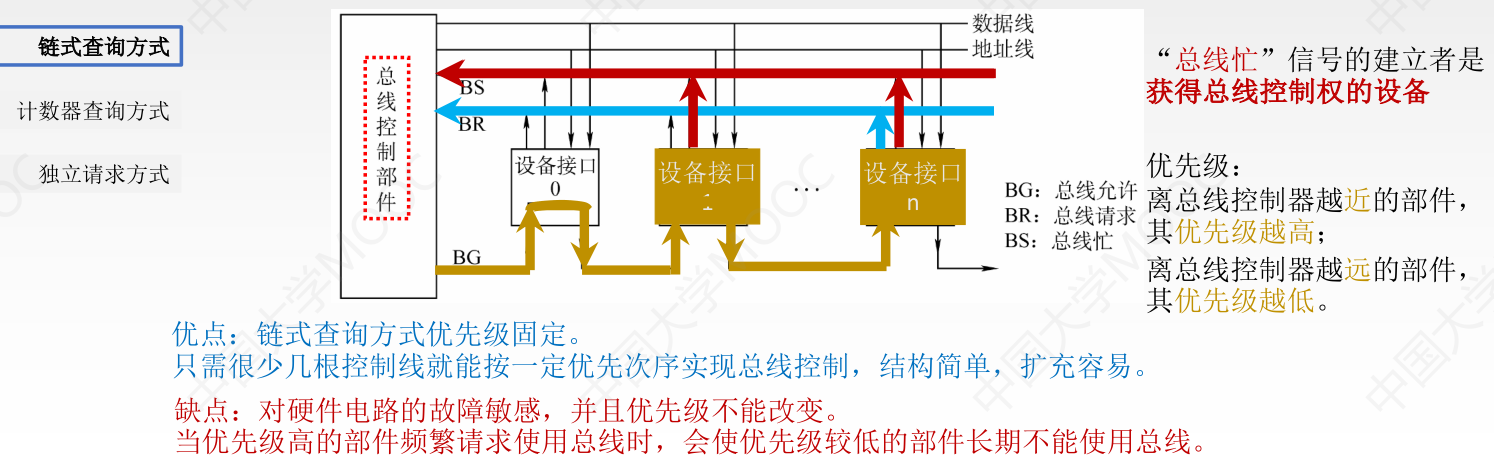

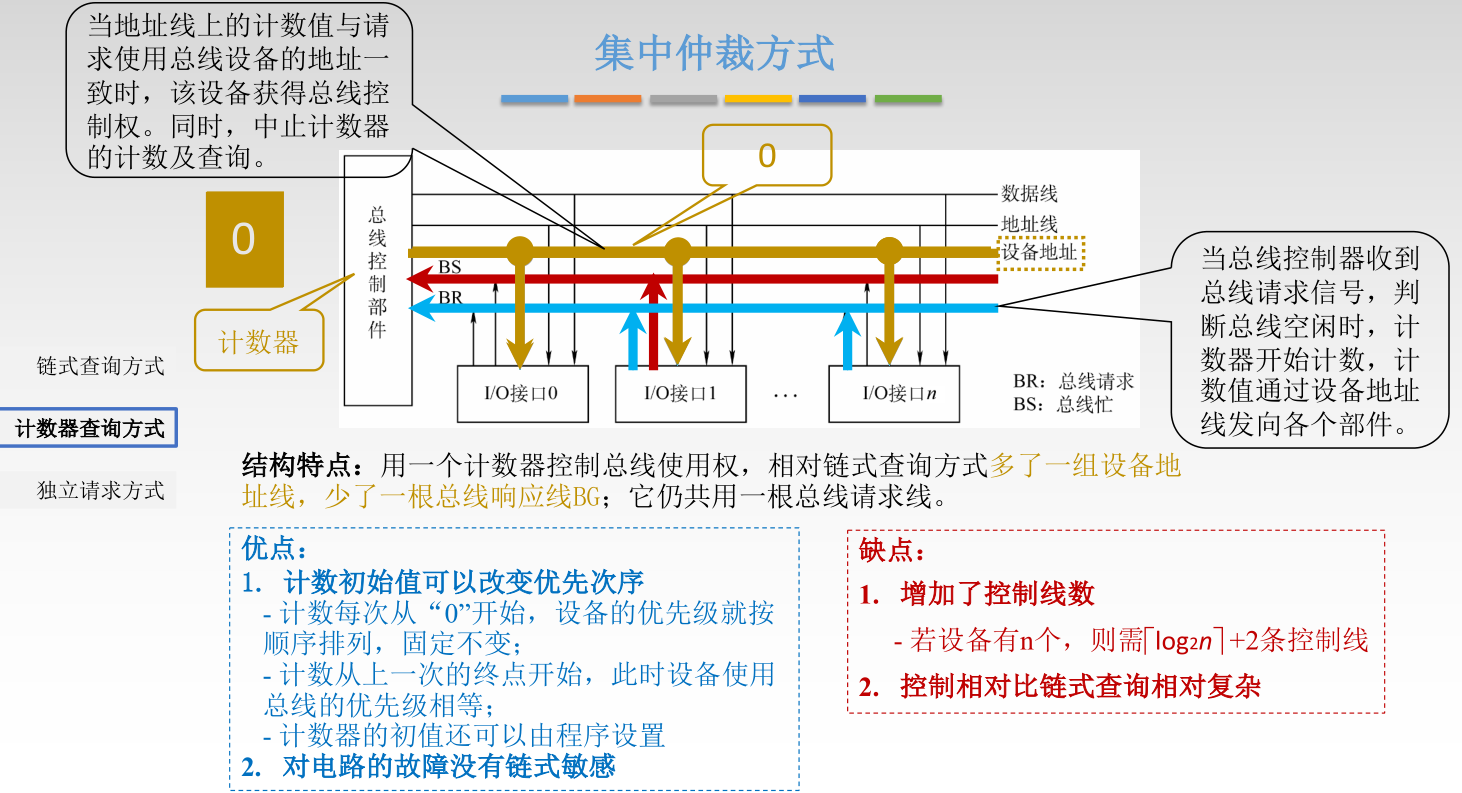

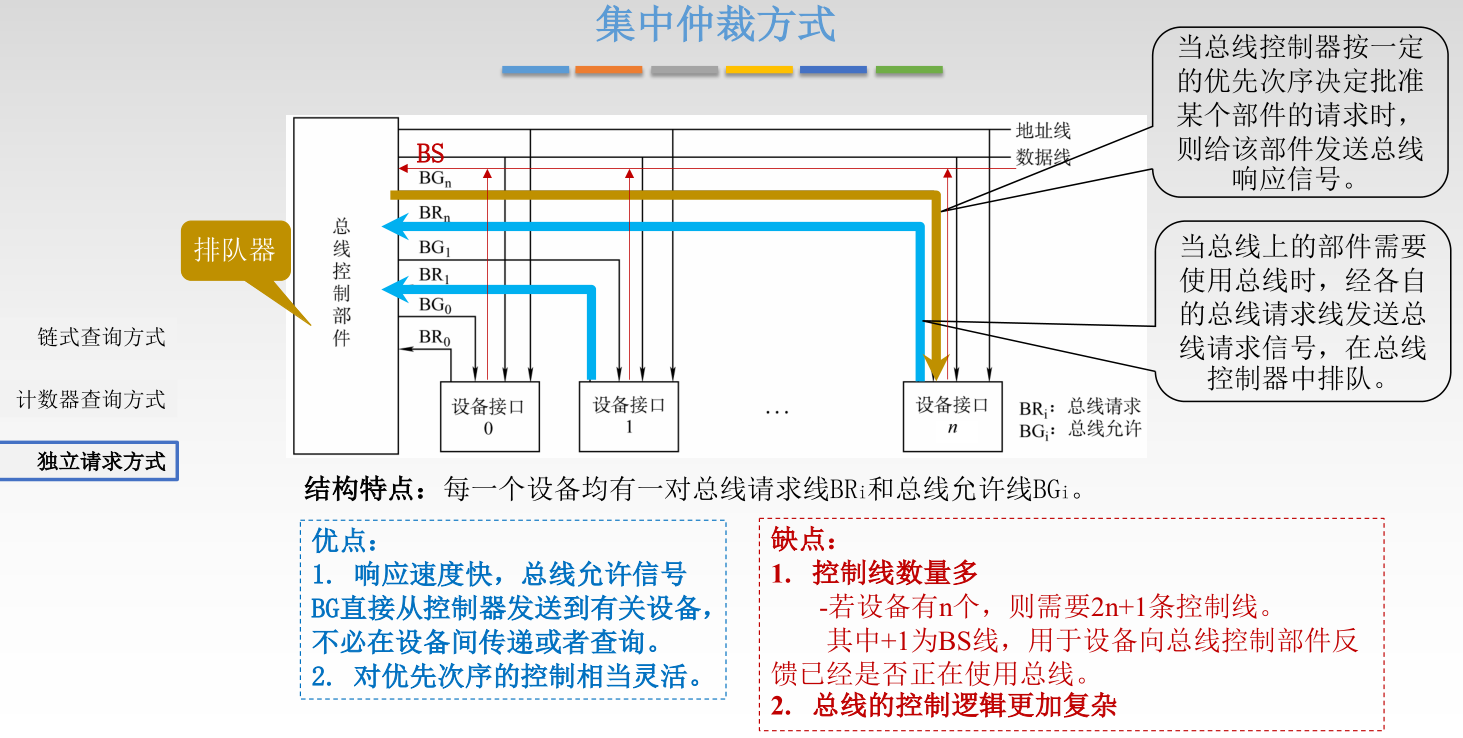

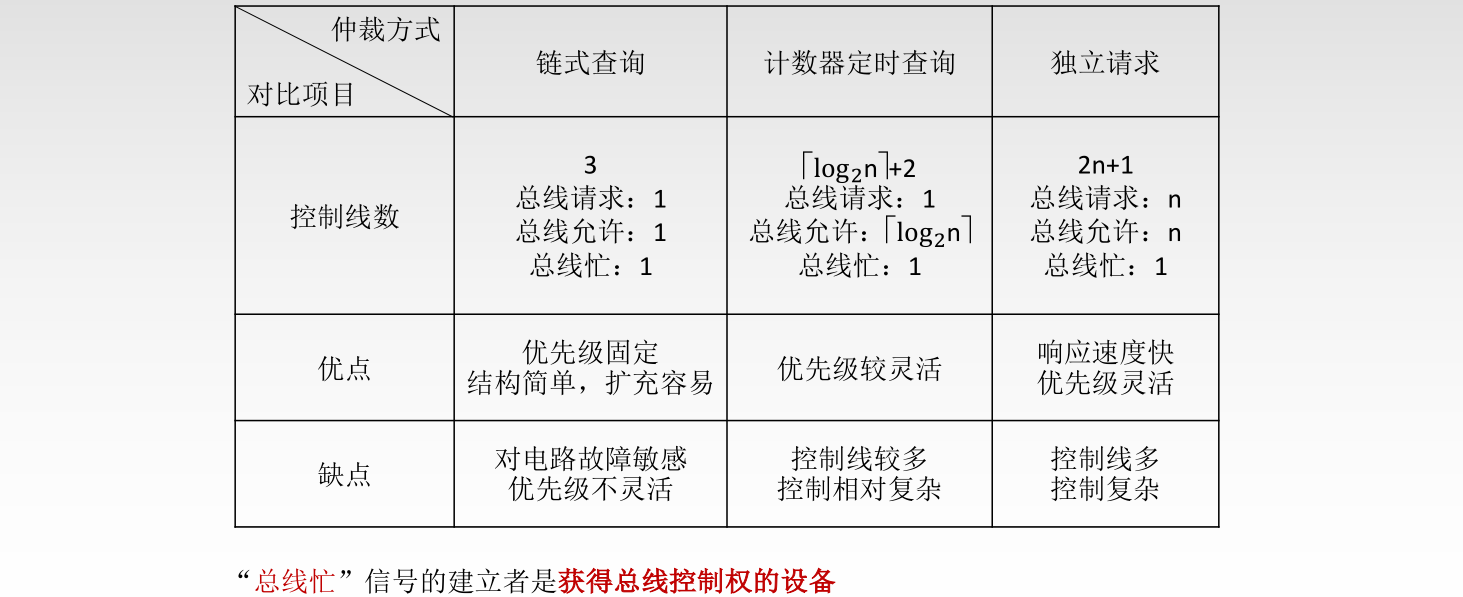

集中仲裁方式

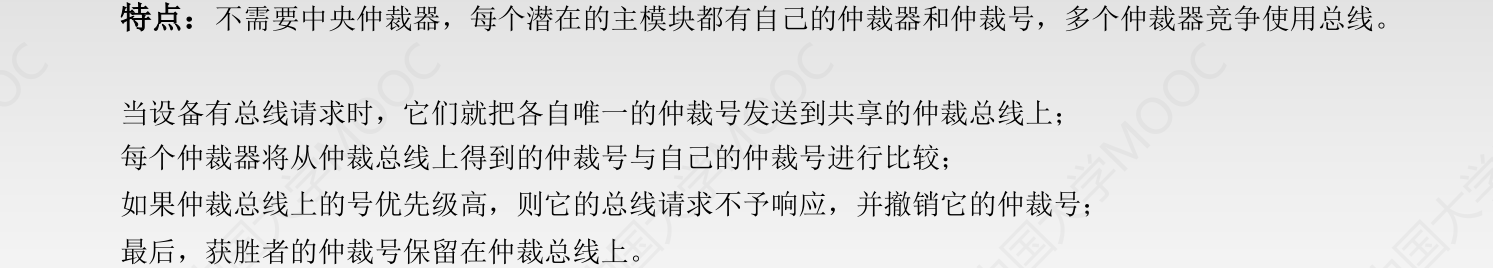

分布仲裁方式

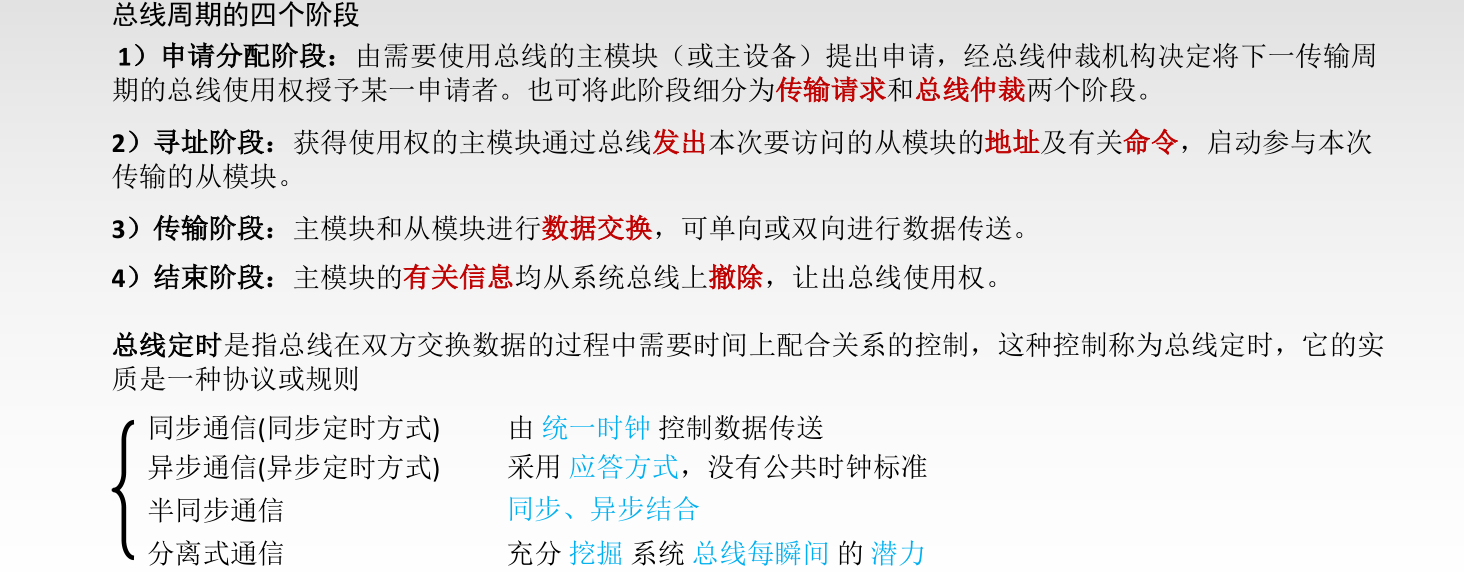

总线操作和定时

总线传输的四个阶段

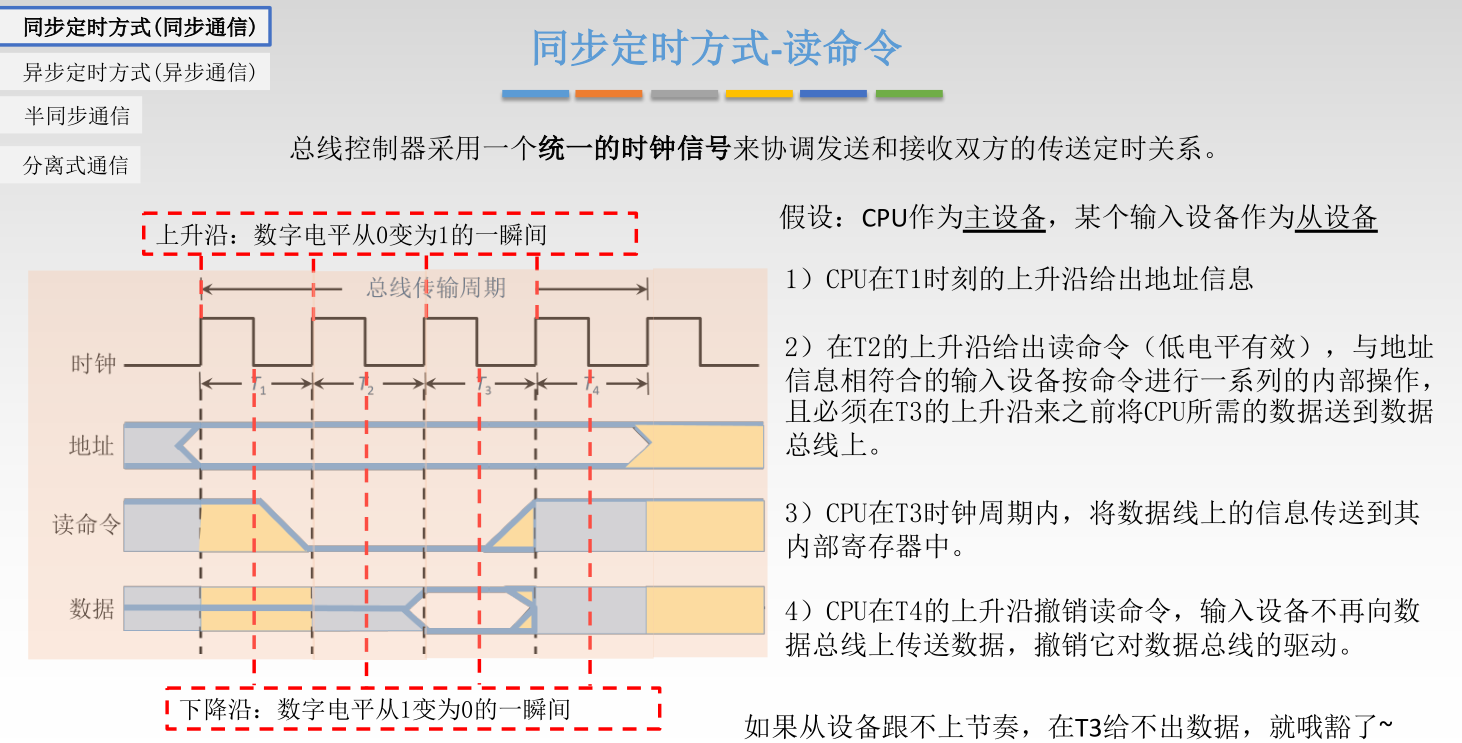

同步定时方式-读命令

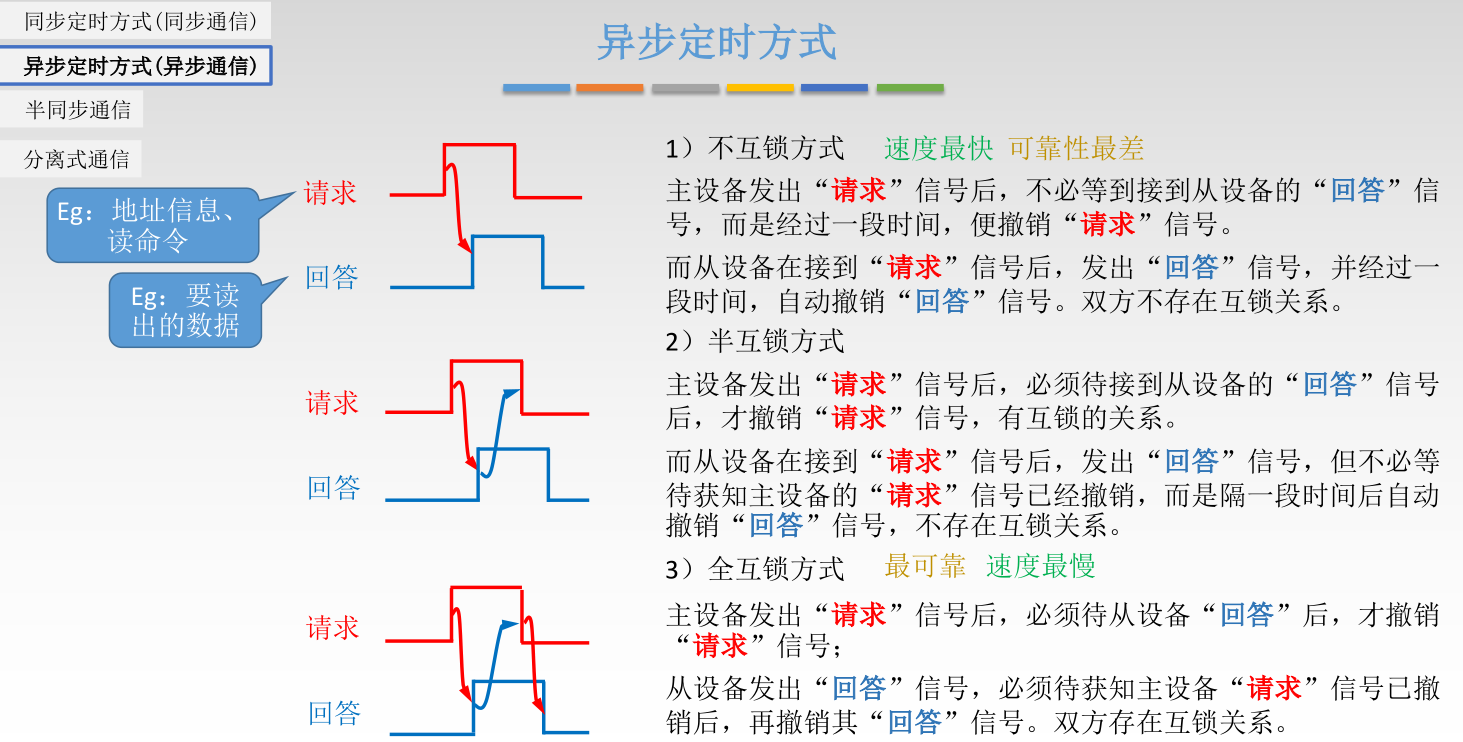

异步定时方式

只有主设备和从设备请求回答的动作完成之后才意味着完成了一个总线周期

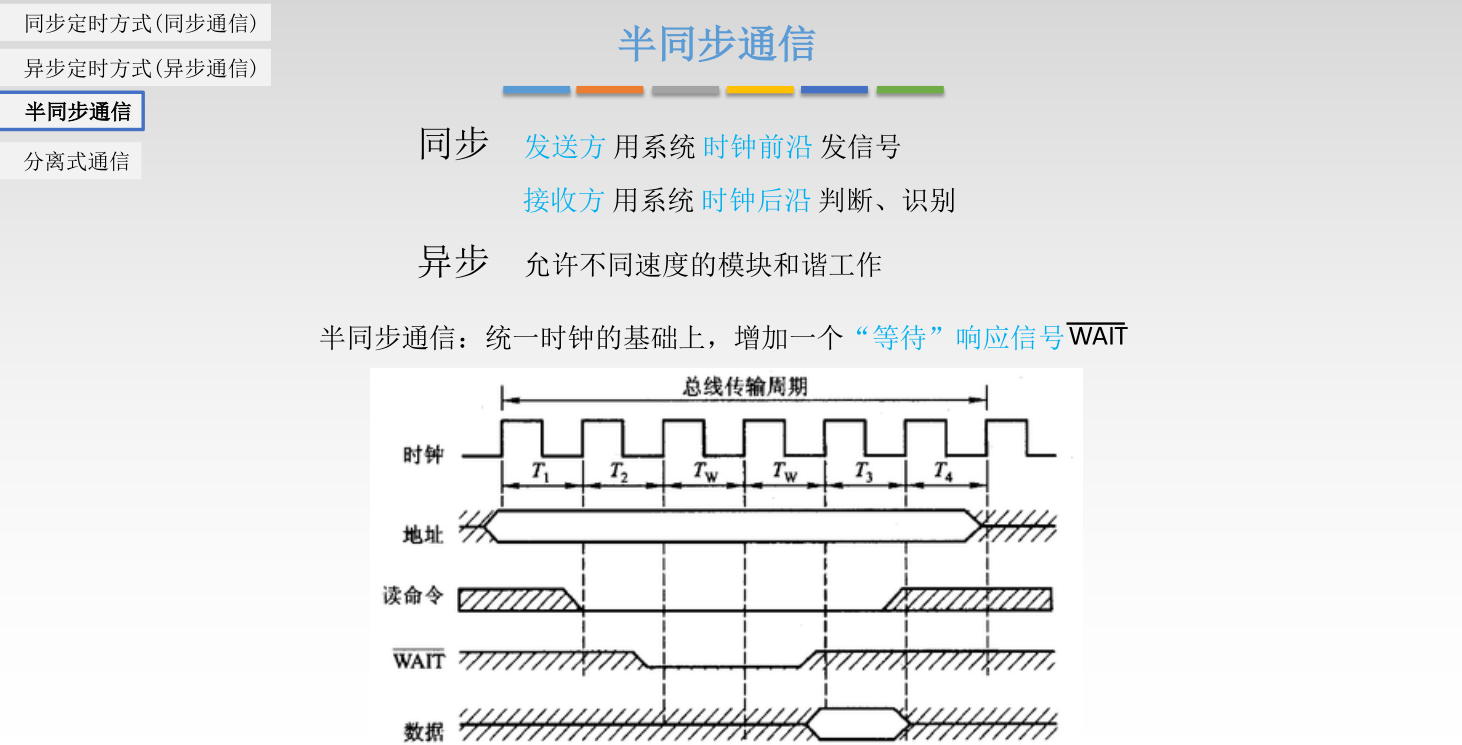

半同步通信

增加一个等待反馈信号 W A I T ‾ \overline{WAIT} WAIT,当从设备跟不上节奏时就会通过控制线路给总线的控制器进行反馈,让总线控制器等几个节拍

这种半同步通信方式也有统一的时钟节拍,但是可以动态地调整每一个传输周期内包含的时钟节拍数,因此也能够支持速度差异较大的主设备和从设备之间进行数据交互

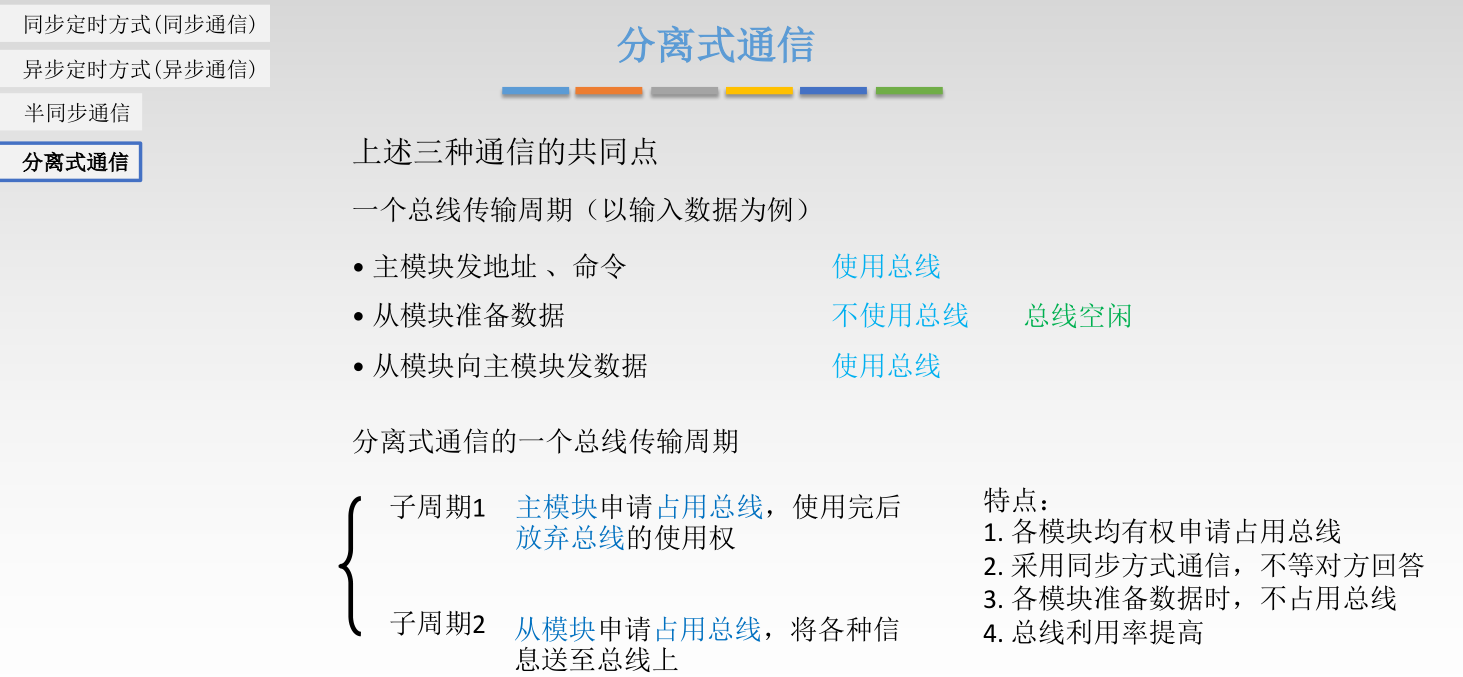

分离式通信

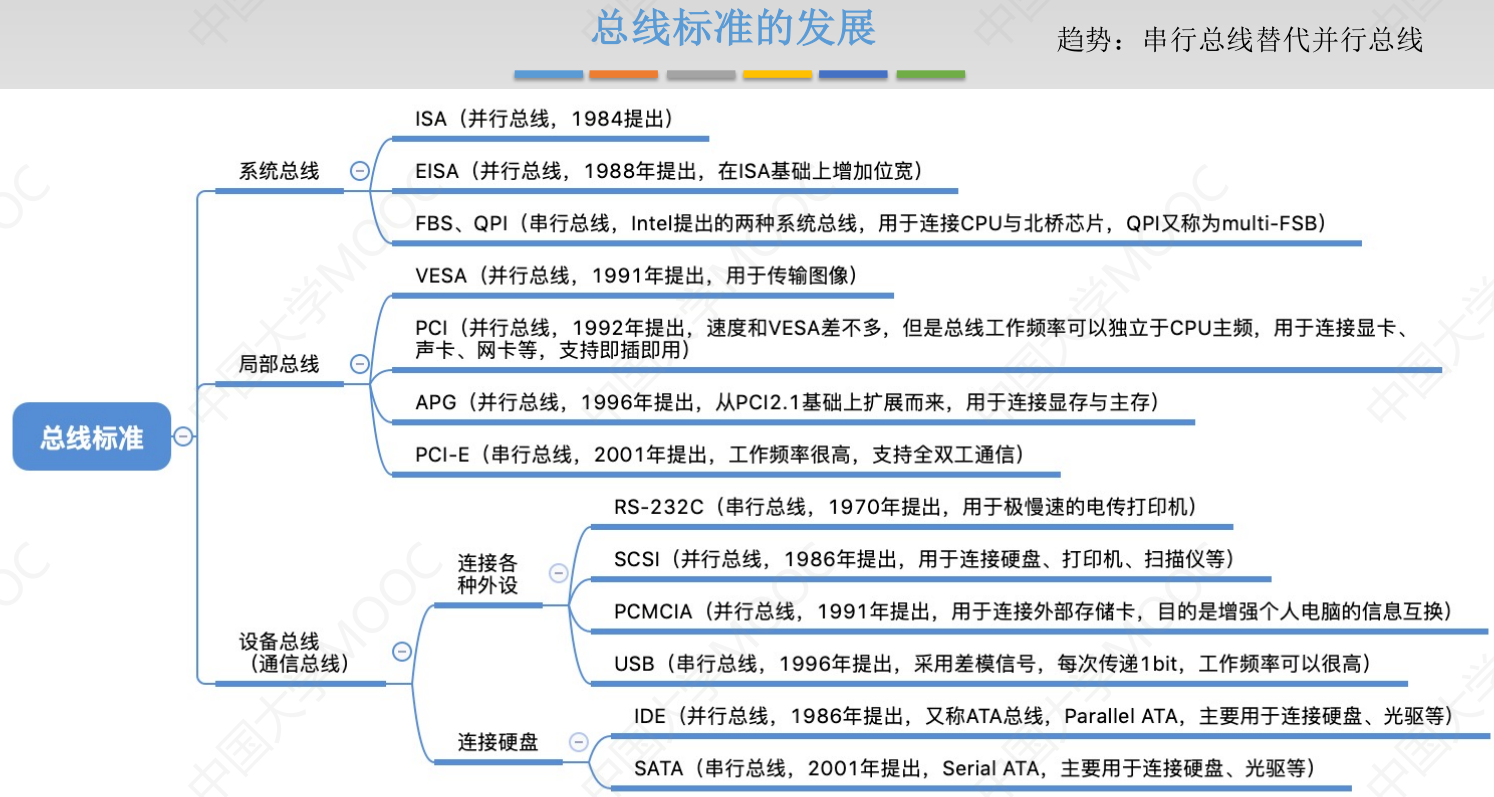

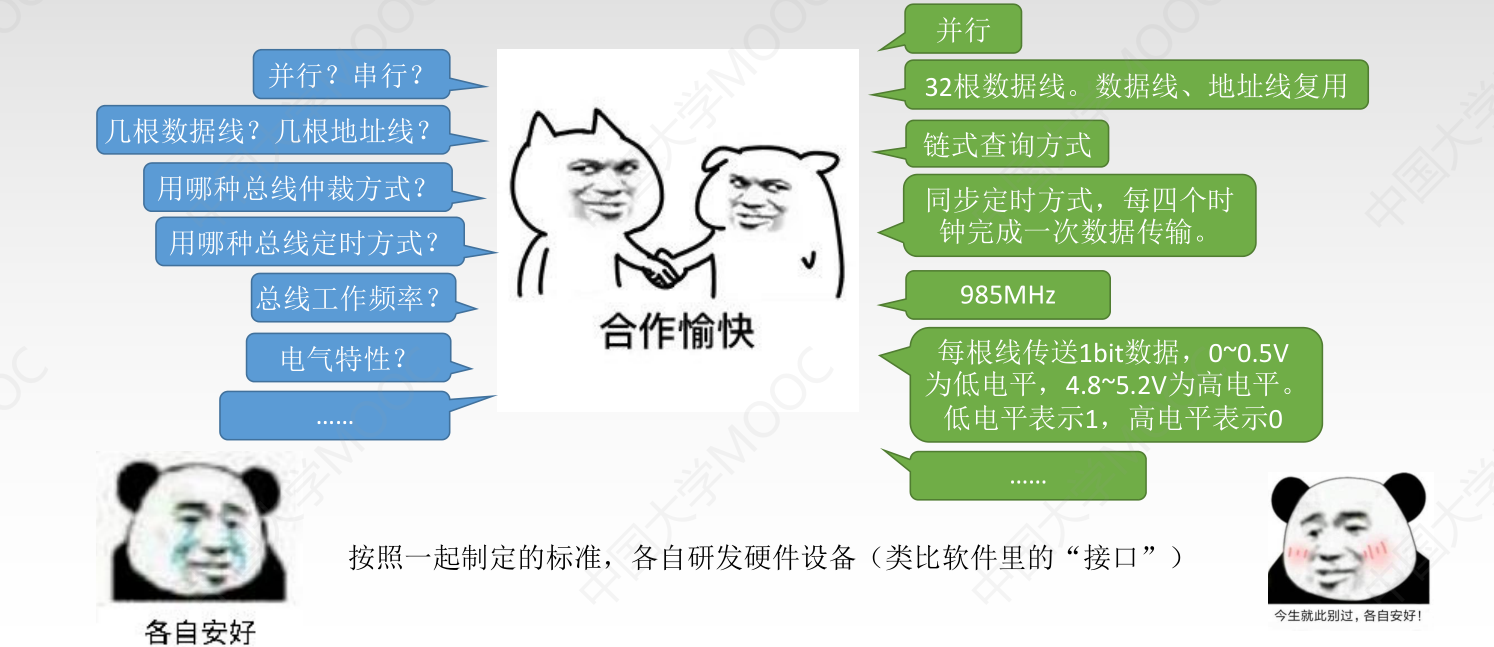

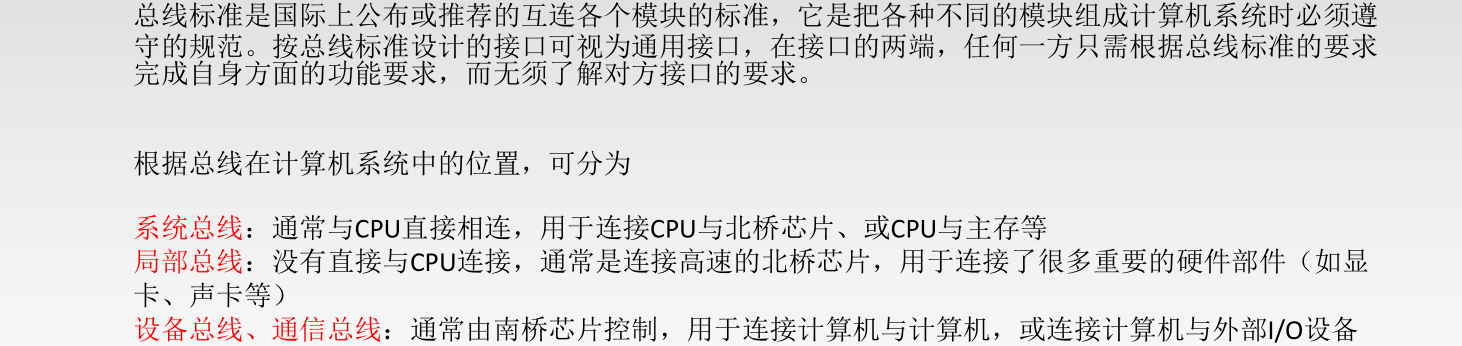

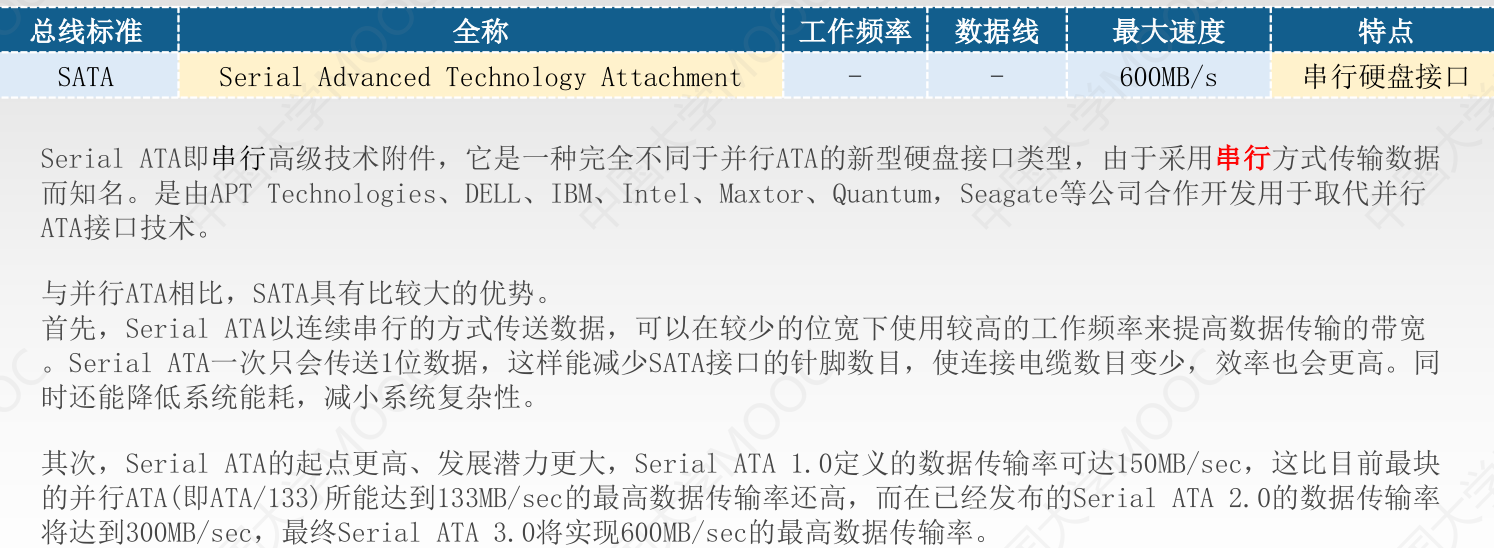

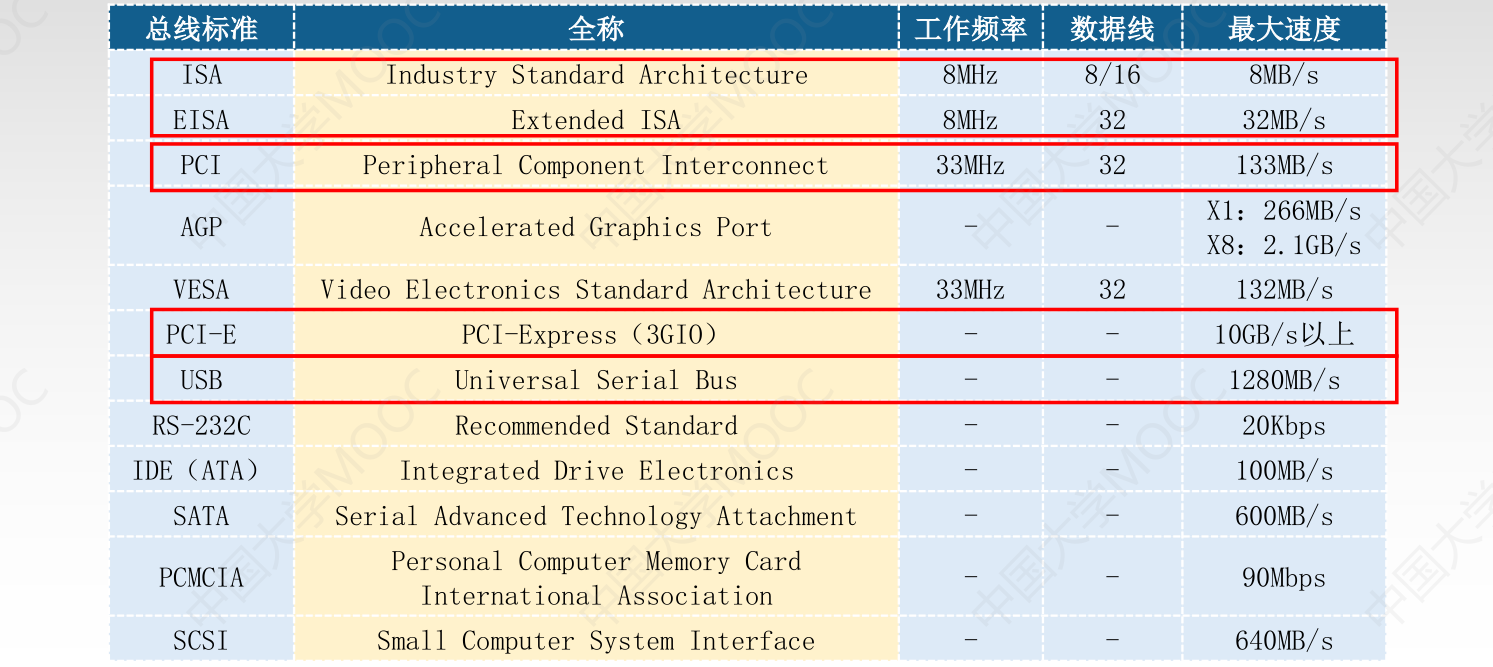

总线标准

408考生可不看

总线标准的基本概念

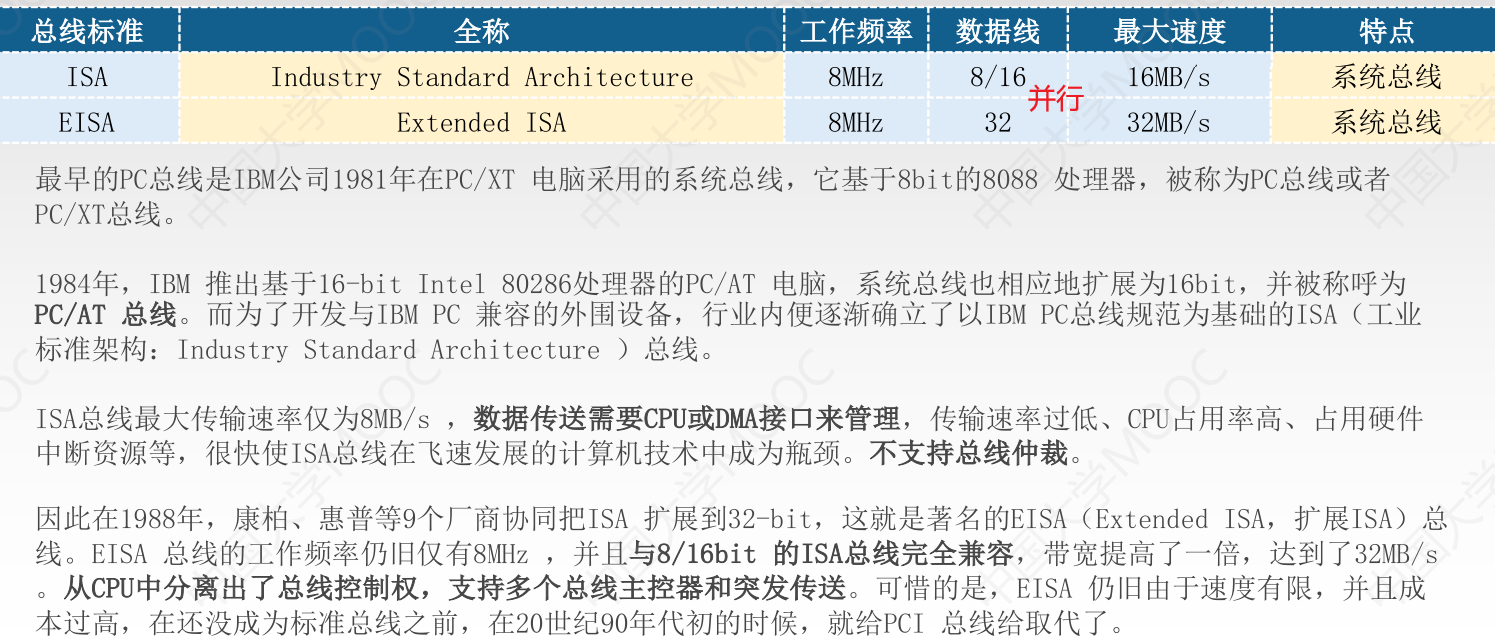

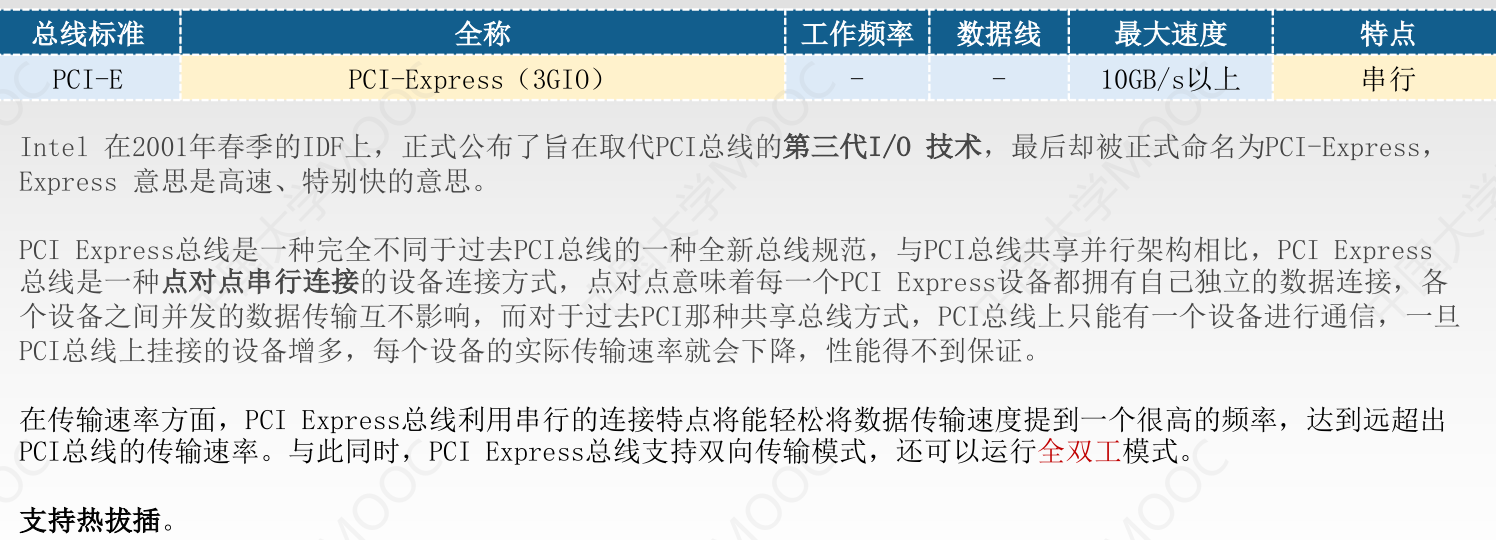

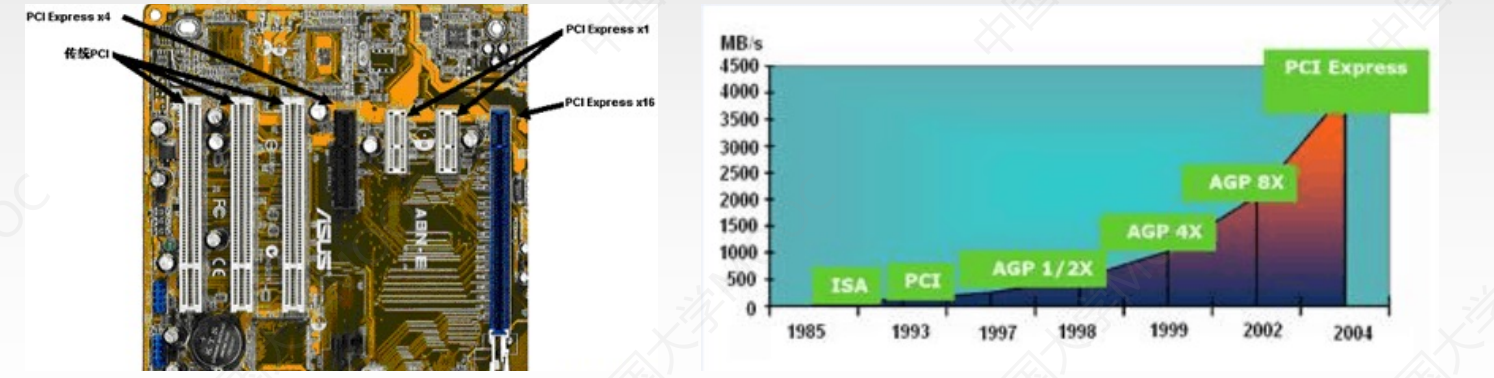

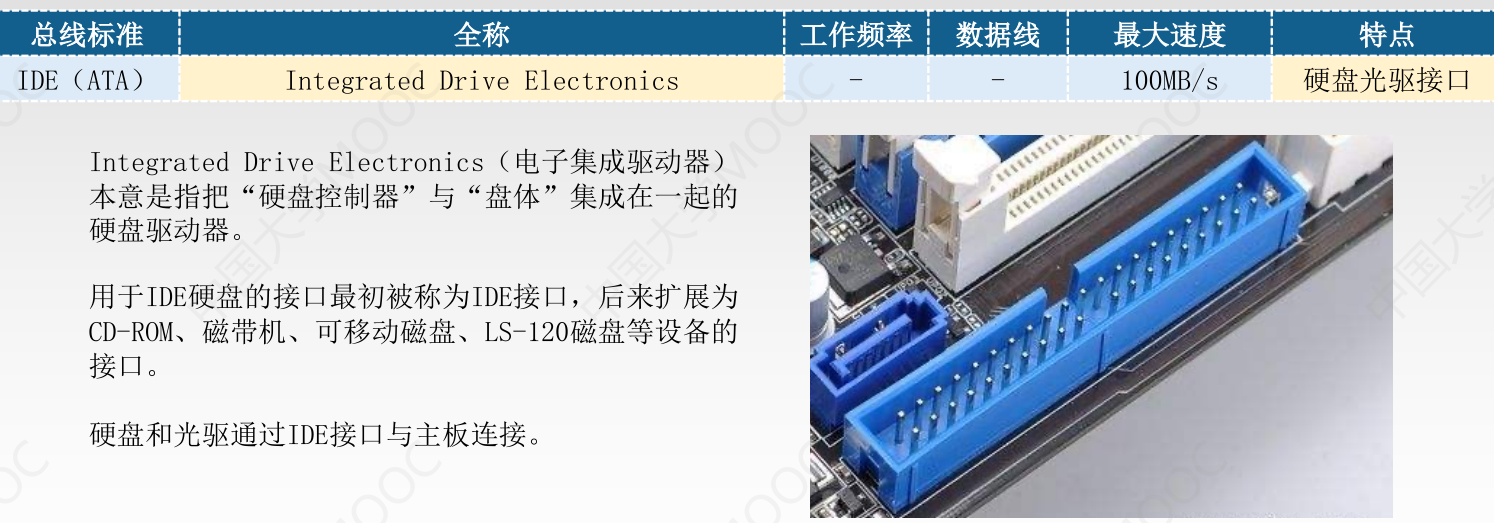

系统总线标准

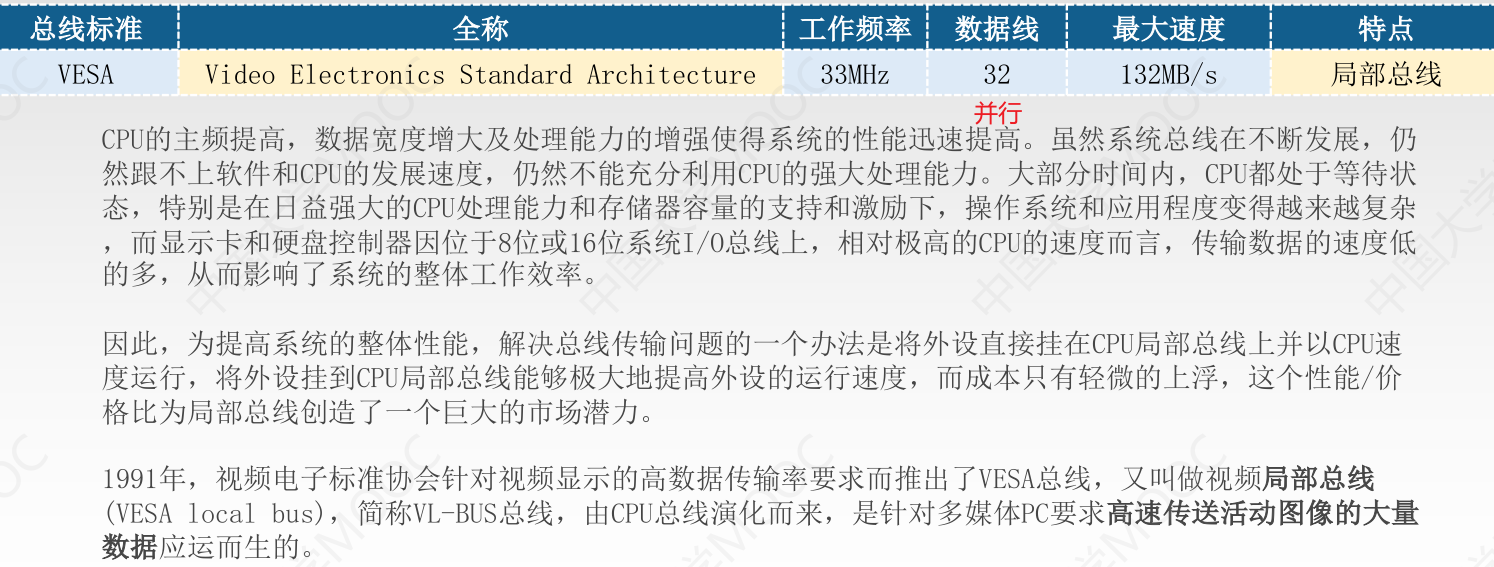

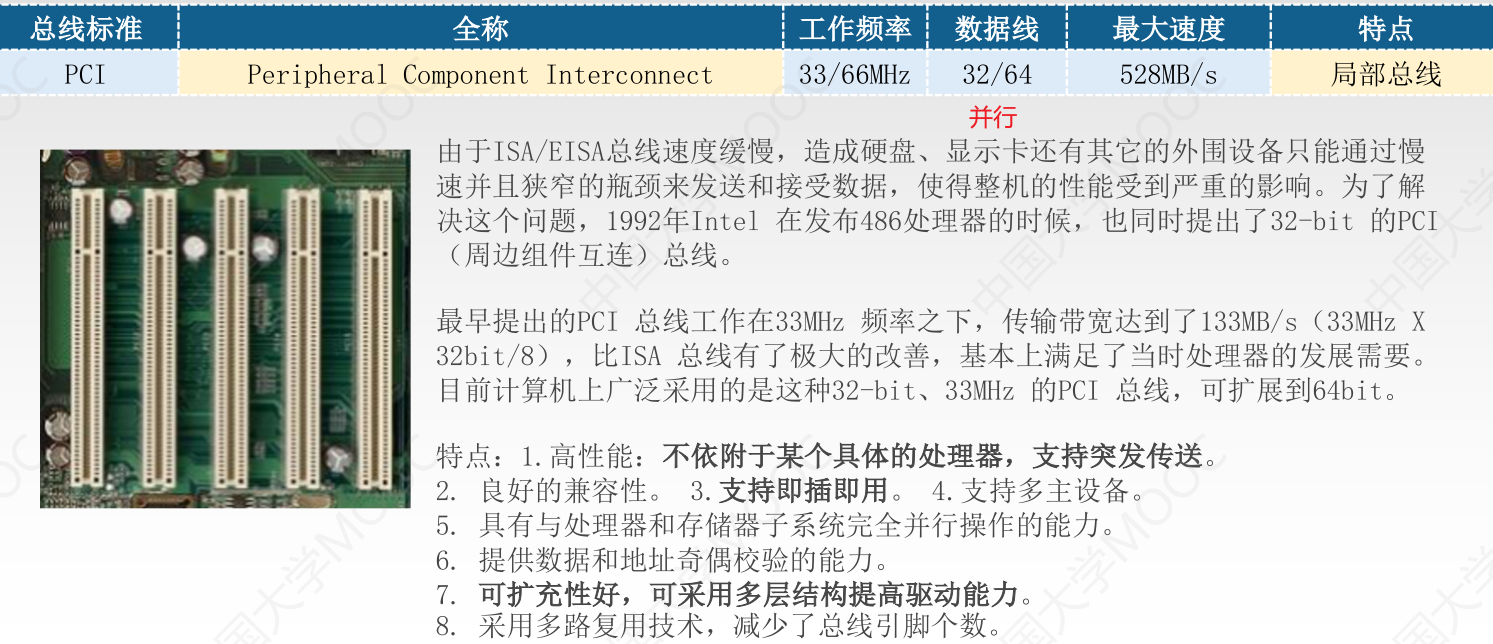

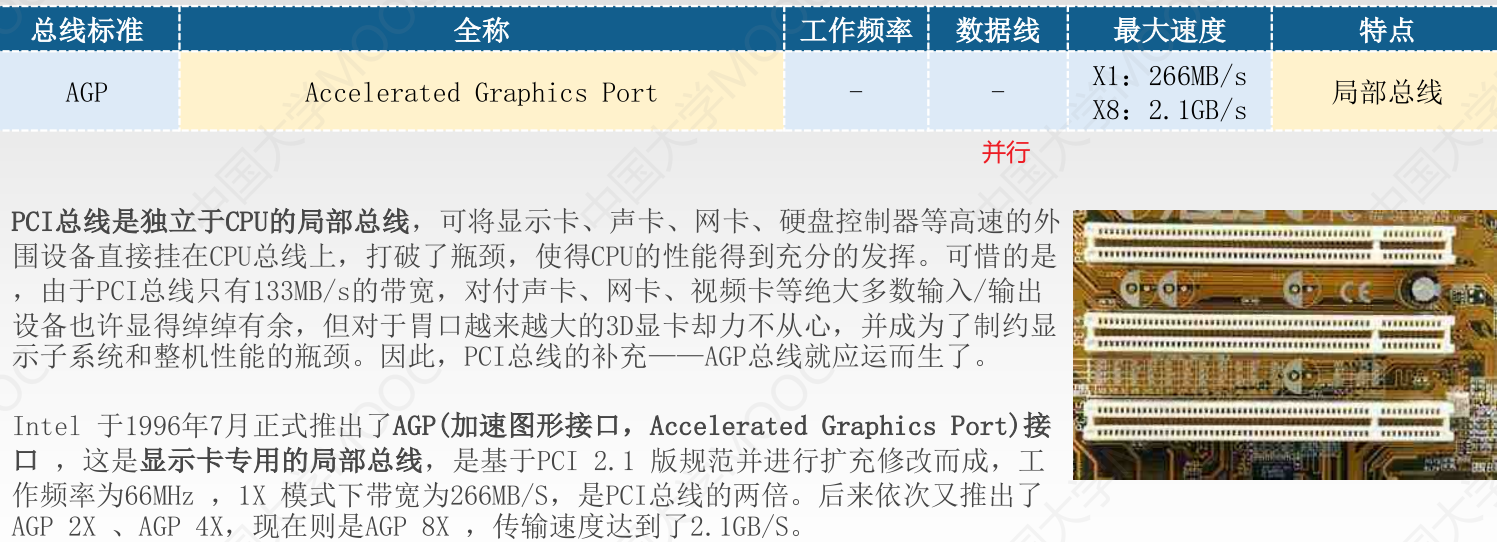

局部总线标准

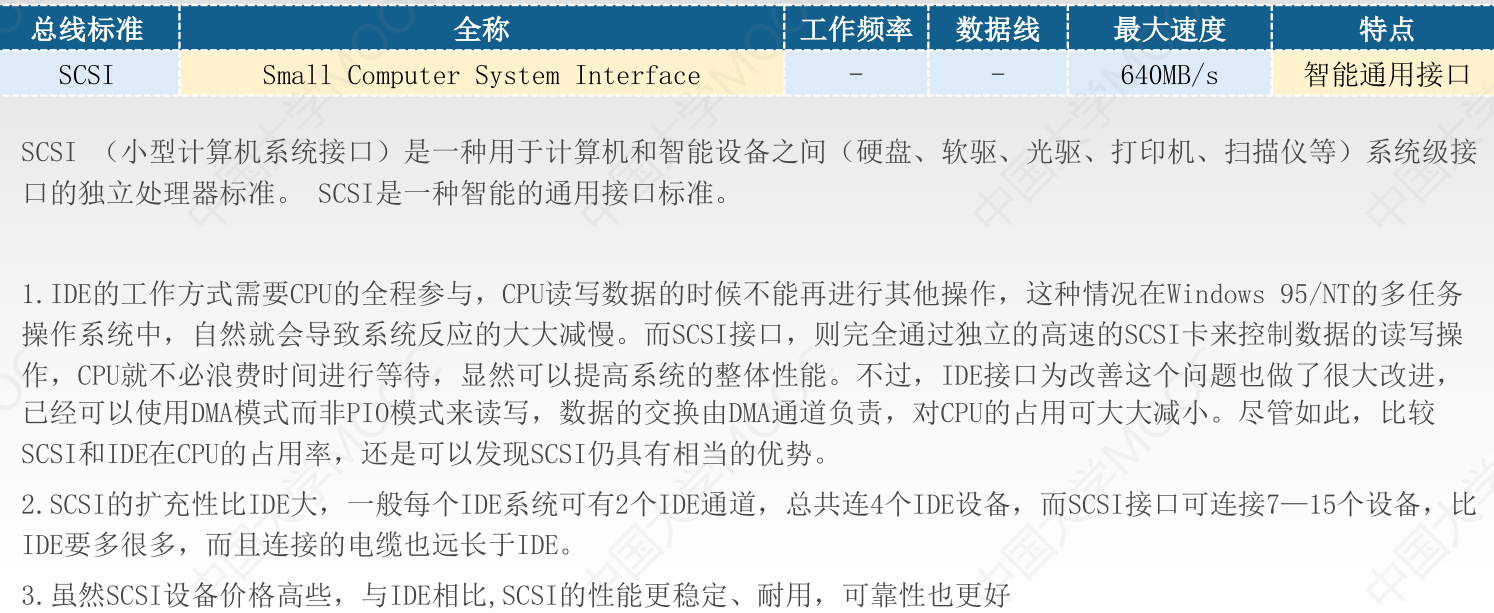

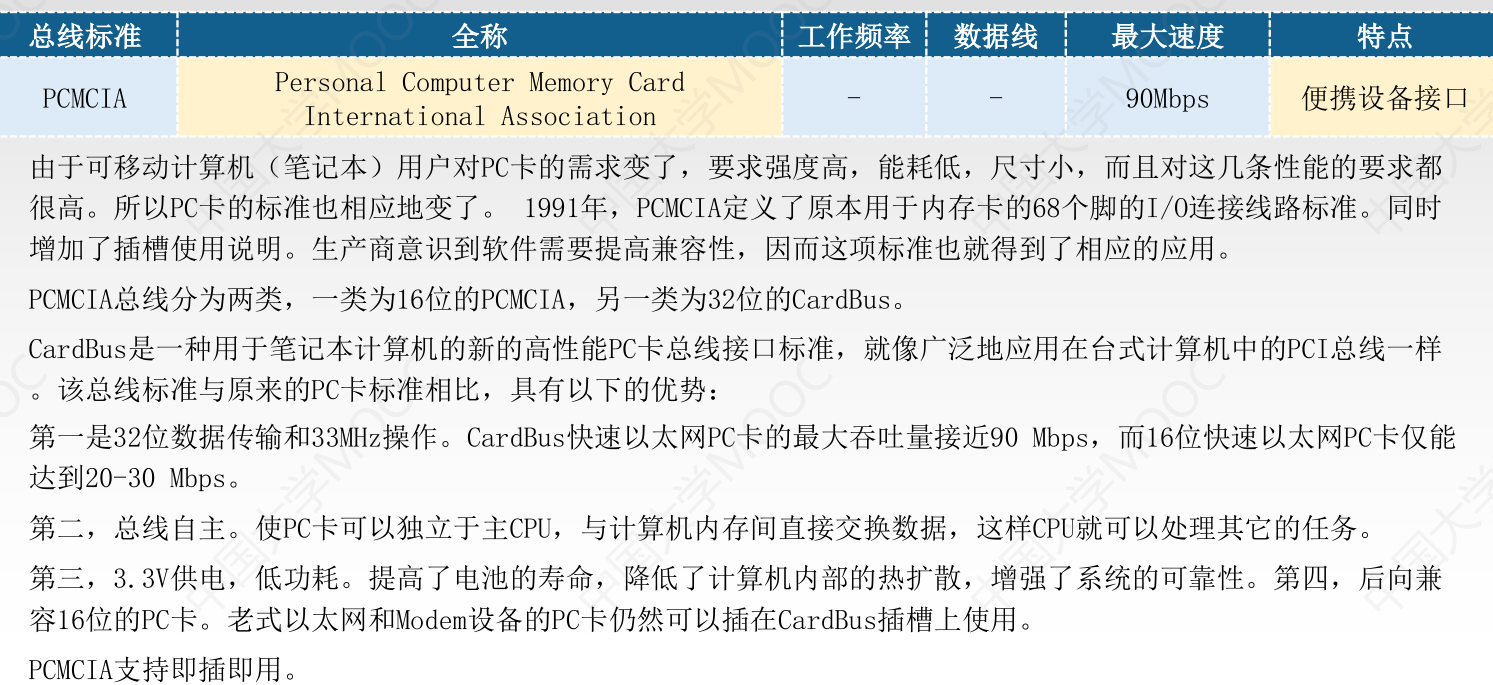

设备总线标准

速度对比

为何用串行总线取代并行总线

实例

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?