工具平台: xilinx vivado 2022.2

操作系统:WIN11

PS:从VIVADO2019.2之后,VIVADO不再支持WIN7系统

一、综合阶段报错

1)

二、布局布线阶段报错

1)时钟输入至HD BANK GC 无法调用Clocking Wizard IP。

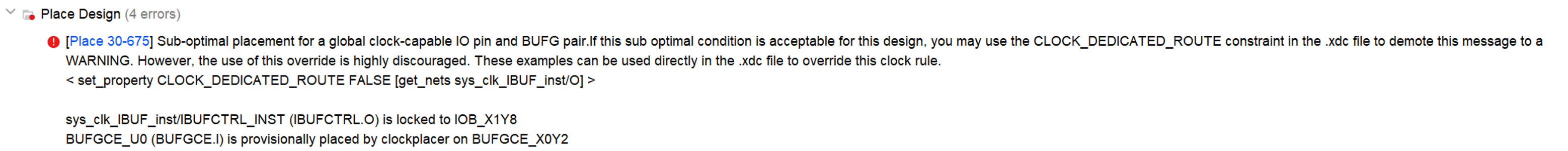

[Place 30-675] Sub-optimal placement for a global clock-capable IO pin and BUFG pair

解决方法步骤:

1.使用BUFGCE接收HD BANK的输入时钟

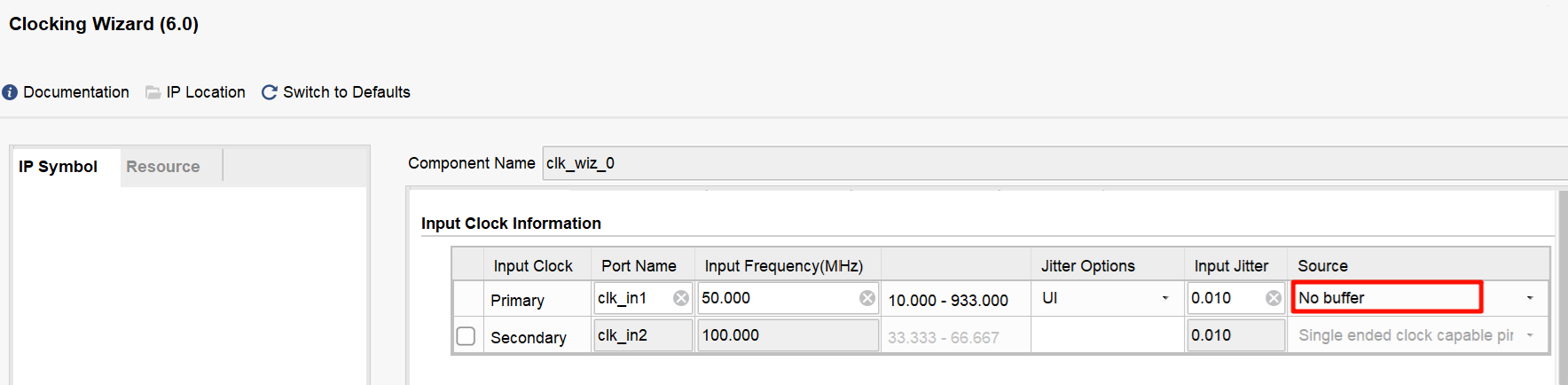

2.将Clocking Wizard的输入时钟设置为 No buffer

3.在XDC文件中加入以下约束:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets sys_clk_IBUF_inst/O]

BUFGCE

BUFGCE_U0 (

.O(sys_clk_in), // 1-bit output: Buffer

.CE(1'd1), // 1-bit input: Buffer enable

.I(sys_clk) // 1-bit input: Buffer

);

PS:ADM官网对于该问题的回复链接如下:

本文讲述了在使用XilinxVivado2022.2进行设计时,用户遇到在Windows11系统下综合阶段及布局布线阶段的Aurora6466BIP核引脚错误,特别提及自Vivado2020版本起,对WIN7系统的支持已被终止。

本文讲述了在使用XilinxVivado2022.2进行设计时,用户遇到在Windows11系统下综合阶段及布局布线阶段的Aurora6466BIP核引脚错误,特别提及自Vivado2020版本起,对WIN7系统的支持已被终止。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?