目录

一、Radix-4 Booth乘法器原理

上文中介绍了基2 Booth乘法器,本文继续介绍基4 Booth乘法器。

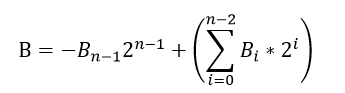

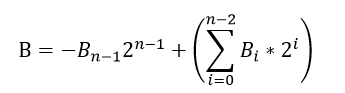

对于N比特数B来说:

N比特数B,将其展开,其中B-1=0:

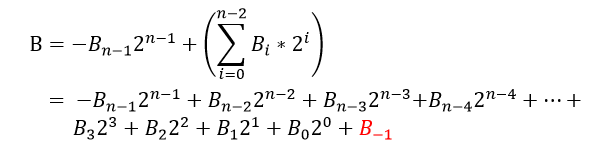

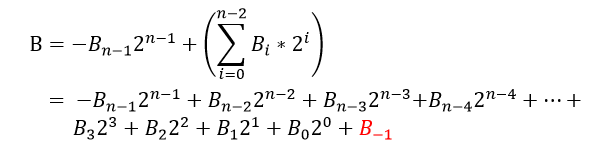

基2 Booth表示为:

其基系数为:

![]()

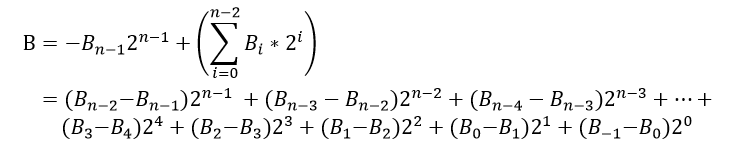

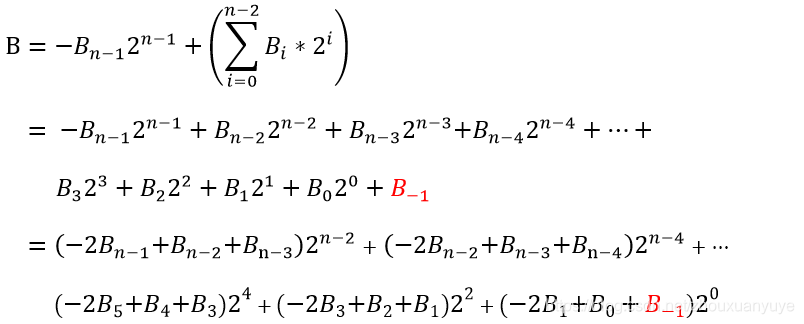

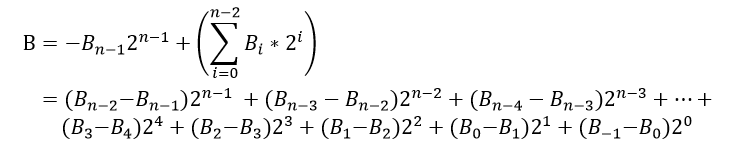

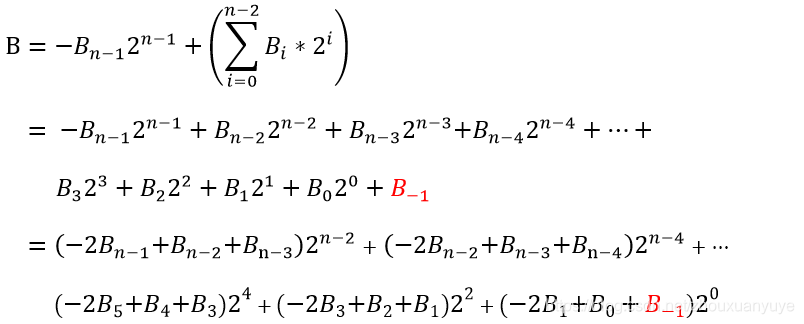

基4 Booth乘法器的基系数为:

![]()

所以,上式B可以重写为如下式(位宽为偶数):

将A与B相乘,则:

目录

上文中介绍了基2 Booth乘法器,本文继续介绍基4 Booth乘法器。

对于N比特数B来说:

N比特数B,将其展开,其中B-1=0:

基2 Booth表示为:

其基系数为:

![]()

基4 Booth乘法器的基系数为:

![]()

所以,上式B可以重写为如下式(位宽为偶数):

将A与B相乘,则:

4321

4321

8508

8508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?