目录

一、数的表示及乘法的范围

对于n比特数B,其二进制数转换为有符号十进制整数的公式如下:

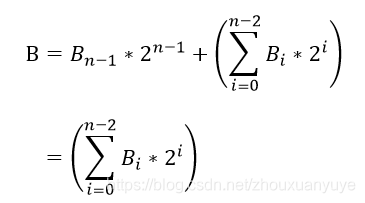

当B>=0,B的第n-1比特为0,则B可用下式表示:

设n=4,“5”的二进制位为0101,则5 = 1*4 + 1*1。

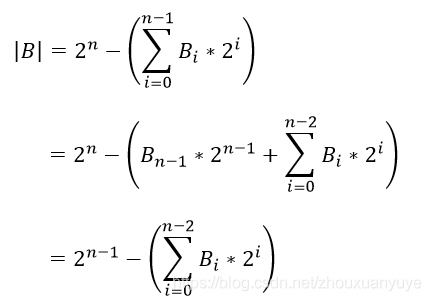

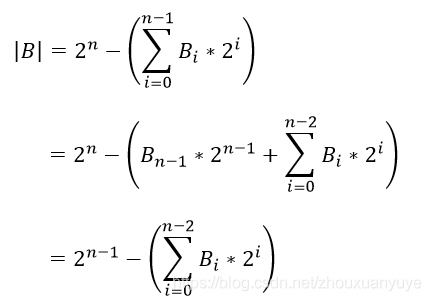

当B<0时,B的第n-1比特为1,B已为补码表示。

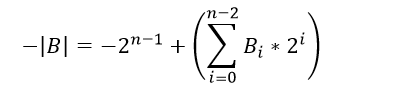

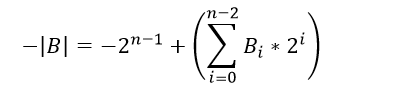

所以-|B|表示如下:

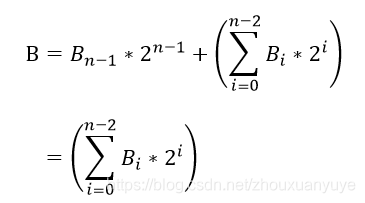

综上所述,有符号数与无符号与十进制的转换表示可统一为如下格式:

目录

对于n比特数B,其二进制数转换为有符号十进制整数的公式如下:

当B>=0,B的第n-1比特为0,则B可用下式表示:

设n=4,“5”的二进制位为0101,则5 = 1*4 + 1*1。

当B<0时,B的第n-1比特为1,B已为补码表示。

所以-|B|表示如下:

综上所述,有符号数与无符号与十进制的转换表示可统一为如下格式:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?