目录

Sklansky加法器是另一种并行高速的树形加法器,由Sklansky于1959年发表,该加法器对比特位进位层级分组,根据对不同比特组所有可能的进位计算所有可选的和与进位,所以也叫Conditional-Sum Addition。

一、进位选择加法器

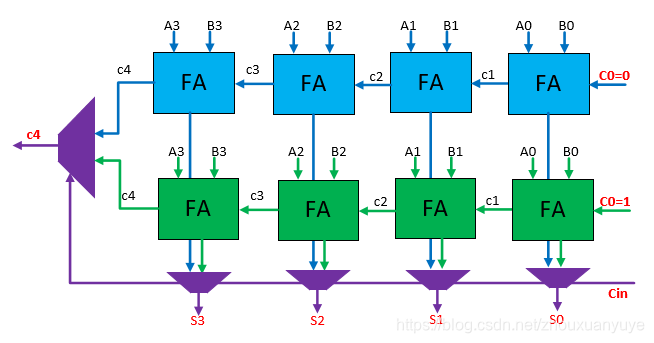

Sklansky加法器使用了进位选择加法器:

- 进位选择加法器由2个行波进位加法器和1个选择器构成

- 其中一个行波进位加法器假定进位进位为0

- 另外一个行波进位加法器假定进位为1

其结构如下:

更多详细参考往期文章:https://zhuanlan.zhihu.com/p/102207162

我们先看下Sklansky在其论文中的一个进位选择加法器的例子(只取低8位部分做详细,如果阅读论文时,对于其表格数据由来不明的话可以细看以下部分):

x = 0 1 1 0 1 1 0 1

y = 1 0 1 1 0 1 1 0

第一级:

本文介绍了Sklansky加法器的工作原理,通过进位选择加法器的分组计算,展示了从低8位部分的详细设计过程,并提供了Verilog实现方案,以16比特为例,阐述了如何构建树形结构的Sklansky加法器。

本文介绍了Sklansky加法器的工作原理,通过进位选择加法器的分组计算,展示了从低8位部分的详细设计过程,并提供了Verilog实现方案,以16比特为例,阐述了如何构建树形结构的Sklansky加法器。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1128

1128

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?