这里不再阐述QPSK的原理直接详细介绍基于FPGA的QPSK实现

输入输出信号

module QPSK_top(

input clk,

input rst,

input [1:0]data_send,

output [35:0] qpsk

);

其中定义随机信号data_send的产生来自由matlab随机产生的数据文件定义。

后面在介绍在仿真所用的tb文件进行读取相应文件进行仿真。

信号对极化

wire [1:0]I;

wire [1:0]Q;

//对极化 :0——>+1(01) 1——>-1(11)

assign I ={

data_send[0],1'b1};

assign Q ={

data_send[1],1'b1};

上采样&成型滤波

reg [3:0] cnt_16 = 4'b00;//16计数器,内插系数是16(时钟速率是符号速率的4倍)

always @(posedge clk)

begin

if(rst) begin

cnt_16<=4'b00;

end else begin

cnt_16 <= cnt_16+1'b1;

end

end

wire fir_nd; //输入FIR滤波器有效信号

assign fir_nd = (cnt_16 == 4'd15);

wire [23:0] I_filtered;

wire [23:0] Q_filtered;

wire [15:0] carry_cos;

wire [15:0] carry_sin;

//I路成形滤波

rcosfilter rcosfilter_I (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(fir_nd), // 输入I路有效信号

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata({

6'd0,I[1:0]}), // input wire [7 : 0] s_axis_data_tdata {6{I[1]}}

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(I_filtered) // output wire [23 : 0] m_axis_data_tdata

);

//Q路成形滤波

rcosfilter rcosfilter_Q (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(fir_nd), // 输入Q路有效信号

.s_axis_data_tready(), // output wire s_axis_data_tready

.s_axis_data_tdata({

6'd0,Q[1:0]}), // input wire [7 : 0] s_axis_data_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(Q_filtered) // output wire [23 : 0] m_axis_data_tdata

);

这里设置内插系数为16 ,通过16位计数器的方式控制成型滤波器的使能,进而实现上采样

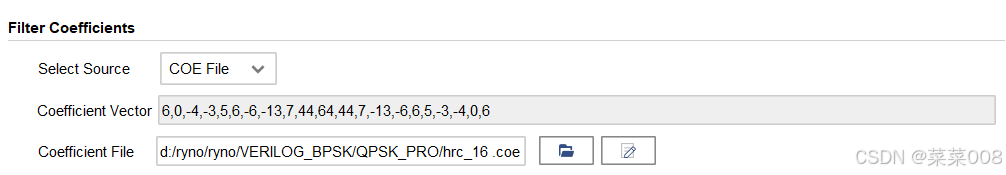

滤波器的IP核设置

两路的成型滤波器用到了【FIR Compiler】滤波器IP核,根据各参数进行设置

配置过程如下:

本文只简单介绍主要配置,具体IP核每项配置的含义和设置可以参照手册或文章

1、选择coe文件

coe文件对应要设置的滤波器系数,上面的文件名hrc_16.coe的16指的是量化系数16

可以从matlab得到

clc

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

443

443

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?