1. 现象描述

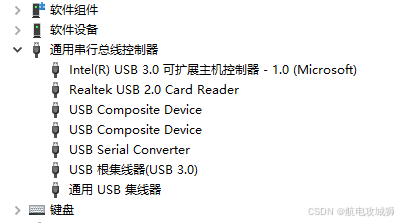

1) 电脑设备管理器显示驱动已经安装成功:

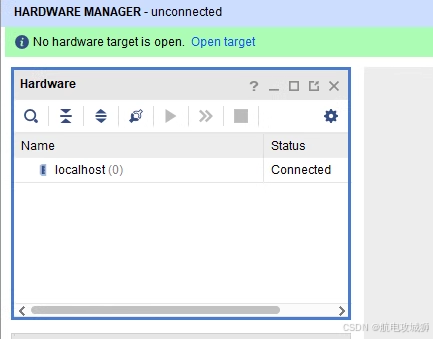

2) vivado Hardware Manager页面读取不到FPGA芯片

2. 问题解决

这种情况多半是在安装VIVADO软件时没有同时安装对应JTAG下载器驱动软件或没有提示安装对应下载器的安装软件。

可以按照如下步骤解决:

1) 运行该程序前,先确保下载器已经从电脑端口拔下来了。

2) 进入目录:“C:\Xilinx\Vivado\xxxxx\data\xicom\cable_drivers\nt64\digilent\install_digilent.exe”文件,并在需要的时候勾选所有勾选项以手动安装下载器服务程序。

3) 安装FTDI官方提供的驱动软件:CDM212364_Setup.zip

2630

2630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?