目录

主要介绍内容:

1、网络协议

2、PHY芯片应用

3、RGMII与GMII接口

4、程序设计

5、实验测试

1、网络协议

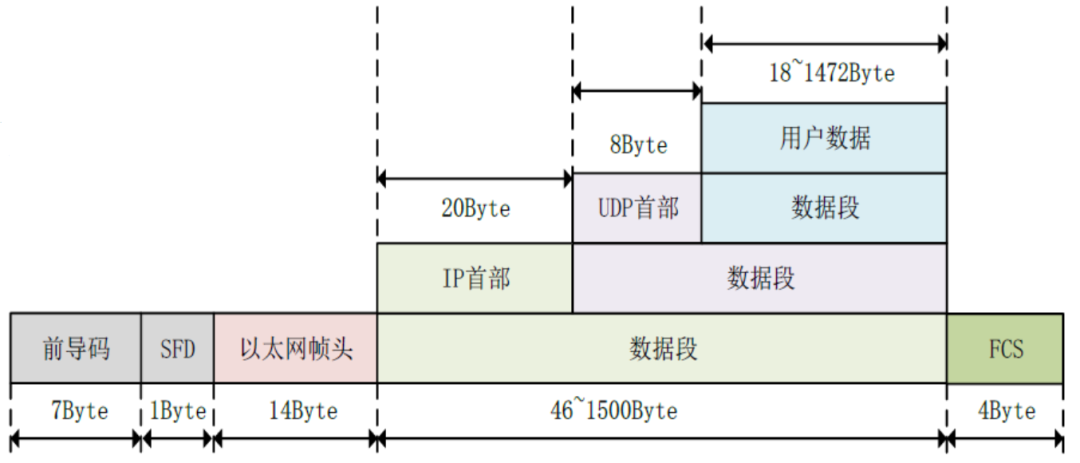

以太网是一种通信协议,目前应用最广泛的局域网通讯方式。以太网协议定义了一系列软硬件标准,从而将不同的设备连接通信;以数据包/帧的形式传输,每包数据量在几十到上千个字节。

对于FPGA应用以太网通信,目前应用最多的是千兆网和万兆网通信;实现不同的通信速率主要借助于不同的硬件接口,千兆网主要通过PHY芯片和光口两种方式实现,万兆网主要通过光口实现。由于FPGA没有协议库,需要开发者了解各类协议,开发需求对应的协议栈。

IEEE 802.3链路层协议如下:

| 前导码 | SFD | 目的MAC | 源MAC | 长度/类型 | 数据 | FCS |

| 7Byte | 1Byte | 6Byte | 6Byte | 2Byte | 4Byte |

前导码:实现数据的同步,固定值56'h55_55_55_55_55_55_55;

帧起始界定符:表示一帧的开始,固定值8'hD5;

目的MAC:接收端物理MAC地址,MAC地址分为单播地址、组播地址和广播地址;

源MAC:发送端物理MAC地址;

长度/类型:取决于后续部分全是数据还是包含数据包协议。比如对于LLC帧,该2字节表示后续数据部分的长度;对于MAC帧,该2字节表示协议类型,比如ARP(0x0806)、IP(0x0800)。当这两个字节的值小于0x0600时,表示LLC帧数据段的长度;如果大于0x0600,则表示该数据属于哪个上层协议。

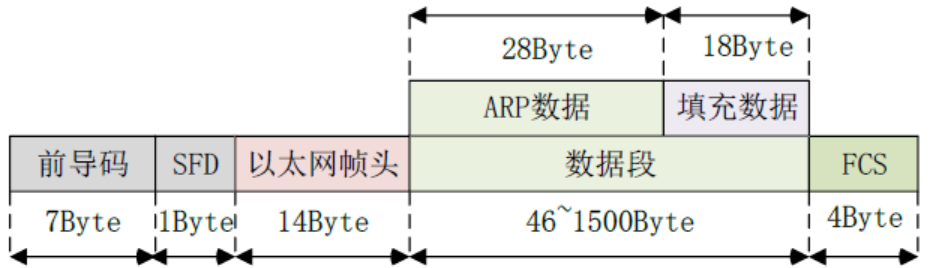

数据:传输的内容,例如IP数据包、ARP包、LLC帧数据内容等;长度不足46字节需要填充补足;数据段长度最小46个字节,最大1500个字节;

FCS帧校验序列:校验数据帧是否传输错误,通过CRC算法生成;CRC数据校验从以太网帧头开始(不包含前导码和帧起始界定符)到数据部分结束。

IFG帧间隙:相邻两帧之间的时间间隔,IFG的最小值是96bit的传输时间。

由于LLC帧结构较为简单,FPGA应用场景使用该协议也较少,本文不再分享该部分的协议;FPGA网络通信使用较多的协议为:ARP、IP、ICMP、UDP、TCP。

1.1 ARP协议

在以太网通信中,网卡接收和解析网络包,当解析到目的MAC地址非本地MAC地址时,则直接丢弃该包数据,因此在通信前需要先获得目的MAC地址。获取对方MAC地址的方式是由ARP协议完成的。

ARP(Address Resolution Protocol)地址解析协议,是根据IP地址获取MAC地址的一种TCP/IP协议。ARP协议分为ARP请求和ARP应答,源主机发起查询目的MAC地址的报文称为ARP请求,目的主机响应源主机并发送含本地MAC地址的报文称为ARP应答。

ARP请求报文:包含了发送方的MAC地址和IP地址以及接收方的IP地址;此时目的MAC为广播地址48’hff_ff_ff_ff_ff_ff。发送目的MAC地址为广播地址,局域网中的所有主机都会进行接收并处理ARP请求报文,验证目的IP地址是不是自己的地址。只有匹配本机时发送ARP应答报文,应答报文包含接收方的IP地址和物理地址。发送端主机将收到的ARP应答报文中的源MAC地址解析出来,将MAC地址和目的IP地址更新至ARP缓存表中,当再次通信时,可以直接从ARP缓存表中获取对方MAC地址。

ARP数据包所在帧结构如下:

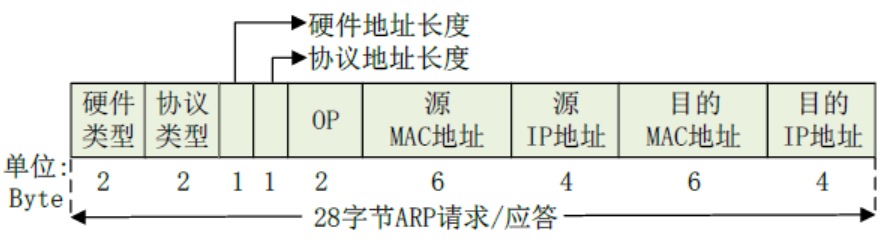

ARP协议如下:

硬件类型:硬件地址的类型,1表示以太网地址;

协议类型:要映射的协议地址类型,值0x0800;

硬件地址长度:MAC地址的长度,字节单位,该值为6;

协议地址长度:IP地址的长度,字节单位,该值为4;

OP操作码:1表示ARP请求,2表示ARP应答;

源MAC地址:发送端的硬件地址MAC;

源IP地址:发送端的协议IP地址;

目的MAC地址:接收端的硬件地址;在ARP请求报文中此值为广播MAC地址;

目的IP地址:接收端的IP地址。

1.2 IP协议

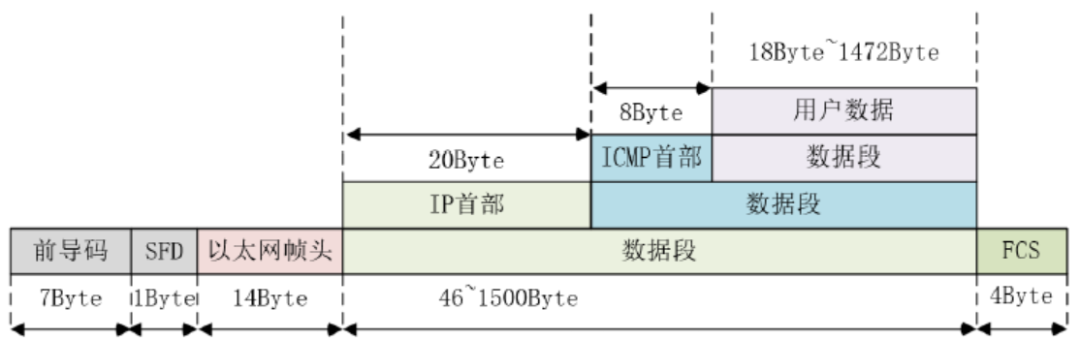

IP协议是TCP/IP协议簇中的核心协议,IP协议位于以太网MAC帧格式的数据段,IP协议内容由IP首部和数据段组成。所有的TCP、UDP及ICMP数据都以IP数据格式传输,IP数据报文结构如下:

IP首部:20字节固定部分+可有可无的可选字段;

IP数据:取决于协议字节内容,为具体的协议报文,如TCP、UDP、ICMP等;

| 中文名 | 英文名 | 长度bit | 含义 |

| 版本 | Version | 4 | 版本号,0x4:IPv4,0x6:IPv6 |

| 首部长度 | IHL | 4 | IP首部一共有多少个32位;在没有可选字段时,该值为0x5; |

| 服务类型 | TOS | 8 | 默认0,一般服务 |

| 总长度 | Total Length | 16 | IP 首部和IP 数据部分总字节数 |

| 标识 | ID | 16 | 报文的唯一标识,一般每发送+1 |

| 标志 | Flag | 3 | 是否分片的标志。 第1位为保留位; 第2位表示禁止分片(1表示不分片 0:允许分片); 第3位标识更多分片(1:后面还有分片,0:最后一个) |

| 片偏移 | Fragment Offset | 13 | 分片在原分组中的相对位置,以8字节为偏移单位 |

| 生存时间 | TTL | 8 | 可以经过的最多路由器数,默认64或128 |

| 协议 | Protocol | 8 | 封装的协议类型: ICMP(1)、IGMP(2)、TCP(6)、UDP(17) |

| 首部校验和 | Header Checksum | 16 | IP首部校验和,按16bit求和,结果使用二进制反码 |

| 源IP地址 | Source Address | 32 | 发送端的IP地址 |

| 目的IP地址 | Destination Address | 32 | 接收端的IP地址 |

| 可选字段 | Options | 可变 | 主要用于测试,确保首部长度为 4 字节的整数倍 |

| 数据 | Data | 报文数据部分 |

1.3 ICMP协议

ICMP(Internet Control Message Protocol)网络控制报文协议,属于IP协议的一个子协议,用于测试设备间的网络通不通、主机是否可达、路由是否可用等网络本身的消息。

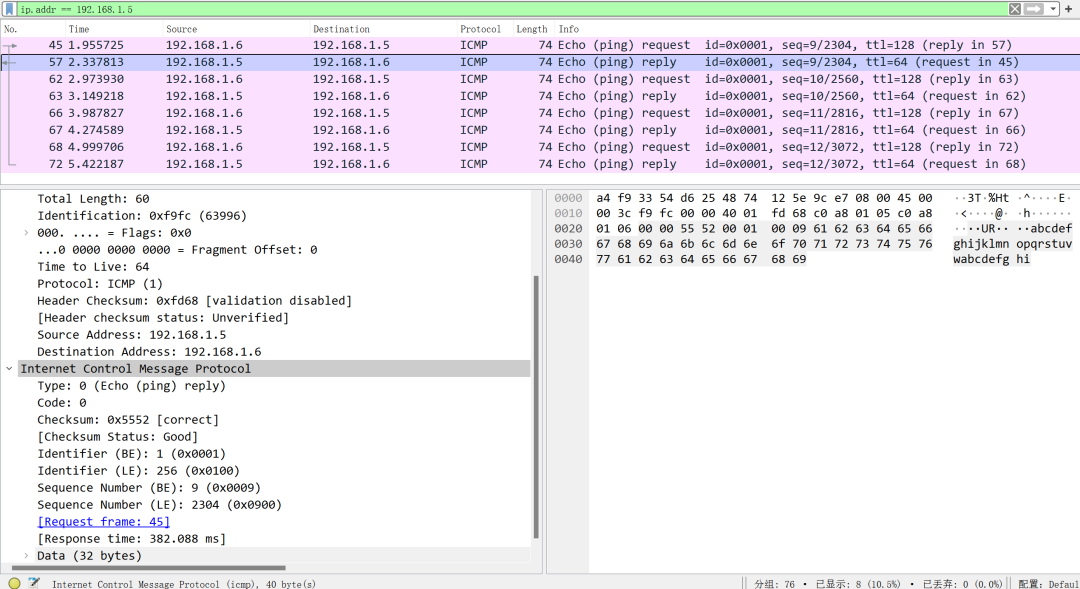

ICMP数据包所在帧结构如下:ICMP报文封装在IP报文中

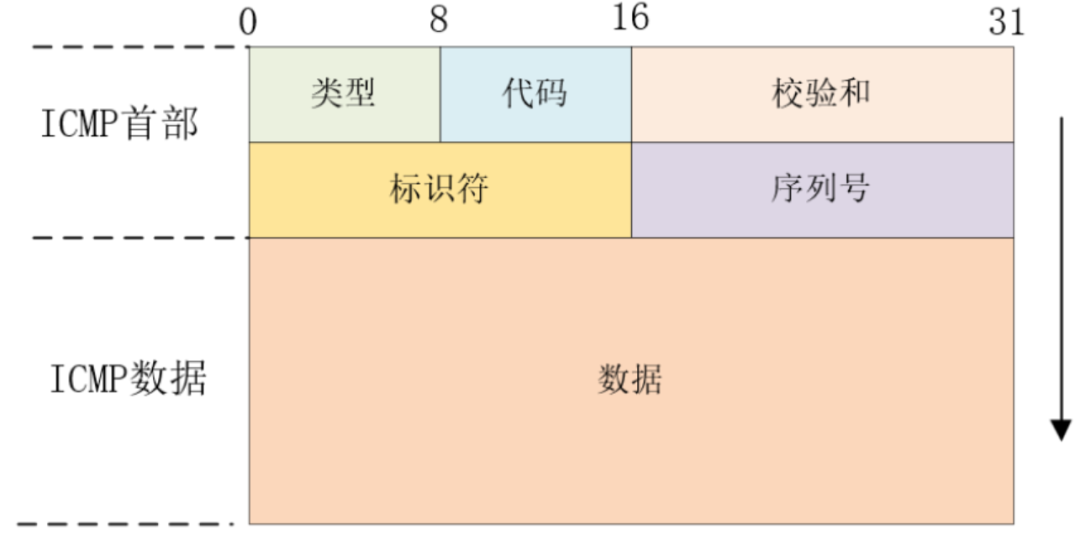

ICMP协议内容如下:

ICMP首部共8个字节;

类型(type):8bit,表示ICMP报文类型;

代码(code):8bit,它与类型字段一起共同标识了ICMP报文的详细类型;

常用的:类型0,代码0:表示回显应答(ping应答);类型8,代码0:表示回显请求(ping请求);类型11,代码0:超时;类型3,代码0:网络不可达;类型3,代码1:主机不可达;类型5,代码0:重定向。

校验和(checksum):占2字节,对包括ICMP报文数据部分在内的整个ICMP数据报的校验和,以检验报文是否有错误。

标识符(Identifier):16bit,对每一个发送的数据报进行标识。

序列号(Sequence number):16bit,对于发送的每一个数据报文进行编号,比如:发送的第一个数据报序列号为1,第二个序列号为2。

数据(Data):发送的ICMP数据。对于ping应答报文中的Data就是ping 请求报文所发送的ICMP 数据报文里的数据部分。

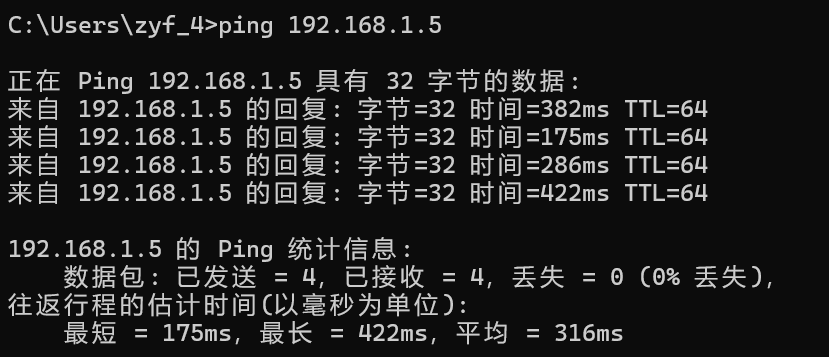

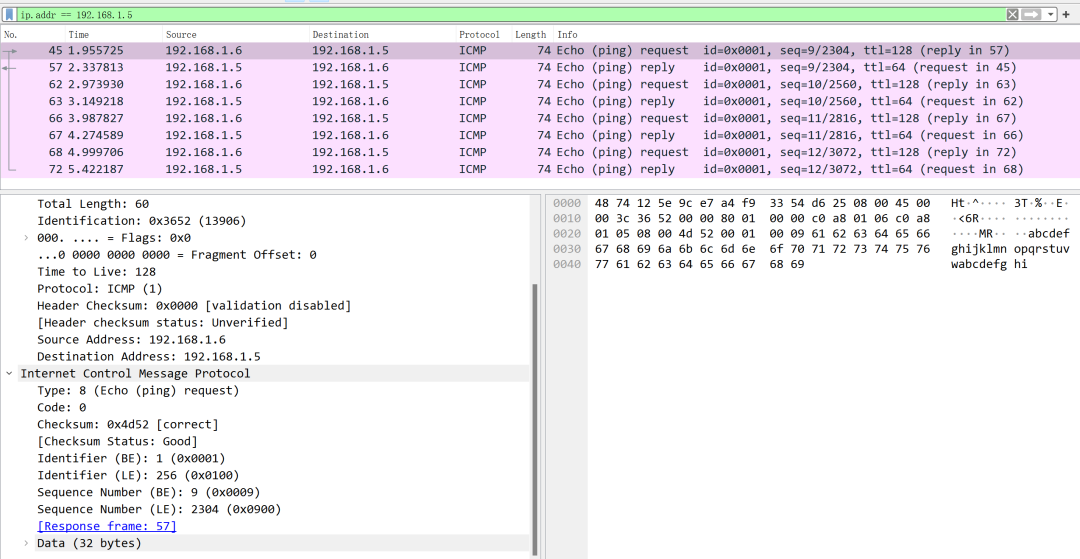

以wireshark为例进行分享ICMP报文具体内容:

第一个ping请求报文:

第一个ping应答报文:

1.4 UDP协议

UDP是一种面向无连接的传输层协议,封装于IP协议内,常应用于实时性高等网络通信场景中。

UDP数据段所在帧结构如下:

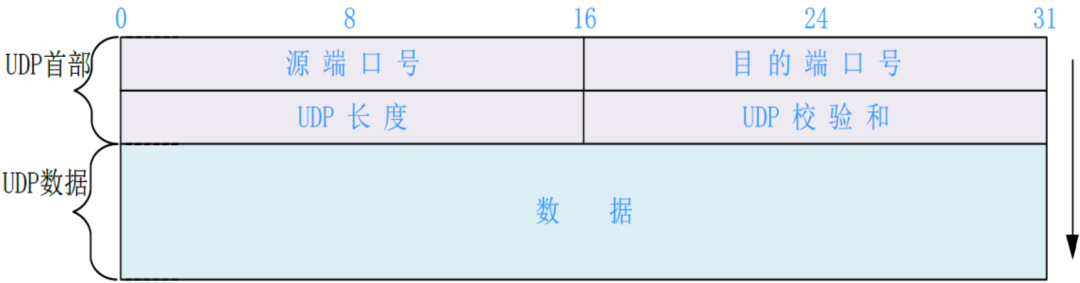

UDP数据段具体内容如下:

UDP首部共8个字节;

UDP数据:18~1472字节;

源端口号:16位,发送端端口号,区分不同服务的端口;

目的端口号:16位,接收端端口号;

UDP长度:16位,包含UDP首部和数据总长度,单位是字节;

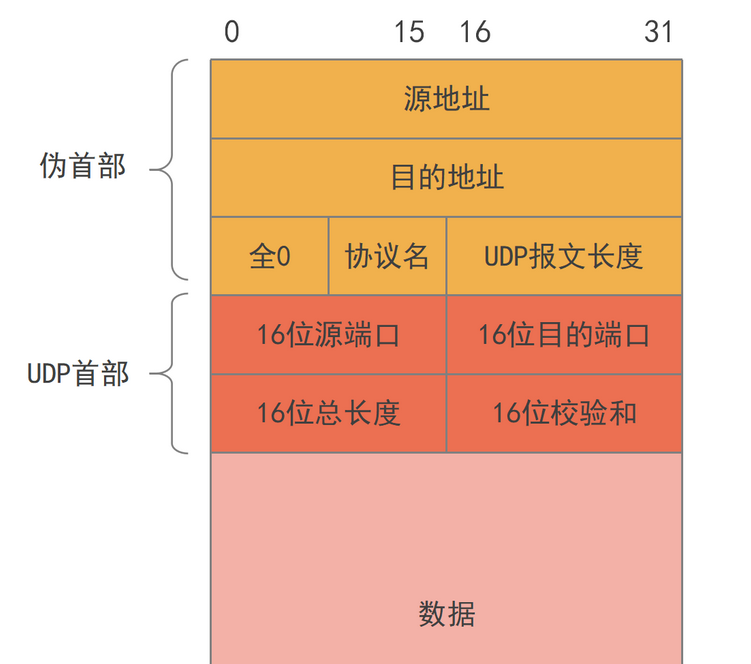

UDP校验和:16位,计算方法:16位相加,结果取反;检验数据含三个部分:UDP伪首部,UDP首部和UDP数据部分。伪首部的数据包括源IP地址,目的IP地址,协议类型和UDP长度。在大多数使用场景中接收端并不检测UDP 校验和,发送端也可不计算校验和。

计算校验和的数据:

2、PHY芯片介绍

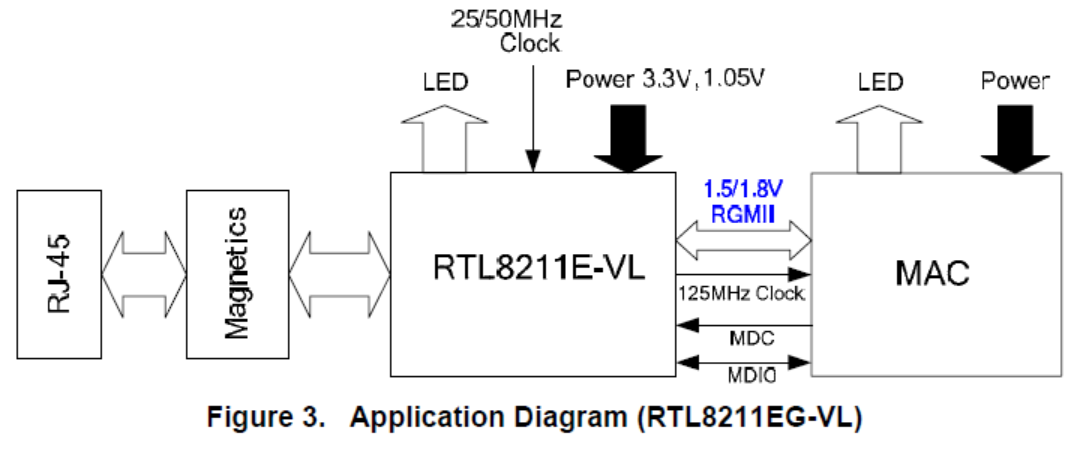

千兆网通信应用最多的一种方式,使用PHY芯片,通过连接RJ45插座、插头开放网线接口。千兆网光纤接口的使用本文暂不介绍。

2.1 PHY芯片

对于千兆以太网通信中,设备之间的物理层链路主要由PHY芯片建立;以太网接口电路主要由MAC(Media Access Control)控制器和物理层接口PHY(Physical Layer,PHY)两大部分构成。对于FPGA设计来说,MAC控制器由FPGA实现,PHY芯片指开发板的以太网芯片。

PHY芯片在发送数据的时候,接收MAC发过来的数据,把并行数据转化为串行数据,按照物理层的编码规则把数据编码转换为模拟信号发送出去,接收数据的过程相反。

PHY还提供了其他功能,可通过LED灯显示连接状态和工作状态;具有自协商功能:互相协商并确定连接速度、双工模式、是否采用流控等,采用两个设备中能同时支持的最大速度和双工模式。

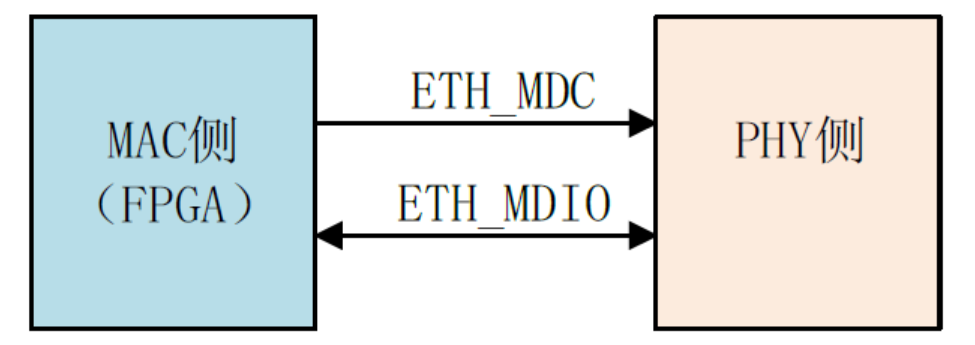

2.2 PHY芯片的配置

PHY芯片有一个配置接口MDIO,PHY芯片内部包含一系列寄存器,可配置其工作模式、获取状态信息,如连接速率、双工模式、自协商状态,时钟相对数据的延时、流量控制等。

PHY芯片在默认状态下是可以正常工作的,对MDIO接口的配置不是必须的。

FPGA配置PHY的模式:

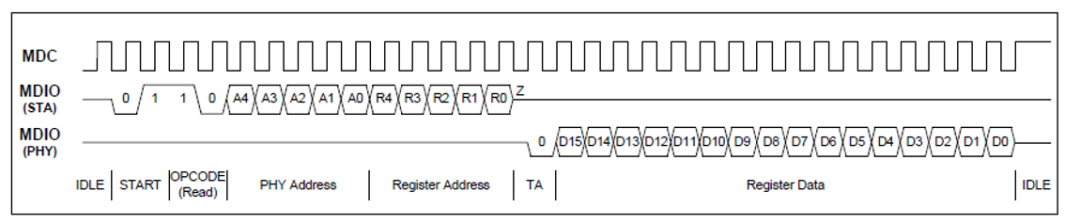

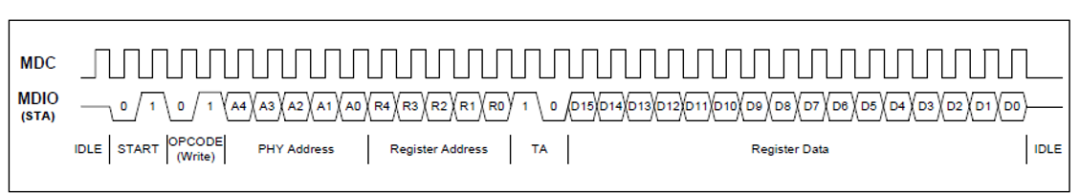

MDC为配置时钟,一般不超过12.5MHz;MDIO为双向数据引脚,用于读写寄存器。

比如我开发板上的PHY芯片为RTL8211-VL,其应用方法如下:

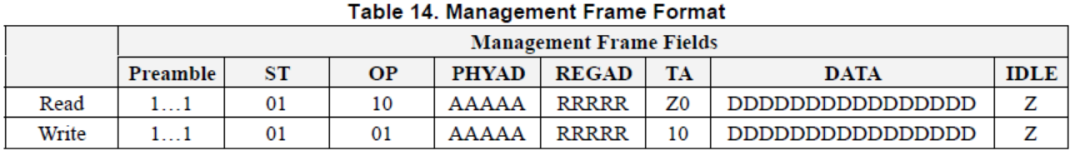

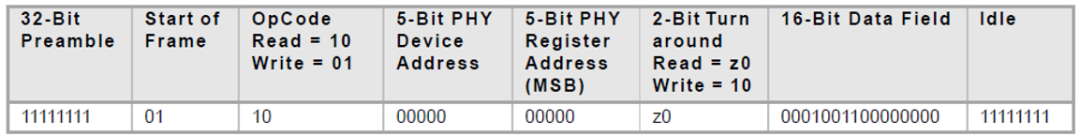

MDIO读写协议如下:

Preamble:32位前导码,全1,同步PHY芯片;

ST(Start of Frame):2位帧开始信号,固定值01

OP(Operation Code):2位操作码,读:10 写:01;

PHYAD(PHY Address):5位PHY地址,支持默认地址0和具体电图PIN地址;

REGAD(Register Address):5位寄存器地址;

TA(Turnaround):2位转向读写,读操作与写操作值不同;

DATA:16位数据,寄存器的读写值;

IDLE:空闲状态,默认全1;

读操作如下:

写操作如下:

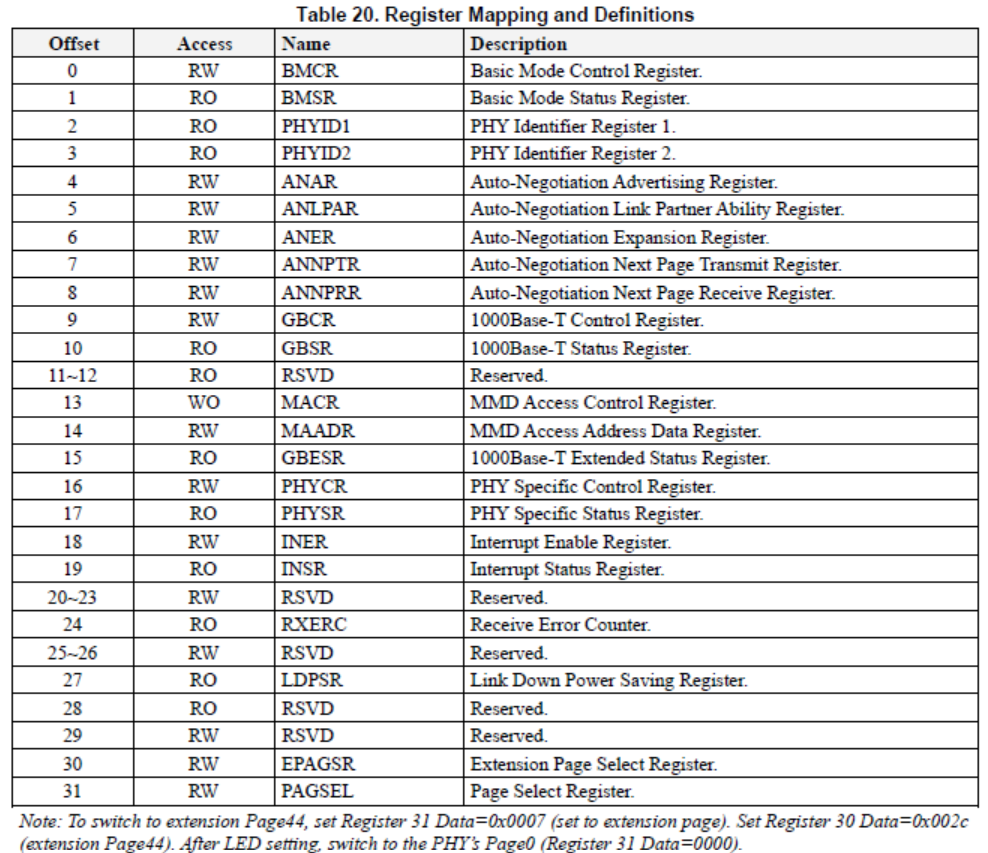

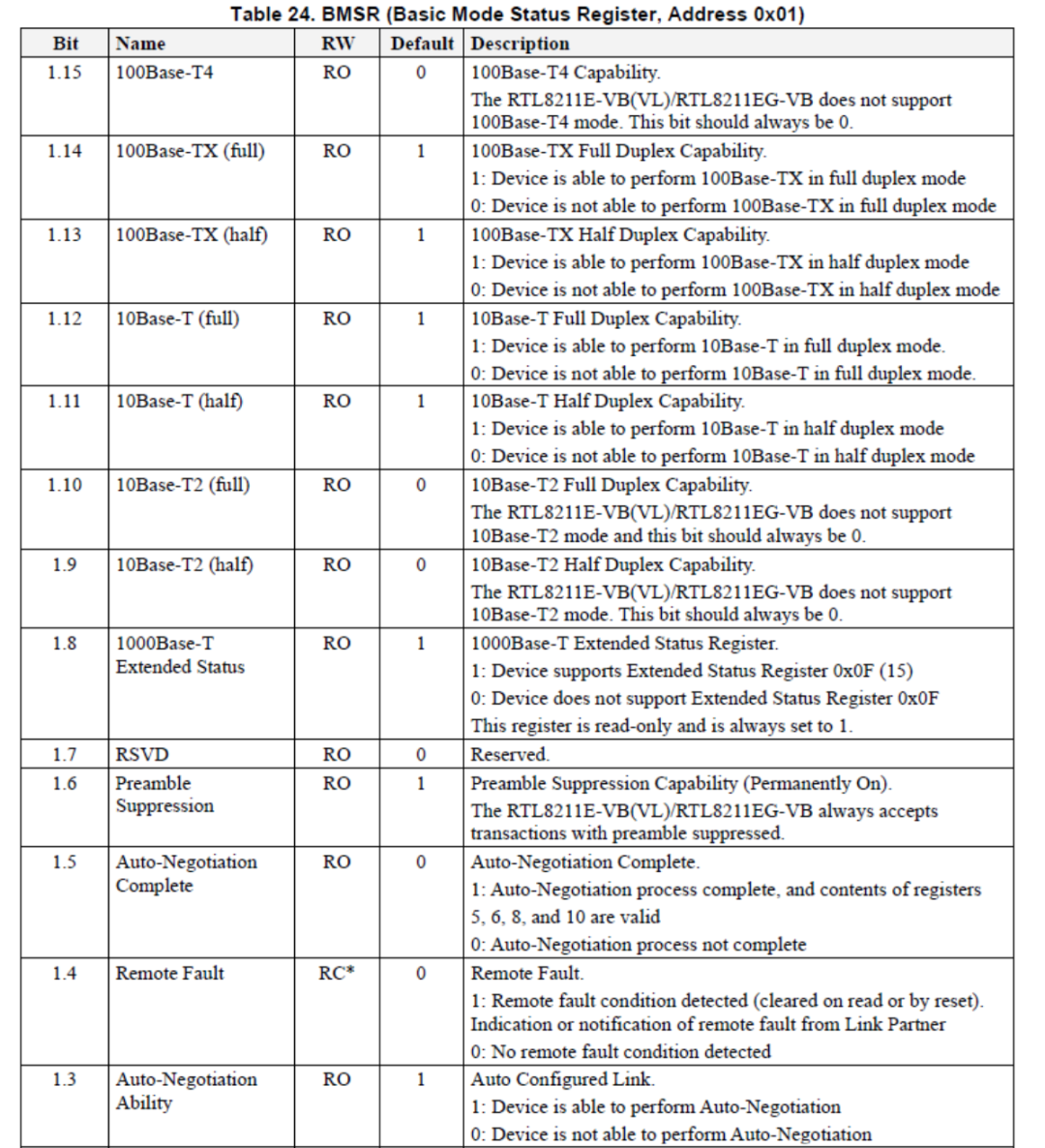

该型号RTL8211片子的寄存器如下:

对于前32#寄存器,直接进行读写即可。对于其他page寄存器的读写需要进行如下操作:31号寄存器进行Page选择,在进入寄存器30配置具体page号,之后进行具体读写。

2.3 RGMII与GMII接口转换

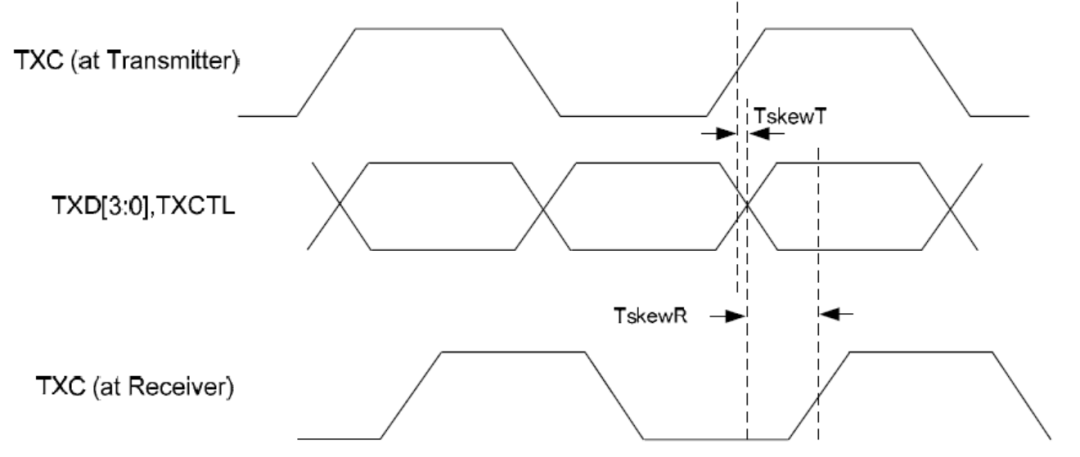

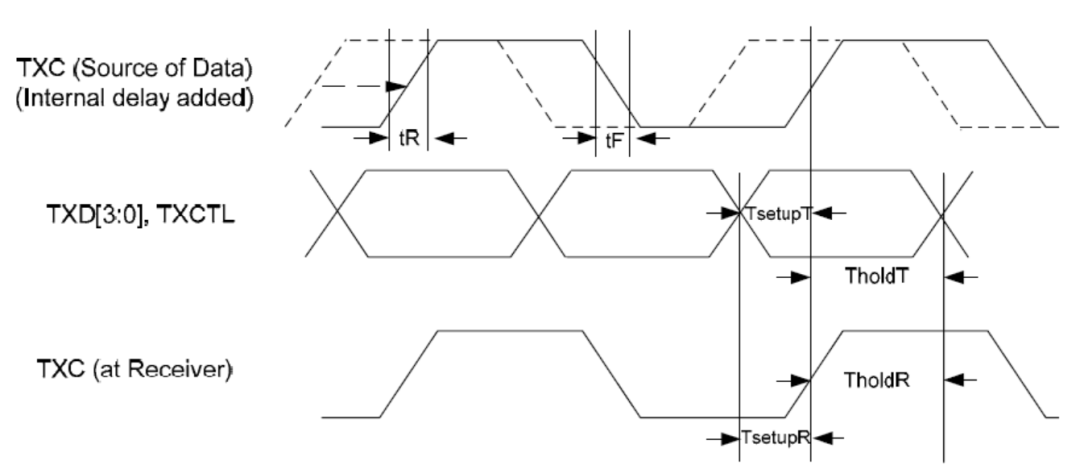

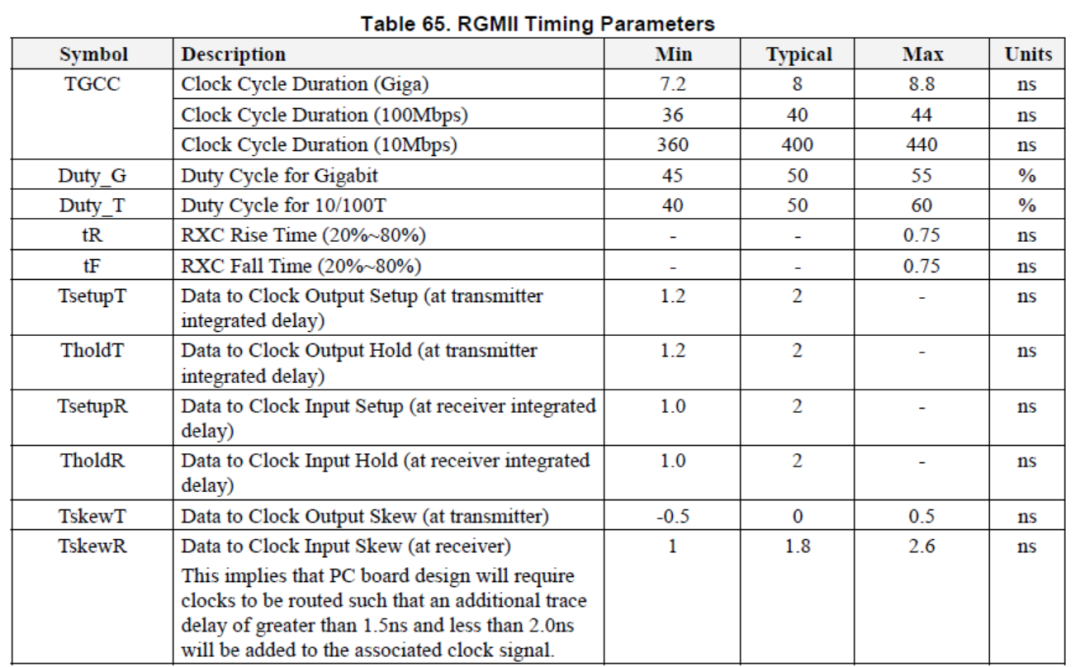

PHY芯片的时钟与数据接口为RGMII接口,RGMII可适用于1000M、100M、10M三种速率;其收发时序如下:

RGMII时序调整的可行方式:1、电路接法,2、寄存器配置,3、时钟移相。调试过程中出现误码时,可考虑这方面。

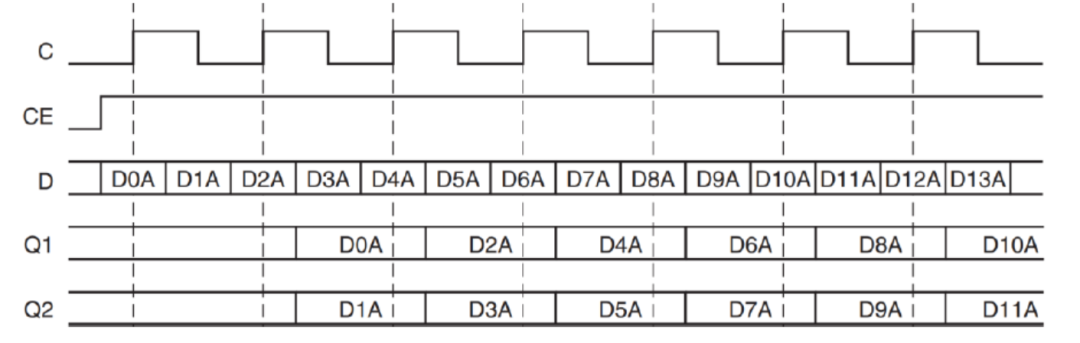

RGMII是时钟双沿数据形式DDR;FPGA用户侧数据需要转换为单沿时钟数据,该类型的接口为GMII接口。RGMII信号:双沿传输;GMII信号:单沿传输。

对于Xilinx FPGA而言,单双沿数据转换主要通过源语实现;7系列和UltraScale及以上的实现有一些差异;

7系列FPGA:利用BUFG、BUFIO、IDDR及和IDELAYE2和IDELAYCTRL、ODRR;

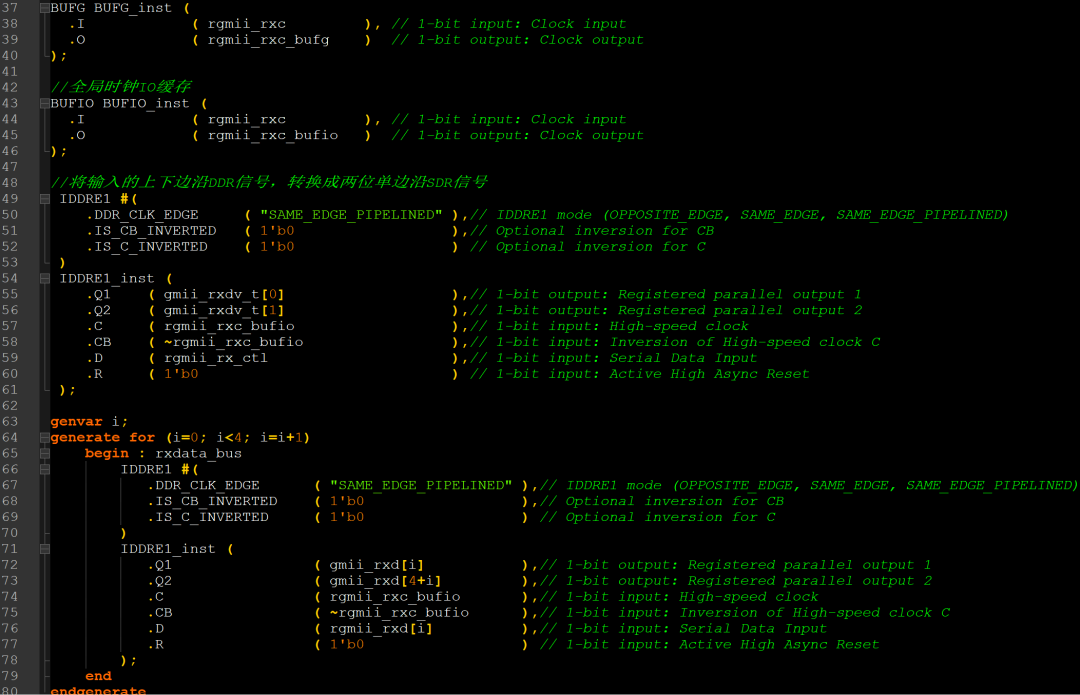

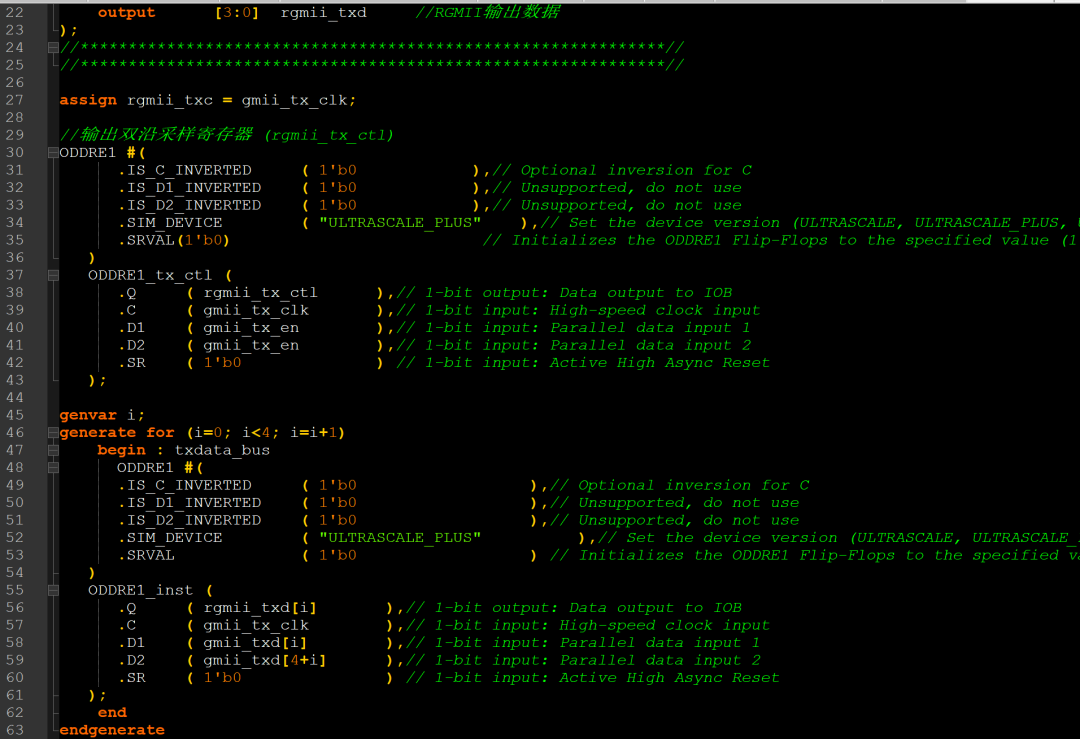

UltraScale/+:利用BUFG、BUFIO、IDDRE1、ODDRE1;

3 、程序设计

整体工程如下:

3.1 PHY芯片配置

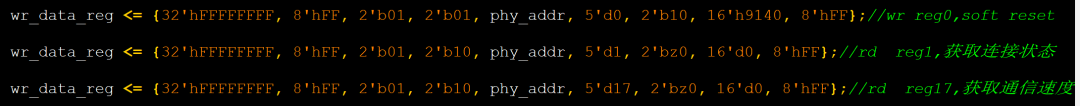

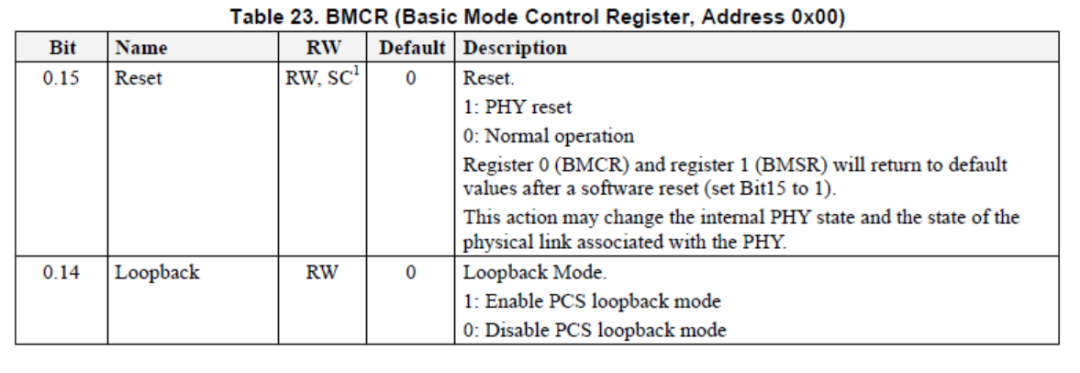

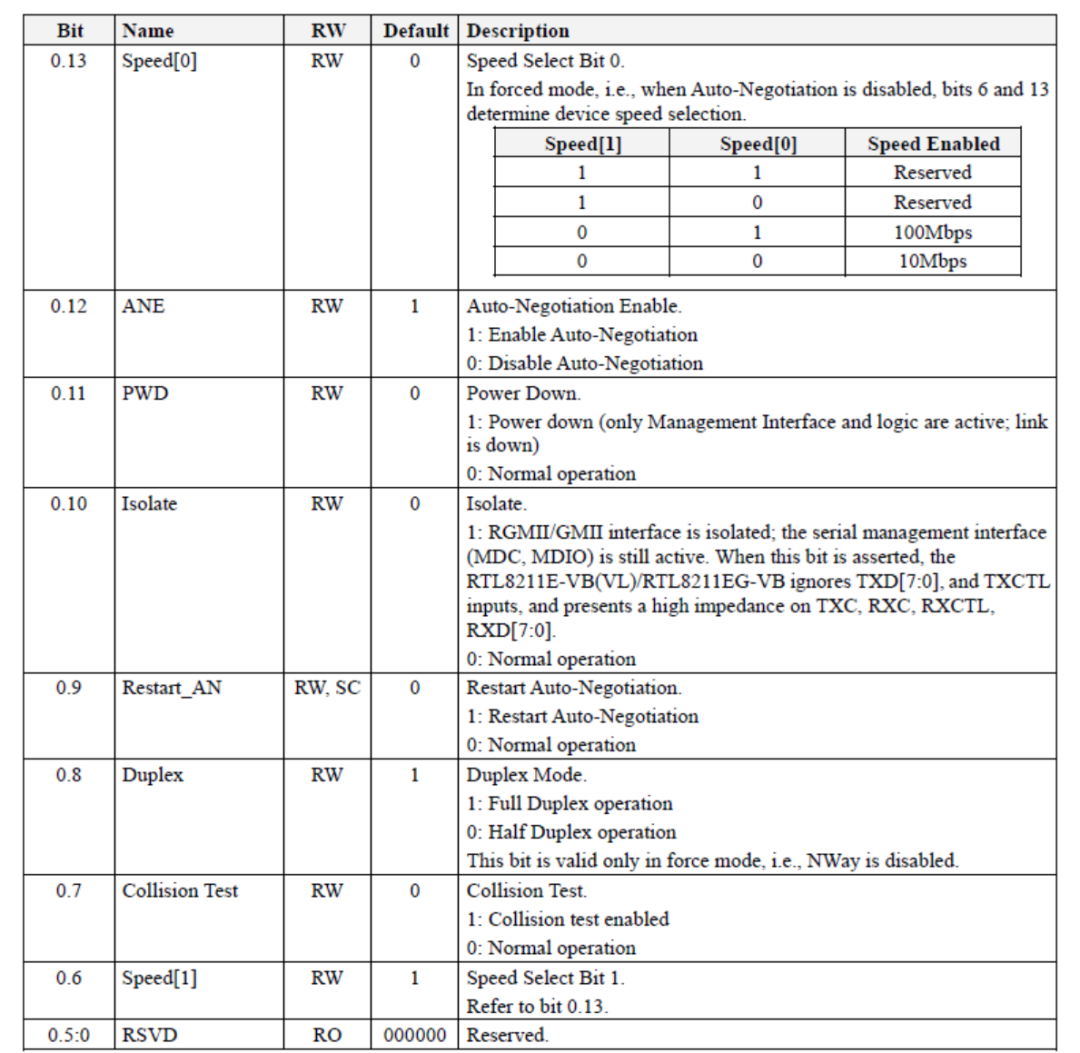

按照Datasheet进行编码寄存器的读写,本次实验进行寄存器0的软复位且使能自动协商功能,读寄存器1的基本状态和寄存器17的连接速率和连接状态。

其中寄存器0如下:

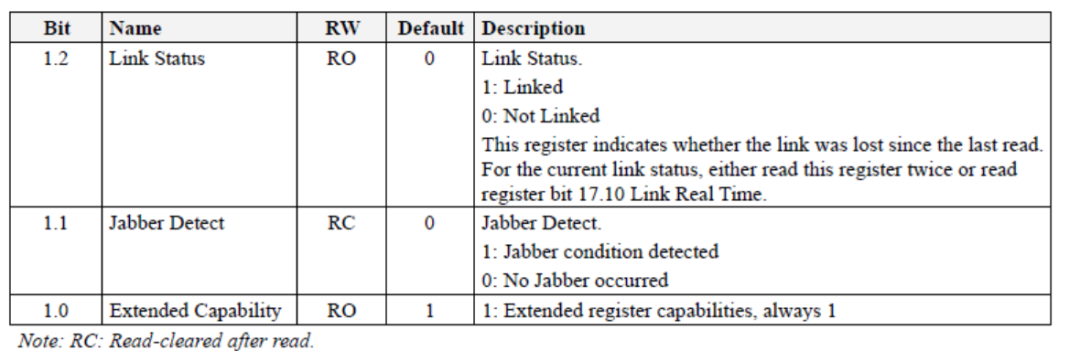

寄存器1只读:

寄存器17:

3.2 RGMII与GMII转换设计

由于本次开发板为UltraScale,因此采用该系列的IDDRE1和ODDRE1源语:

实现输入双沿数据到单沿功能如下:

3.3 UDP协议栈

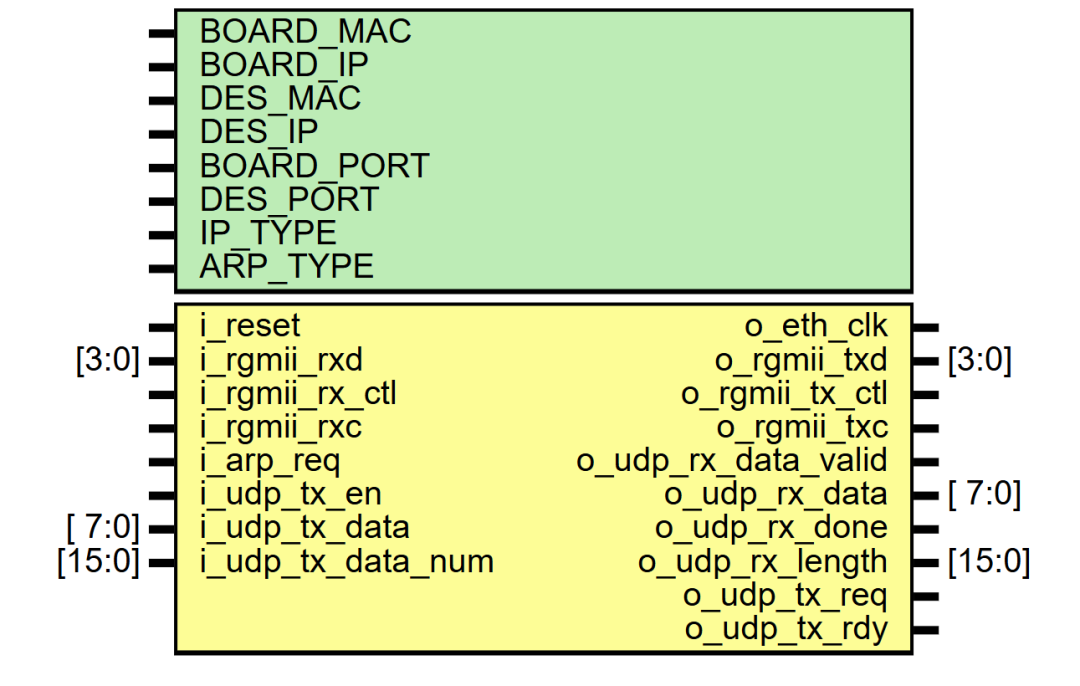

模块主要接口如下:

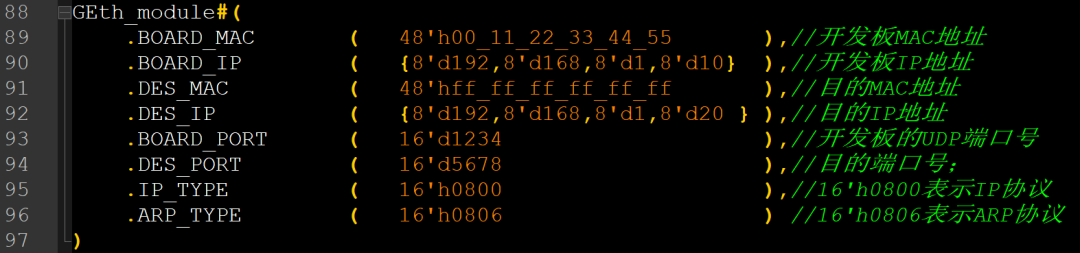

参数配置(两端MAC、IP、UDP层相关):

端口:RGMII接口、UDP收发端数据相关、arp请求触发;

本次实验例化配置:

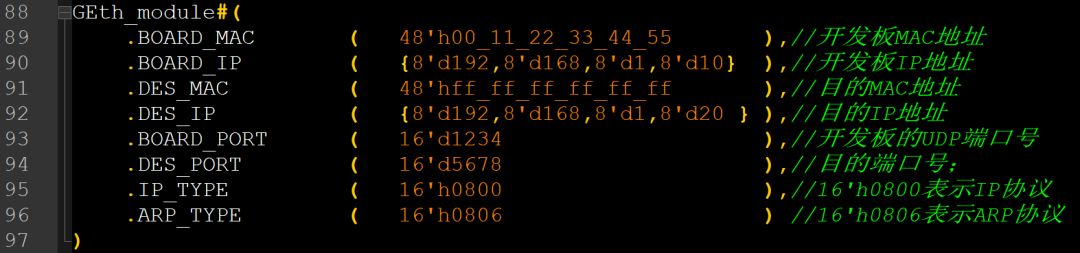

(1)接收状态机

UDP、ARP、ICMP状态机如下:

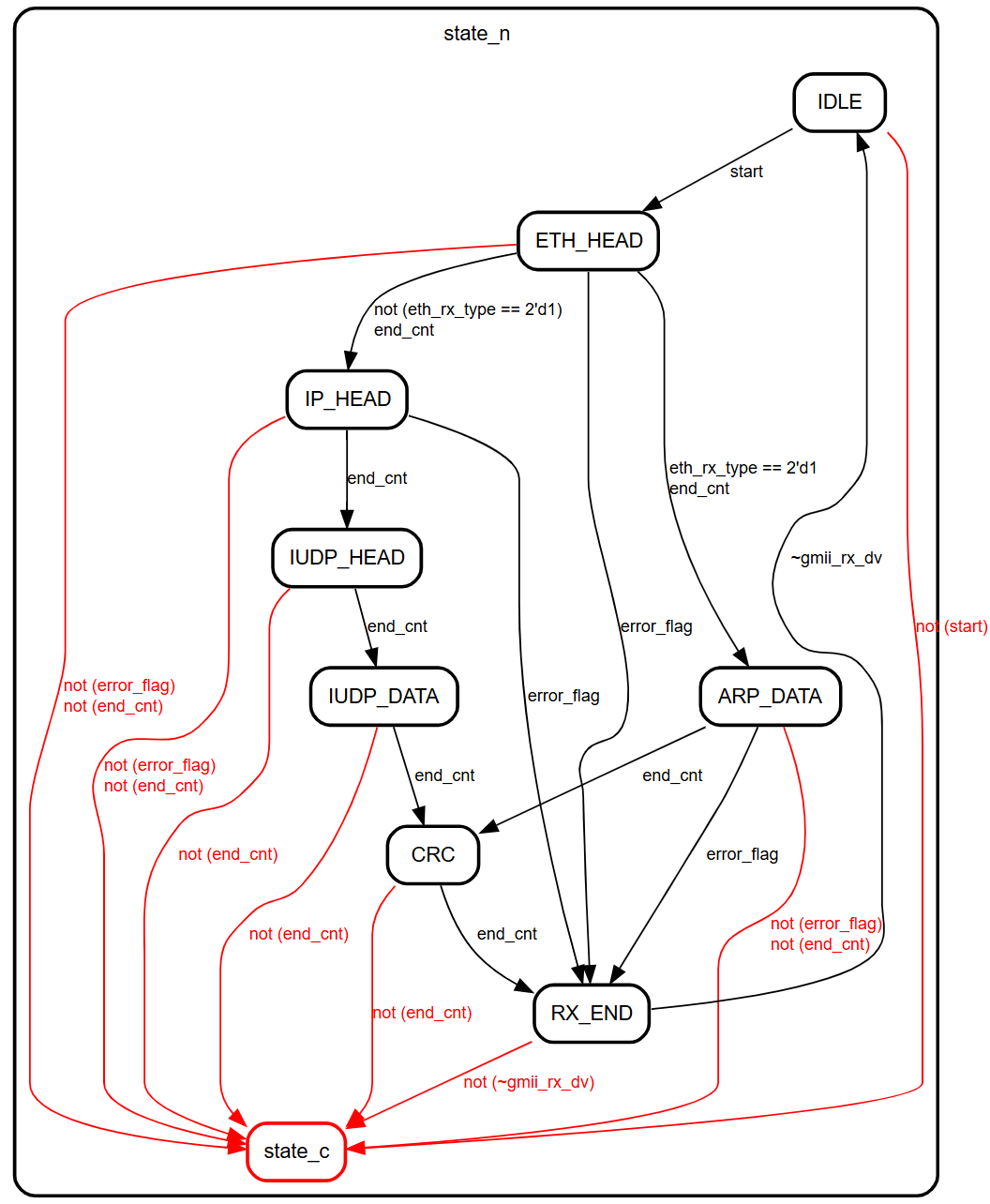

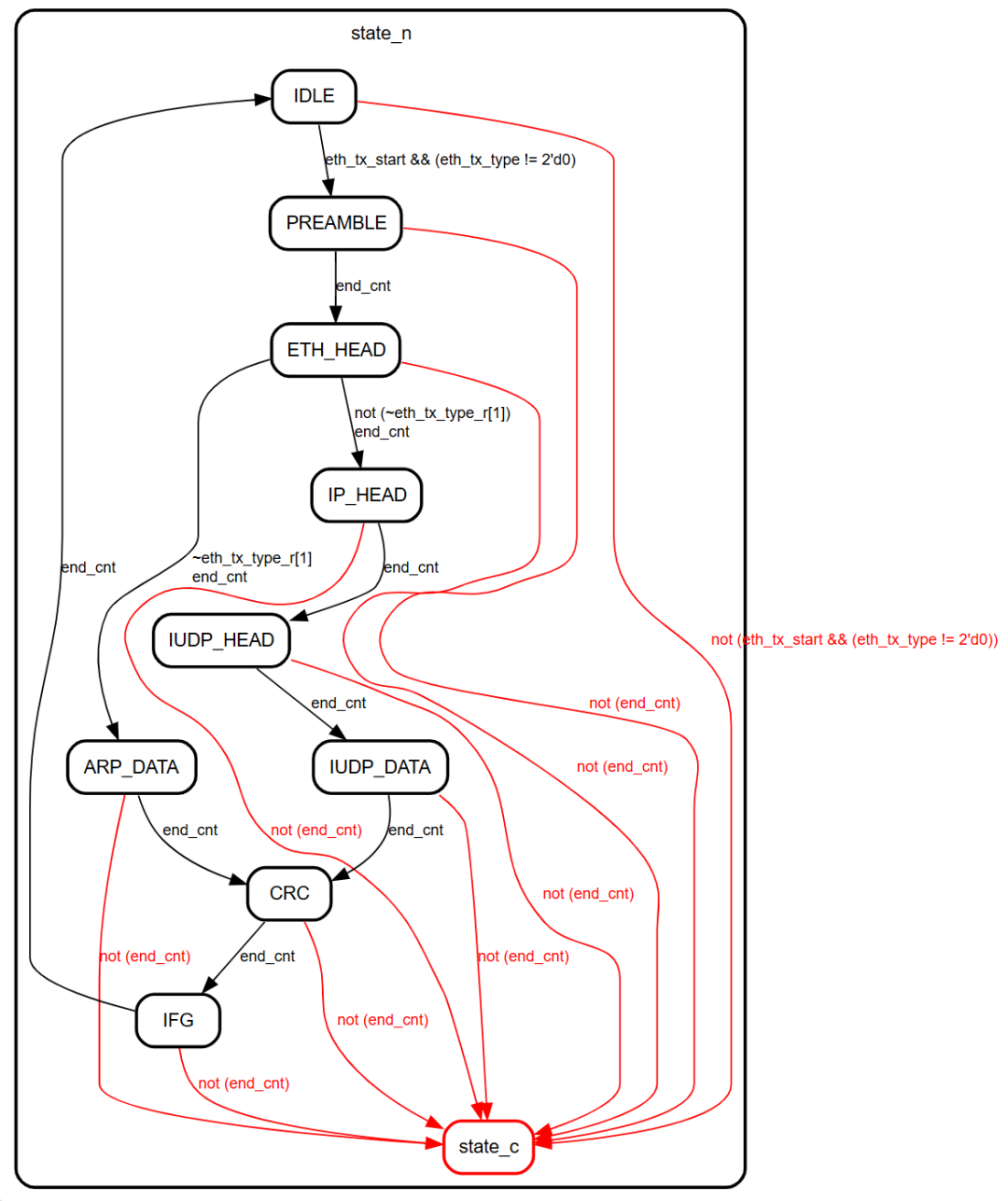

(2)发送状态机

UDP、ARP、ICMP发送状态机:

(3)主要时序关系

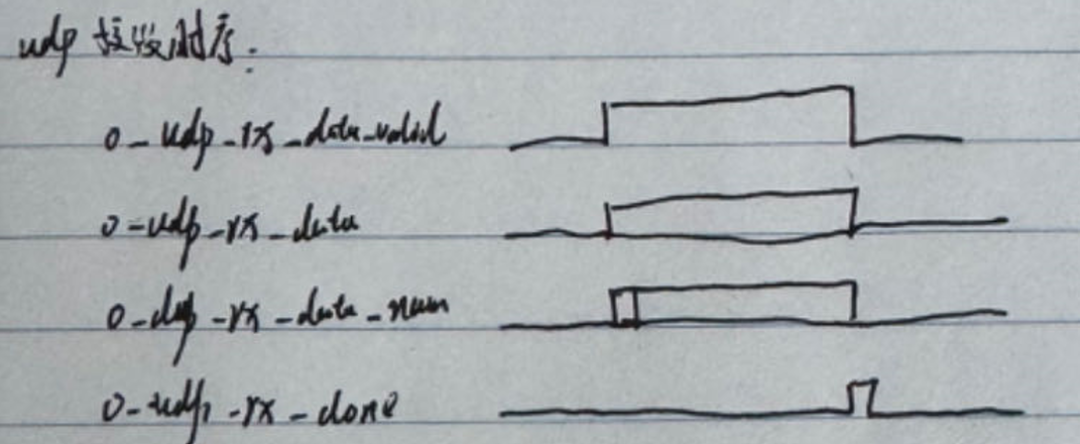

UDP接收时序:

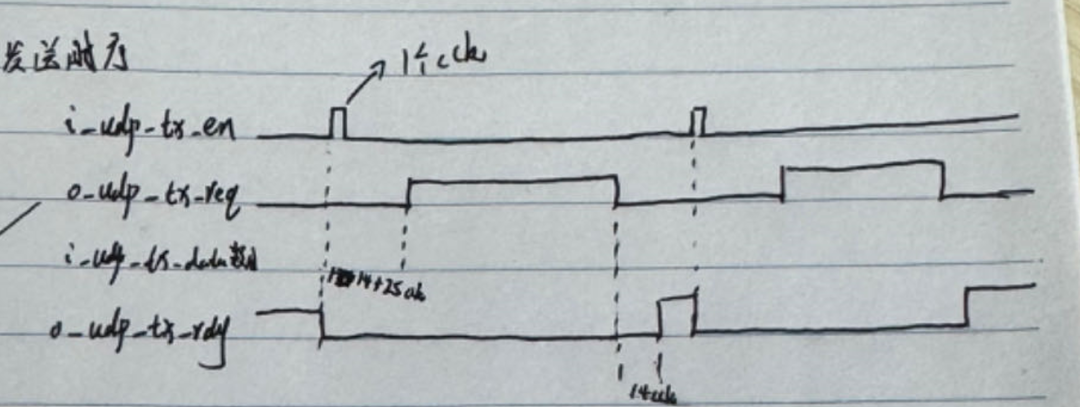

UDP发送时序:

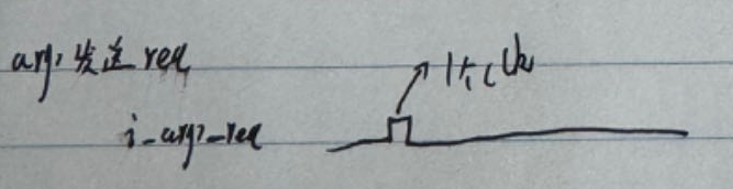

ARP请求时序:

4 、实验测试

4.1 PHY芯片配置测试

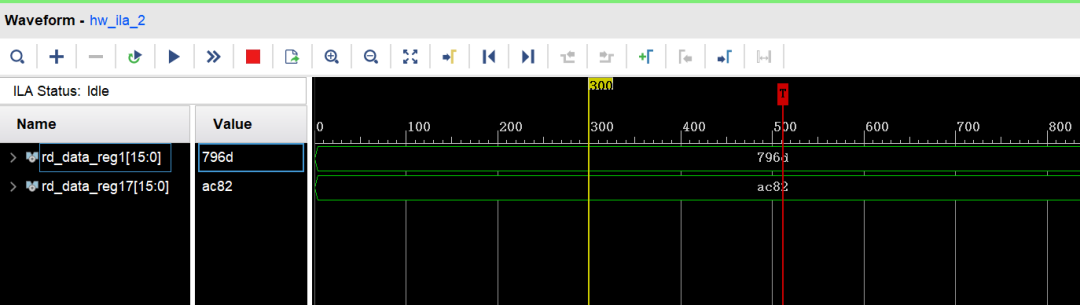

上电后ILA抓取寄存器1和寄存器17的值如下:

寄存器1的值为0x796D,bit5=1表示自协商过程完成,bit2=1表示link成功。

寄存器17的值为:0xAC82,bit[15:14]=10表示1000Mbps,bit13=1表示全双工,bit10=1表示link OK,bit1=1表示接收端OK。

4.2 ICMP功能测试

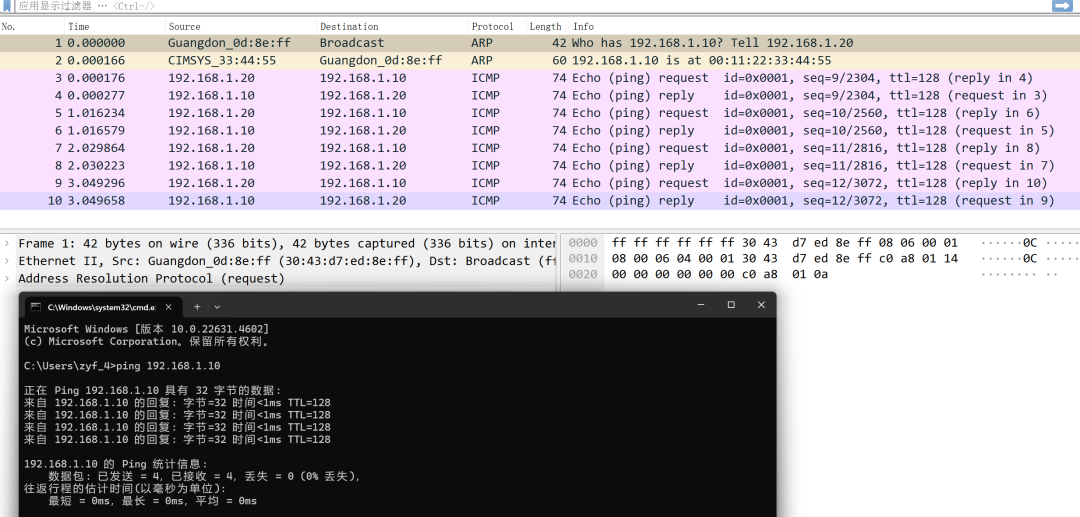

ping下位机192.168.1.10:

在ping下位机之前,上位机首先arp寻址下位机,待上位机收到ARP应答报文解析出下位机MAC地址后,才发起ICMP回显请求报文;FPGA收到ICMP回显请求报文后对应响应回显应答报文。

4.3 ARP功能测试

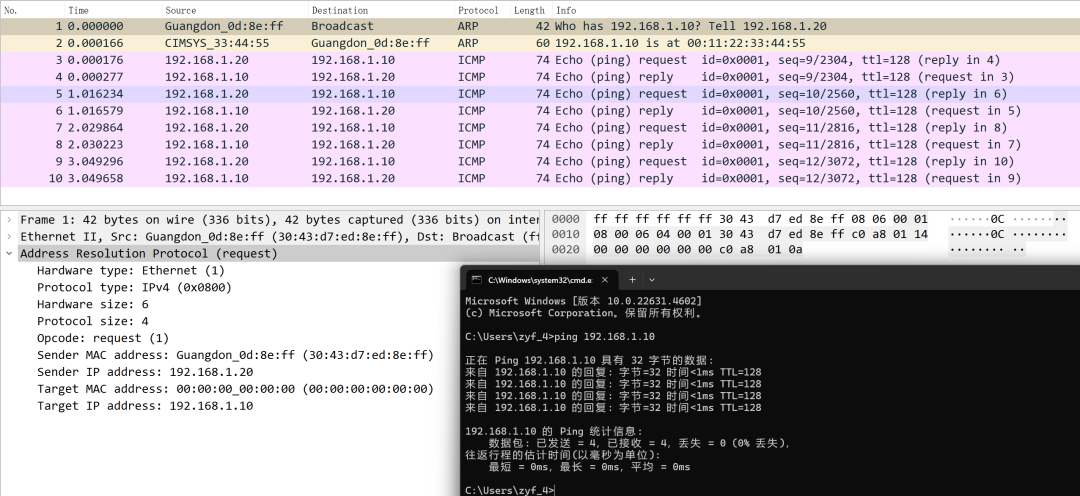

在ping测试中,上位机的arp请求报文如下:

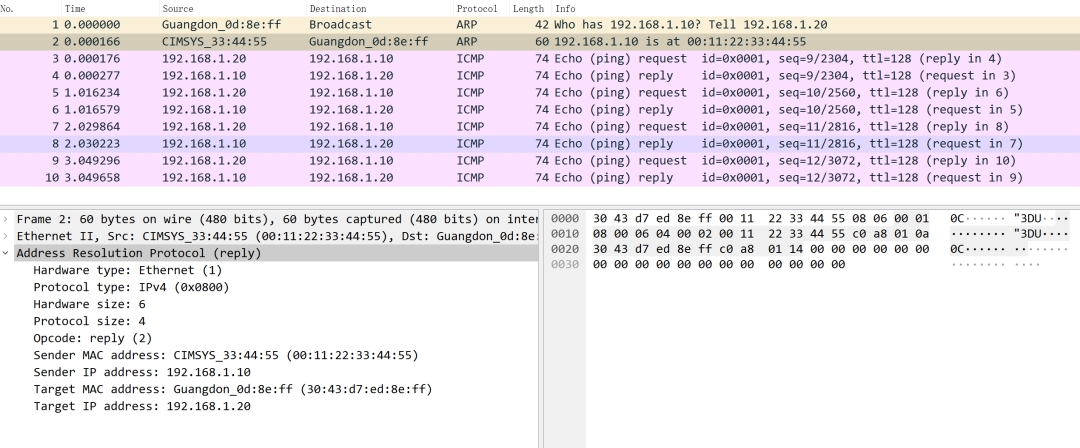

FPGA的应答报文如下:

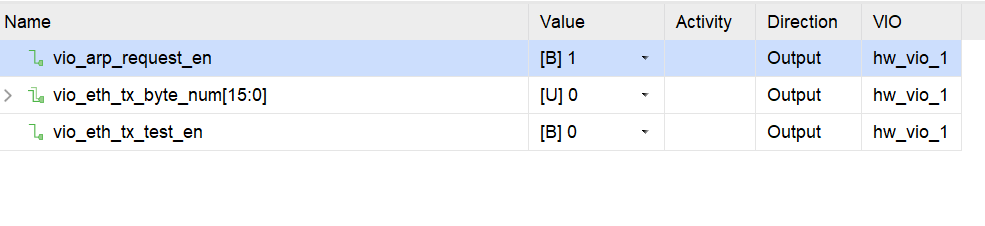

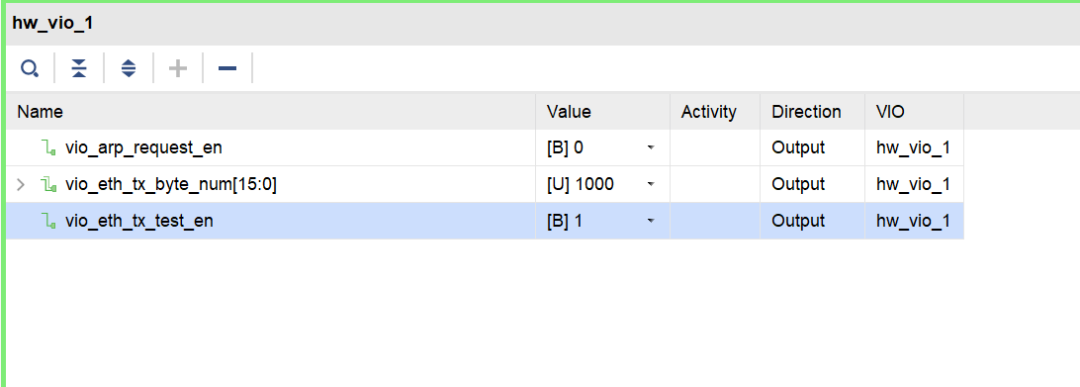

FPGA同样具有发送ARP请求报文:通过设置VIO进行测试

wireshark抓取测试过程:

4.3 UDP收发测试

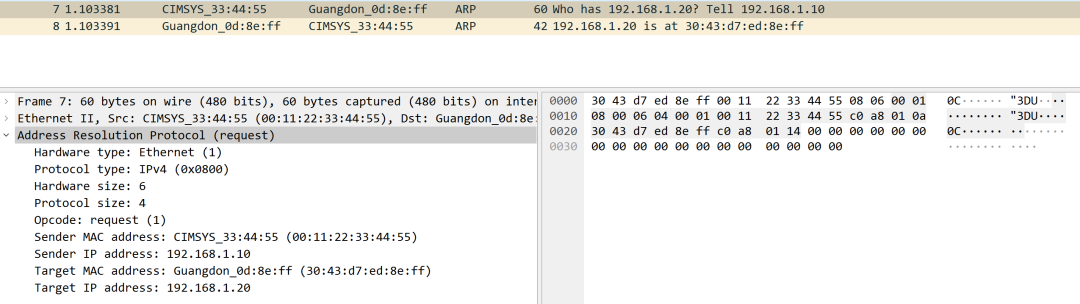

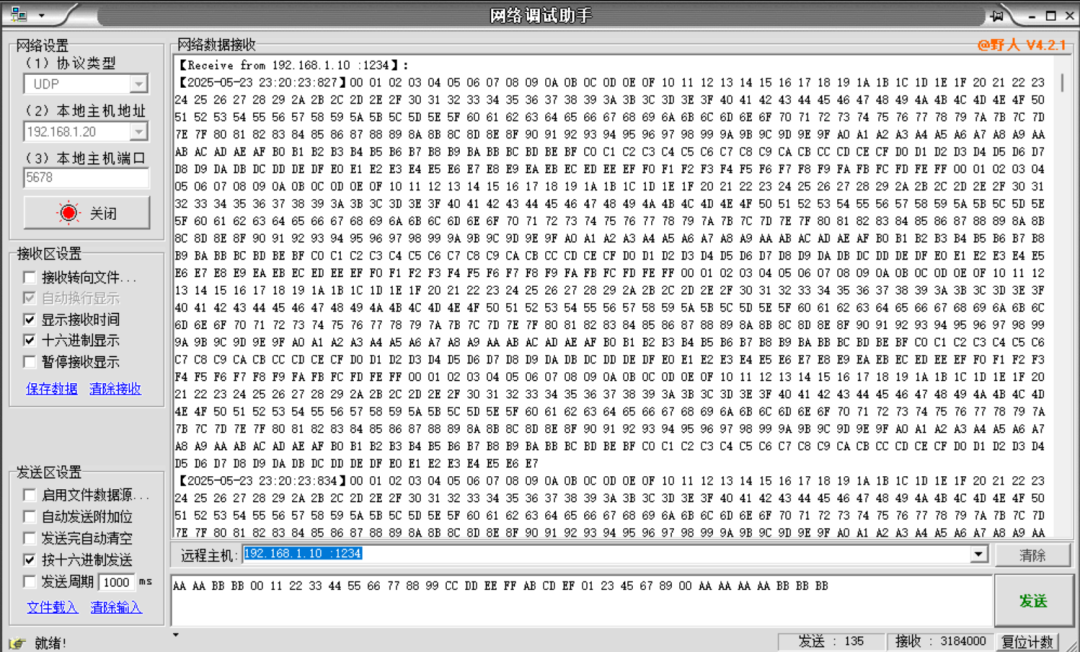

上位机发送UDP数据,FPGA接收解析测试:

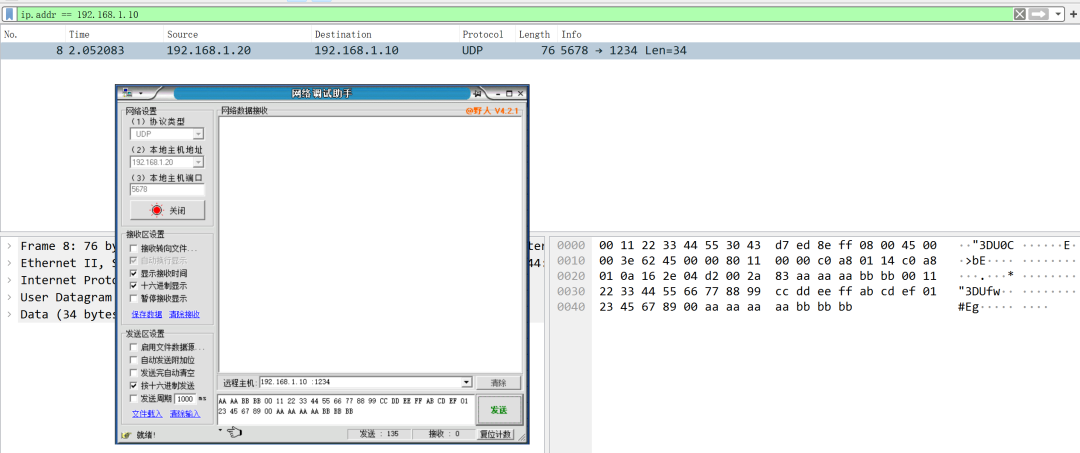

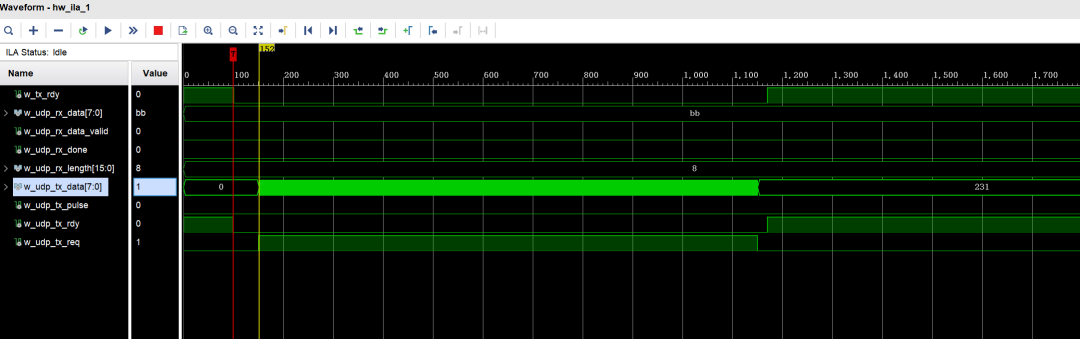

FPGA能够正确解析出接收到的对应数据,接收时序如图。

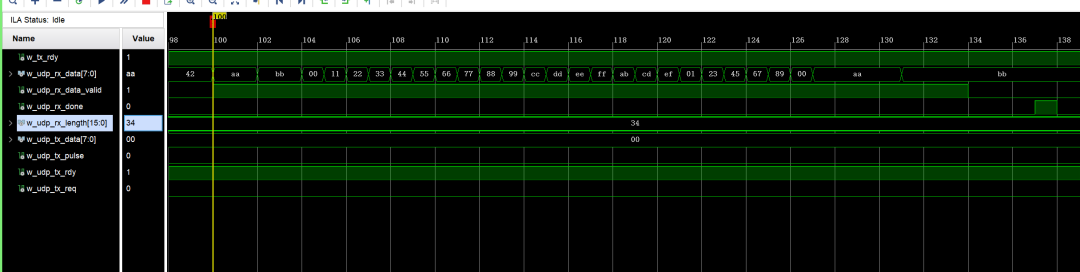

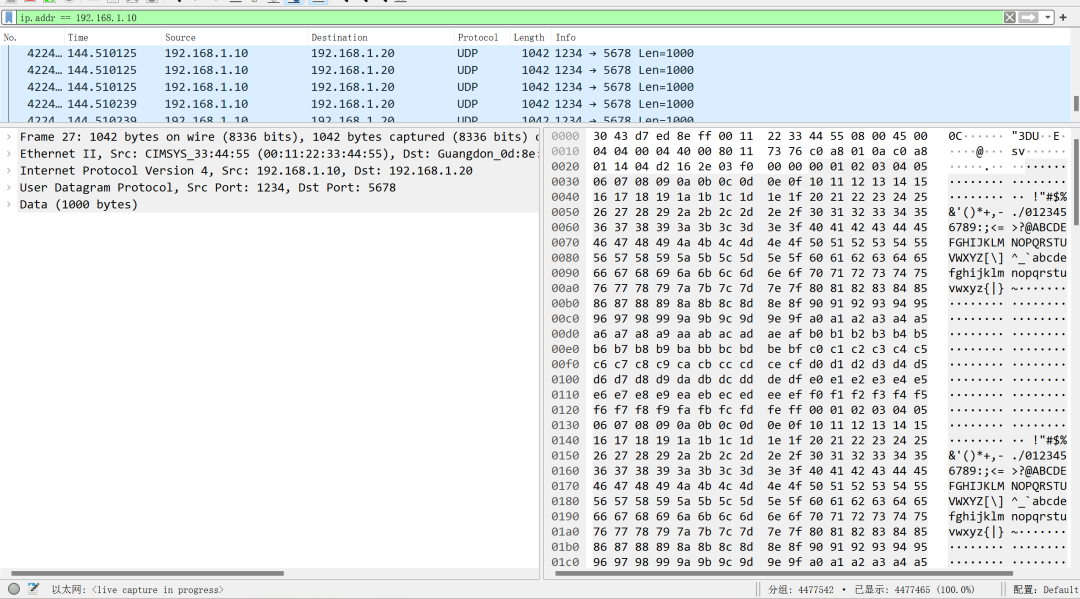

FPGA发送UDP报文,上位机接收测试:

VIO设置UDP数据长度为1000字节:

FPGA的发送时序及状态标志:

上位机接收:

1506

1506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?