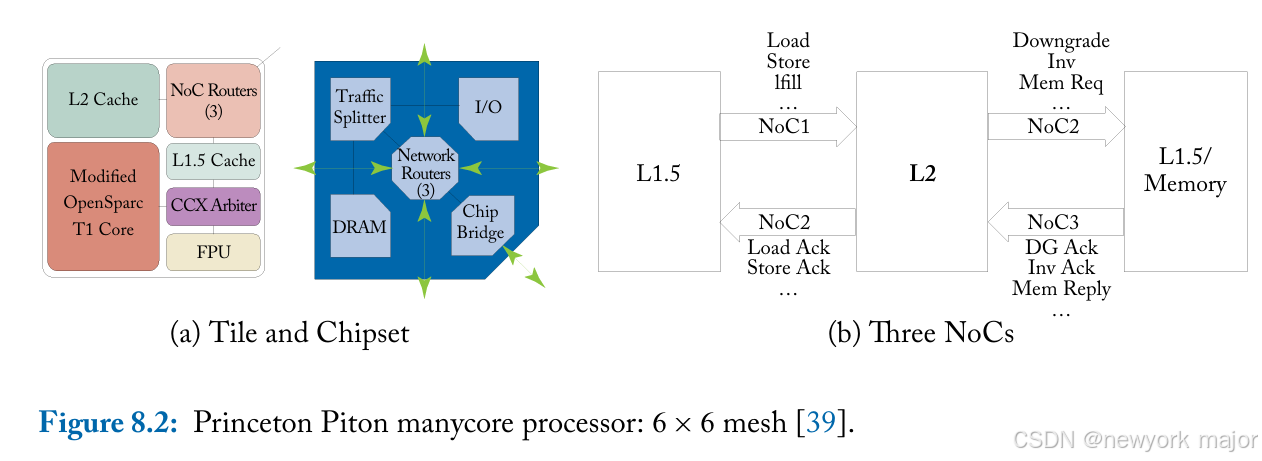

普林斯顿大学的 OpenPiton 处理器是一个多核研究框架;它通过一个名为Piton的25核平 铺处理器 ASIC 原型进行了演示,该原型采用 32 nm 工艺,运行速度为 1 GHz。这款多核处理器使用 OpenSPARC T1 内核,并提供通过三个 NoC 互连的内存子系统。

- OpenSPARC T1的L1的接口是OpenSPARC CCX (CPU-Cache Crossbar)接口。

- a inclusive L2 cache,分布在所有的tile上;

- The memory subsystem maintains cache coherence with a directory-based MESI coherence protocol.

- 遵循OpenSPARC T1使用的TSO内存一致性模型。

- OpenPiton增加了一个新的L1.5 cache来将CCX消息转换为coherence协议消息;

- Coherent messages be tween L1.5 caches and L2 caches communicate through three NoCs.

- A chip bridge connects the tile array to the chipset. 通过左上角的tile,为内存和I/O请求服务

- OpenPiton还包括一个AXI4-Lite桥接器,它通过将noc映射的内存I/O操作接口到axis - lite,提供与各种I/O设备的连接。

Three NoCs transport messages across the various message classes of the coherence pro tocol。NoC1将请求从L1.5传输到L2s;NoC2将L2的响应和请求分别传输到core和memory controller;NoC3传输L1.5的回写和从memory controller到L2的响应。为了确保消息类之间的deadlock-freedom,noc之间的优先级顺序为NoC3 > NoC2 > NoC1。这确保了响应总是被耗尽。noc也保持点对点的顺序。

所有片上网络都使用64位bi-directional links。每个片上网络使用的是wormhole routers without any virtual channels.。该设计本质上使用多个物理网络,而不是在相同的物理链路上复用多个VCs。维度排序X-Y路由用于避免路由和协议死锁。当沿相同维度路由时,每个虫洞路由器需要一个周期,and two cycles at turns。在ASIC原型中,片上路由器占用芯片面积不到3%,主要由核心和缓存占据。

On-Chip-Network典型实现之PRINCETON PITON

于 2024-12-12 15:20:17 首次发布

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?