1.基于2018.2的vivado

2.部分基于小梅哥的ACZ020-CB开发板做的测试,部分来自公司自制设备

3.关于ZYNQ的官方库和示例,印度老哥们写的代码,一般测试不会很深,在化用为自己的代码时,需要格外注意!

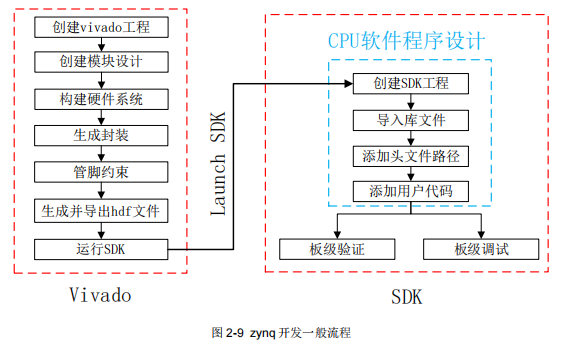

| 内容 | 说明 | 图示 |

|---|---|---|

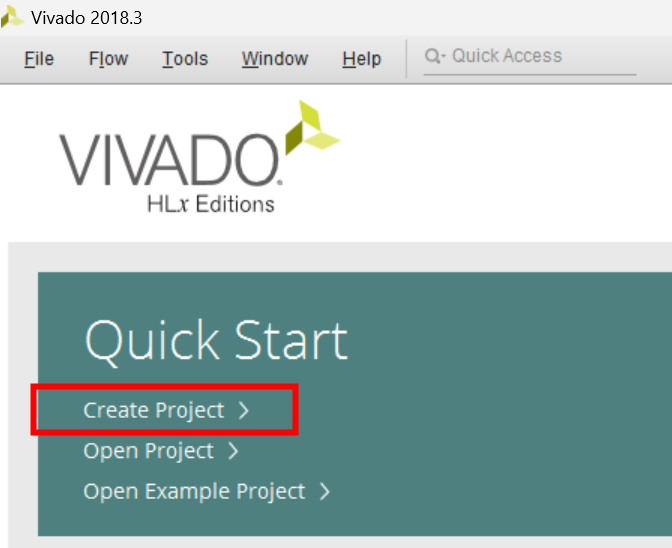

| 新建工程 | 创建工程 |  |

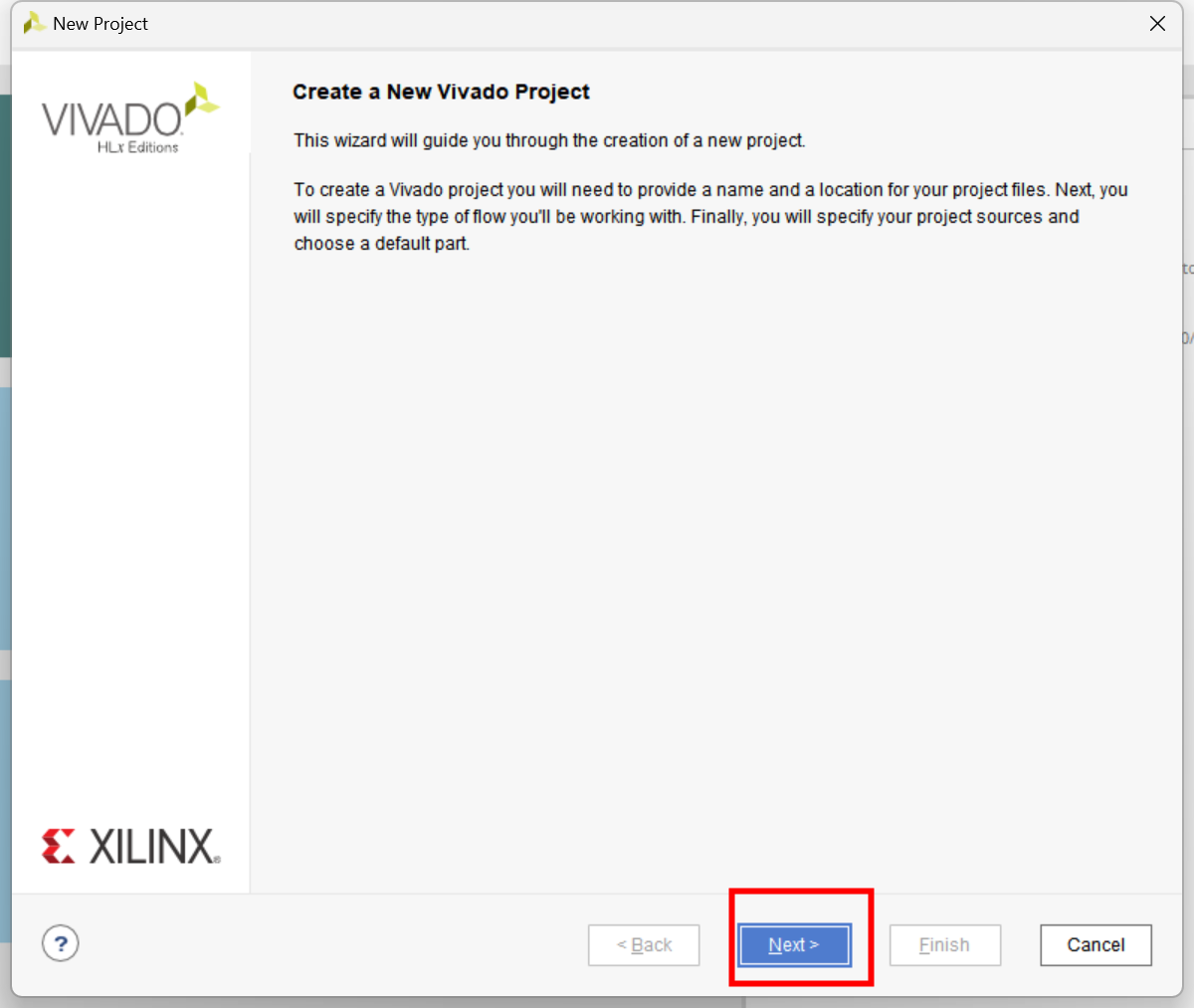

| 下一步 |  | |

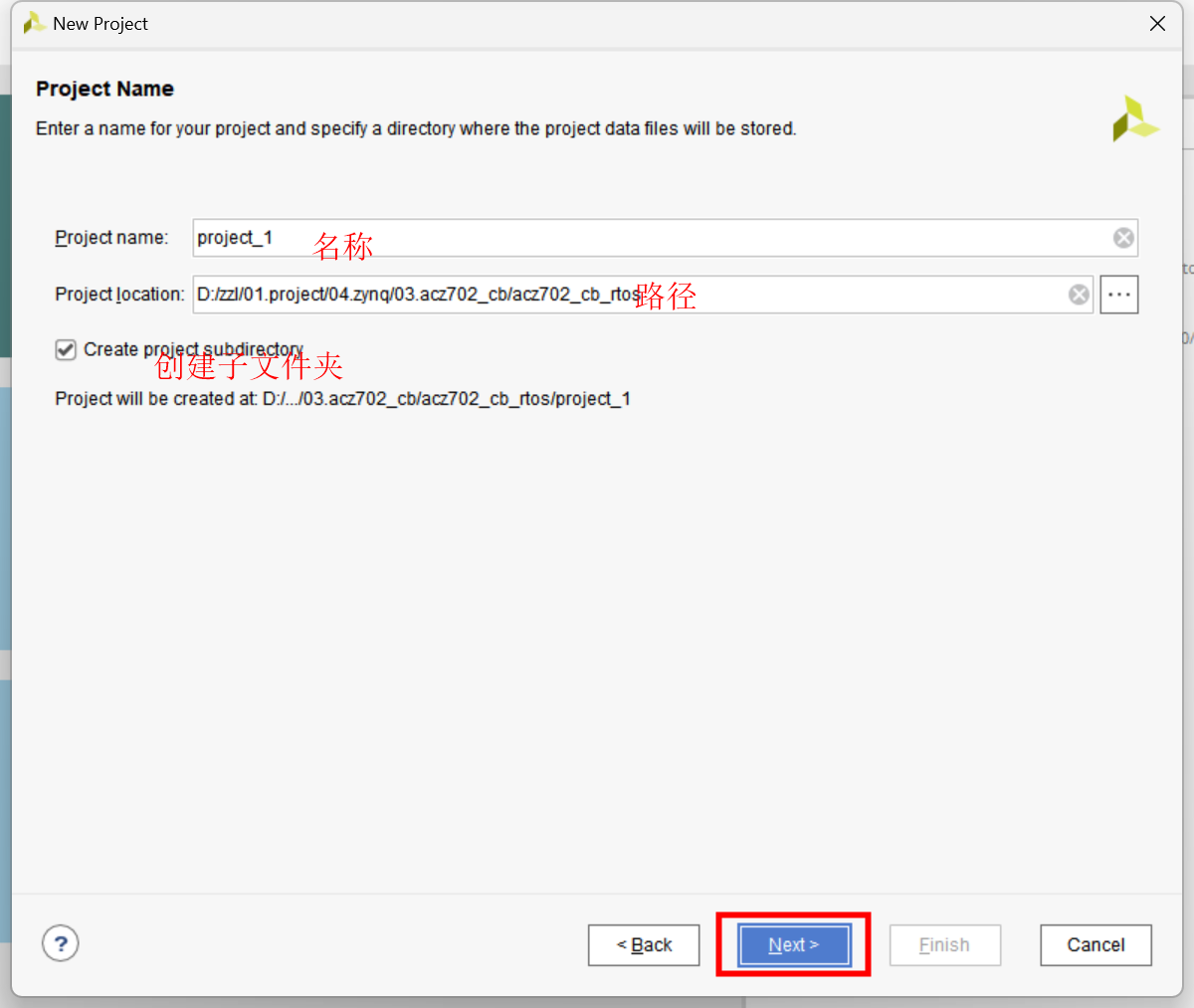

| 起名不能有中文,路径不能过长,创建子文件夹随意勾选(会在创建一个工程名为名的文件夹,所有内容都在文件夹中),然后下一步 |  | |

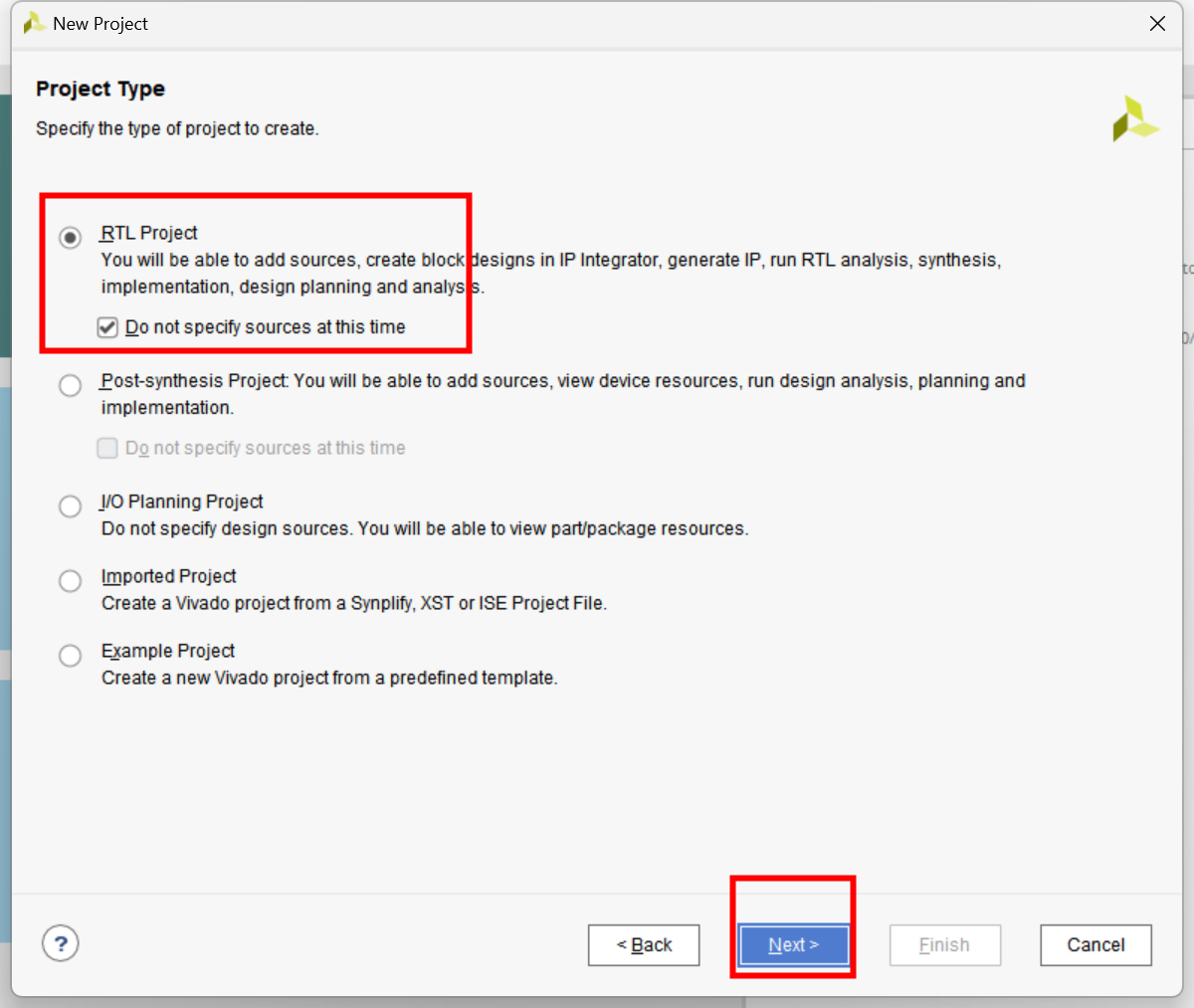

| 选择RTL(寄存器传输级)开发工程,勾选不添加已有的约束和源文件,然后下一步 |  | |

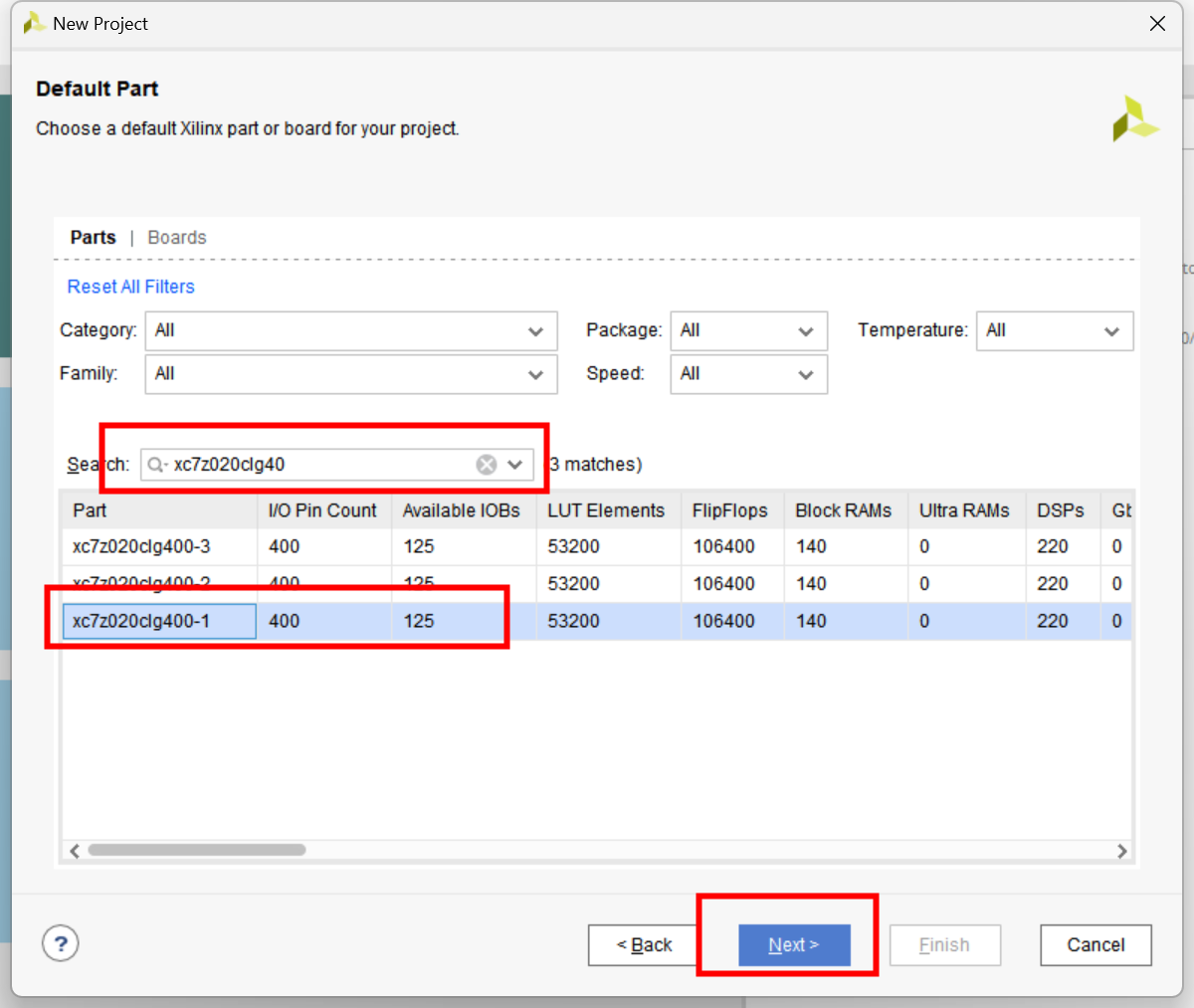

| 找到你的芯片型号(后缀是速度等级,一般选最低的1级,这样程序可以在其他高等级跑),然后下一步 |  | |

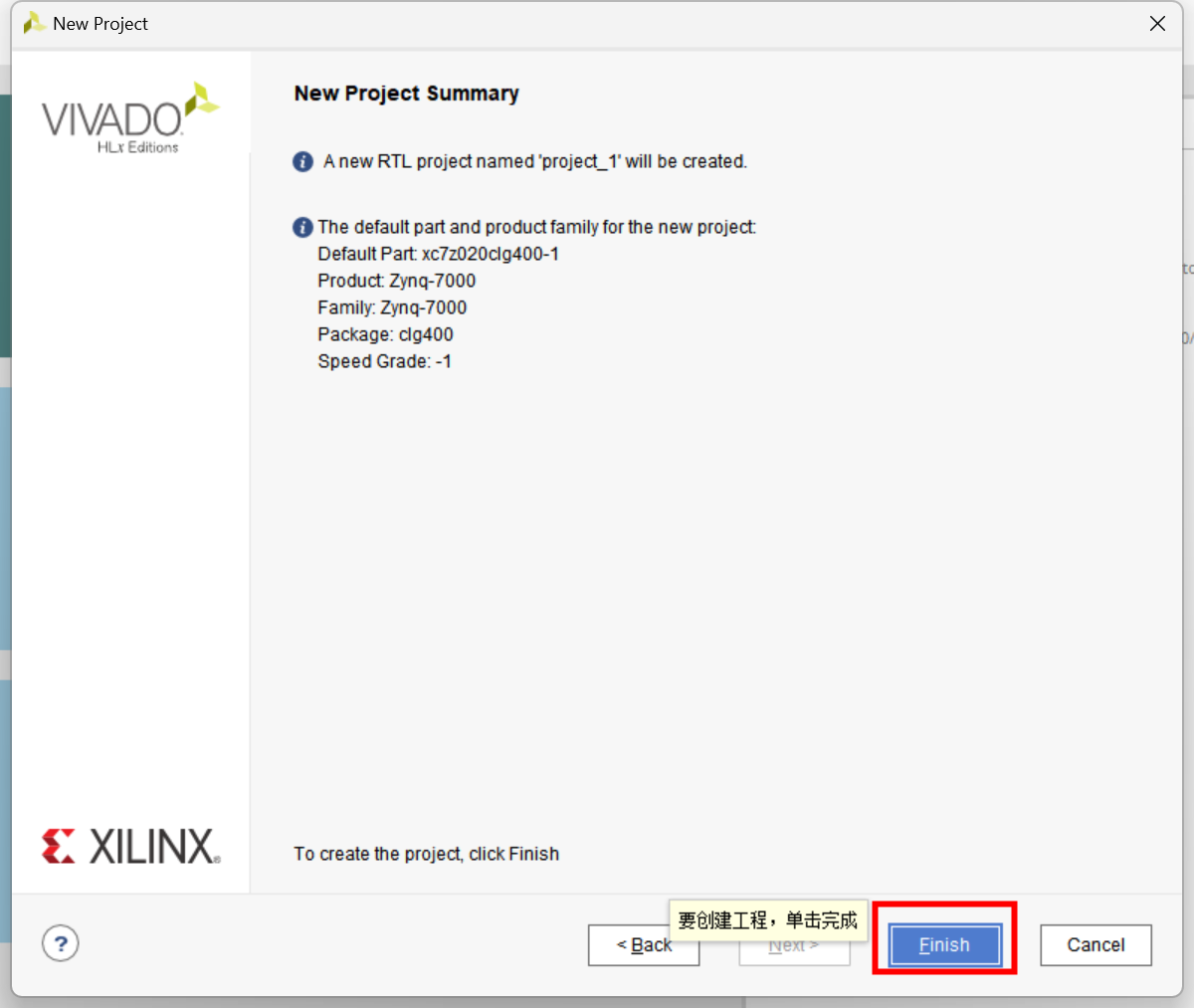

| 完成 |  | |

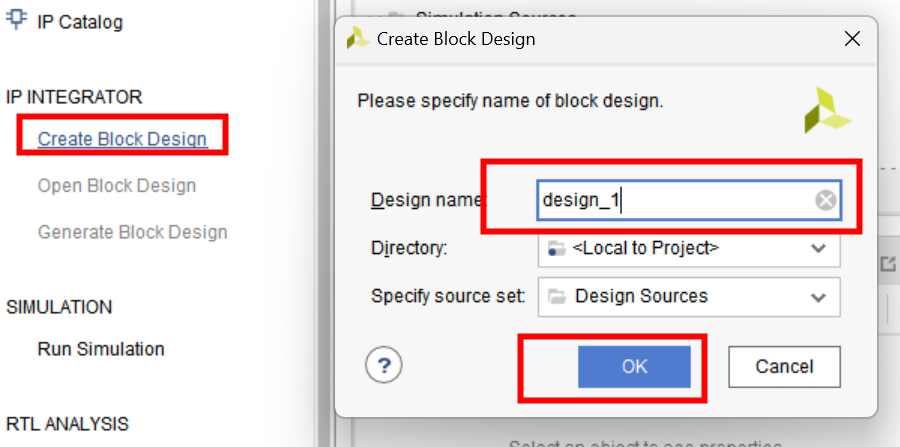

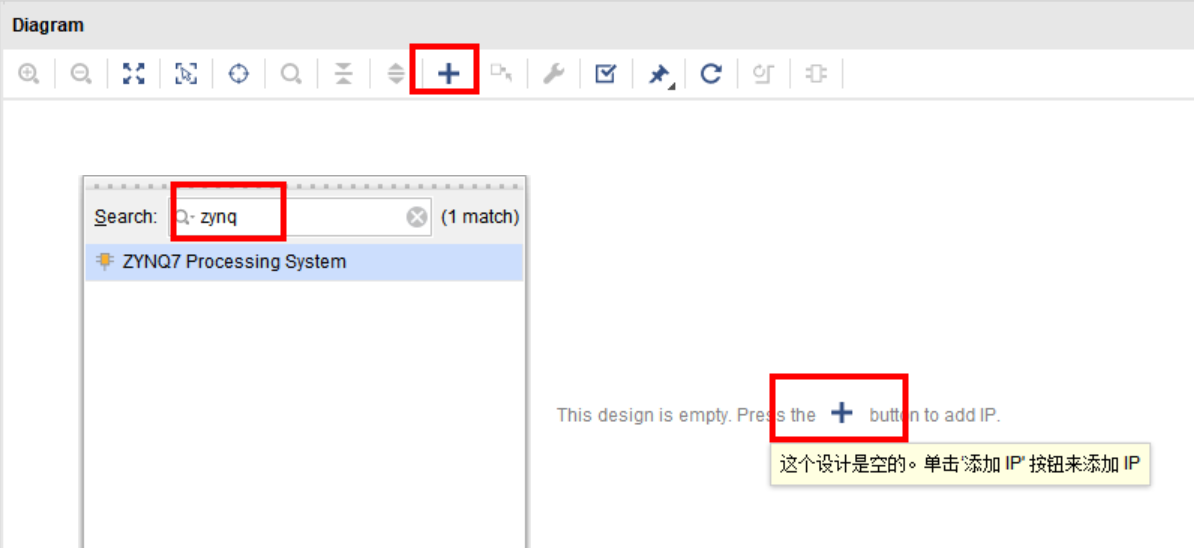

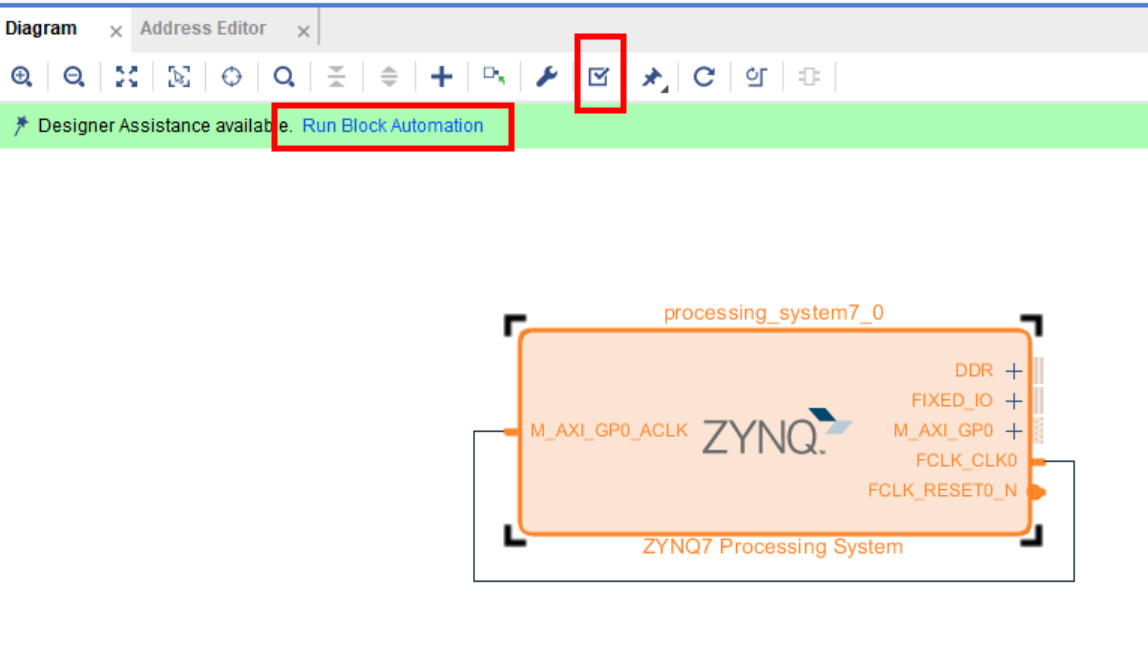

| ZYNQ设置 | 创建块 |  |

| 创建zynq的ip核,两个“+”按钮是一样的 |  | |

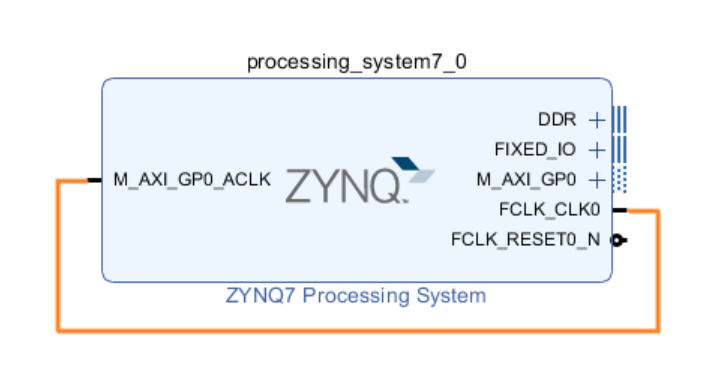

| 把时钟链接起来,双击zynq,打开选项菜单 |  | |

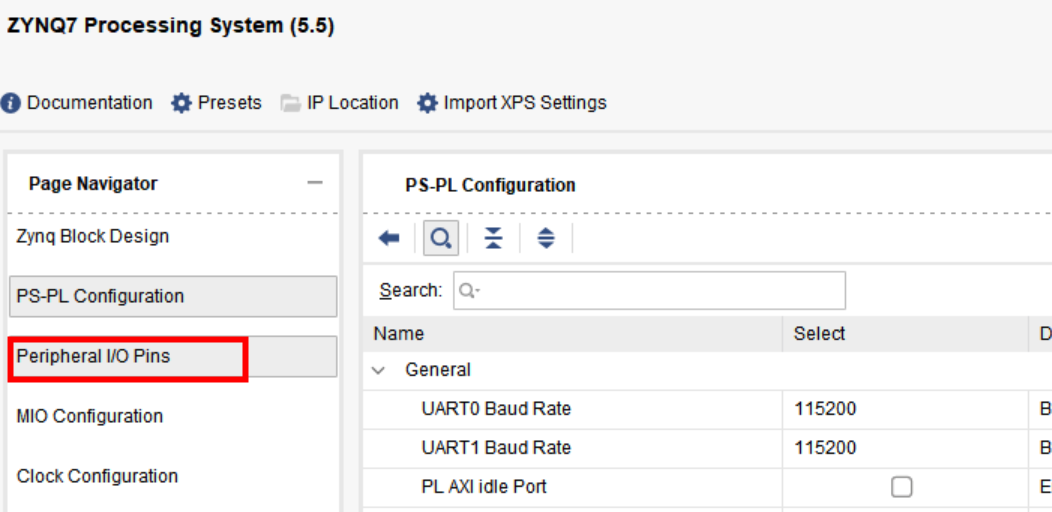

| 设置波特率等参数 |  | |

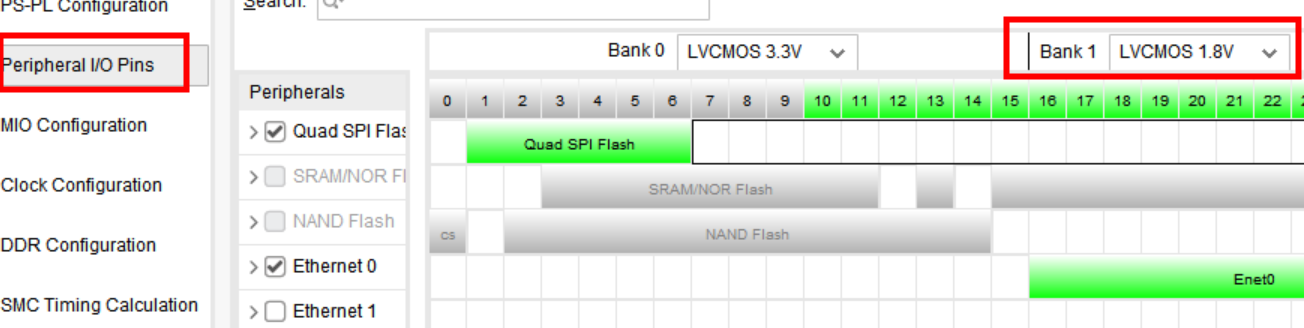

| 选择使用到的模块的,blank2电压1.8V |  | |

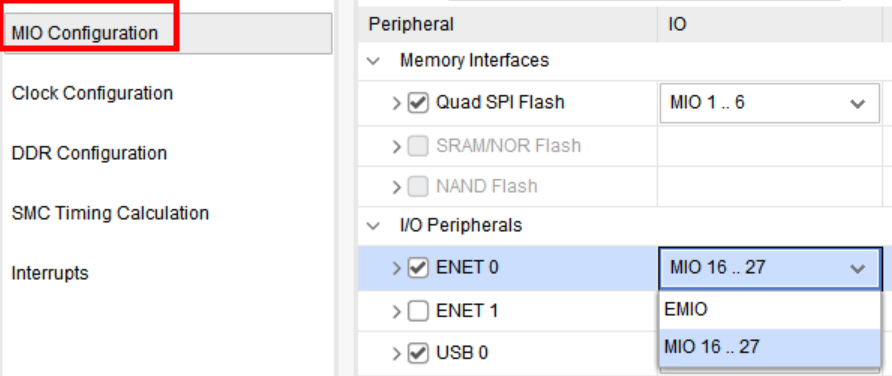

| 配置模块引脚 |  | |

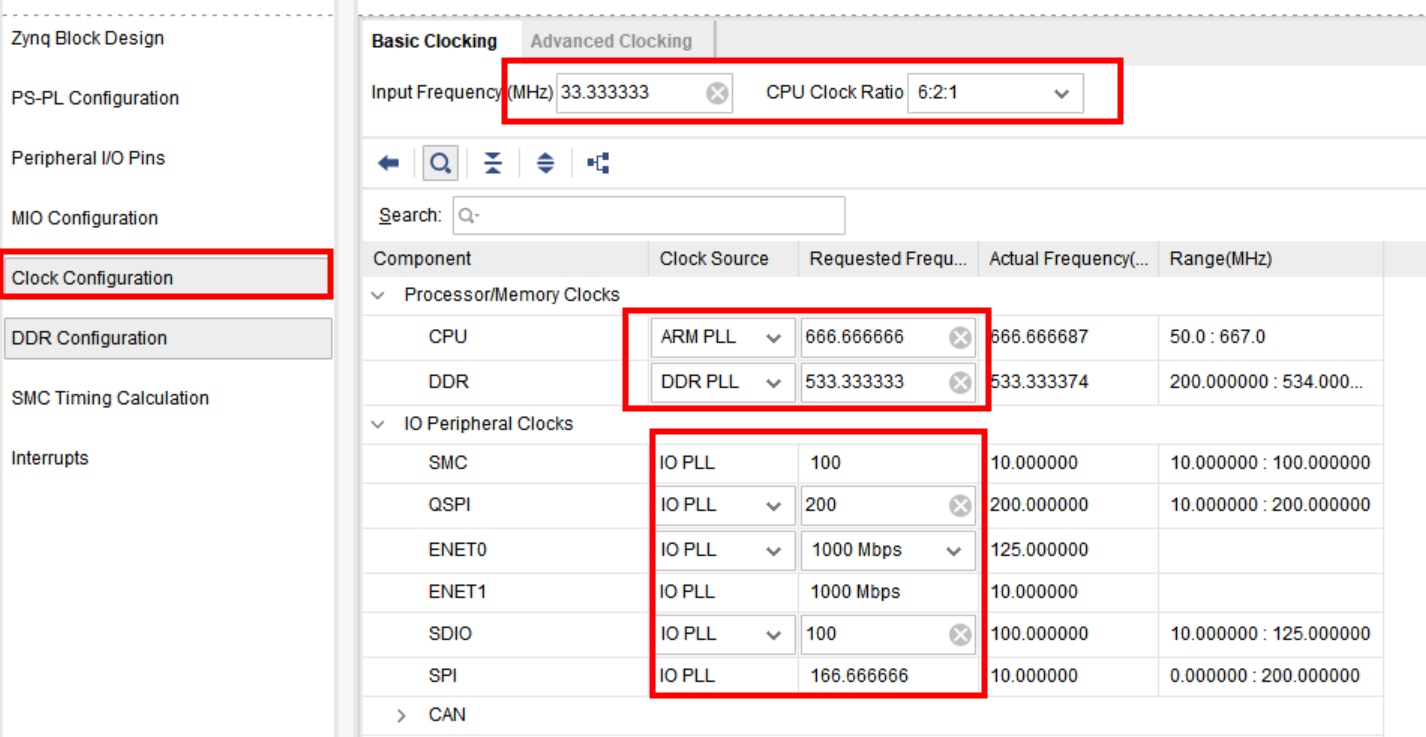

| 配置时钟 |  | |

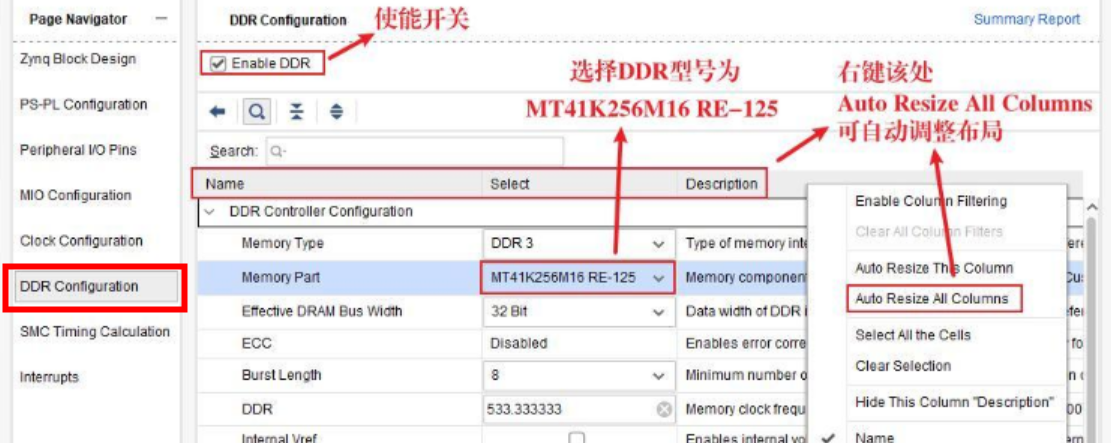

| 配置DDR |  | |

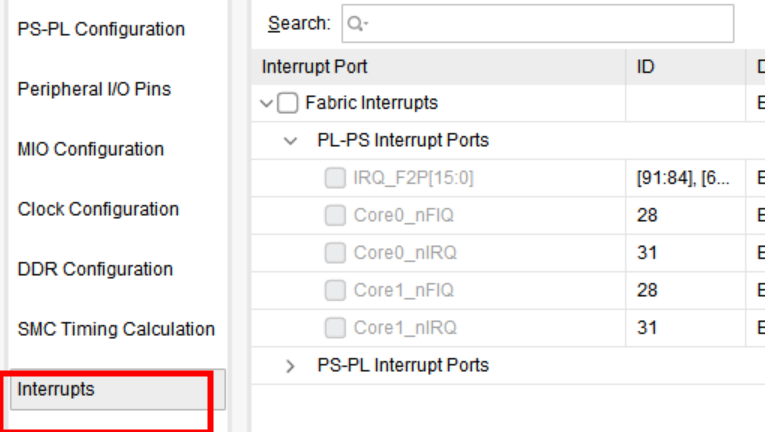

| 配置中断 |  | |

| 生成输出接口 1. FCLK_RESET0_N:全局复位信号,低电平有效。 2. M_AXI_GPIO:通用 AXI 接口信号,M 代表其作为主机信号。 3. M_AXI_GPIO_ACLK:M_AXI_GPIO 的输入时钟信号。 4. FCLK_CLK0:PS 输出时钟信号。 |  | |

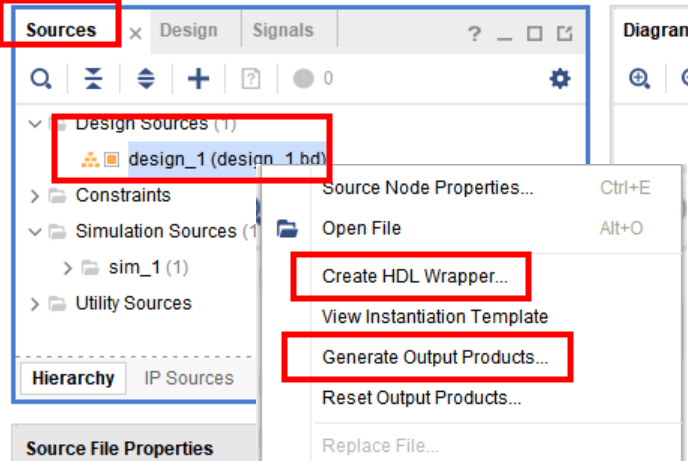

| 创建HDL 创建输出 |  | |

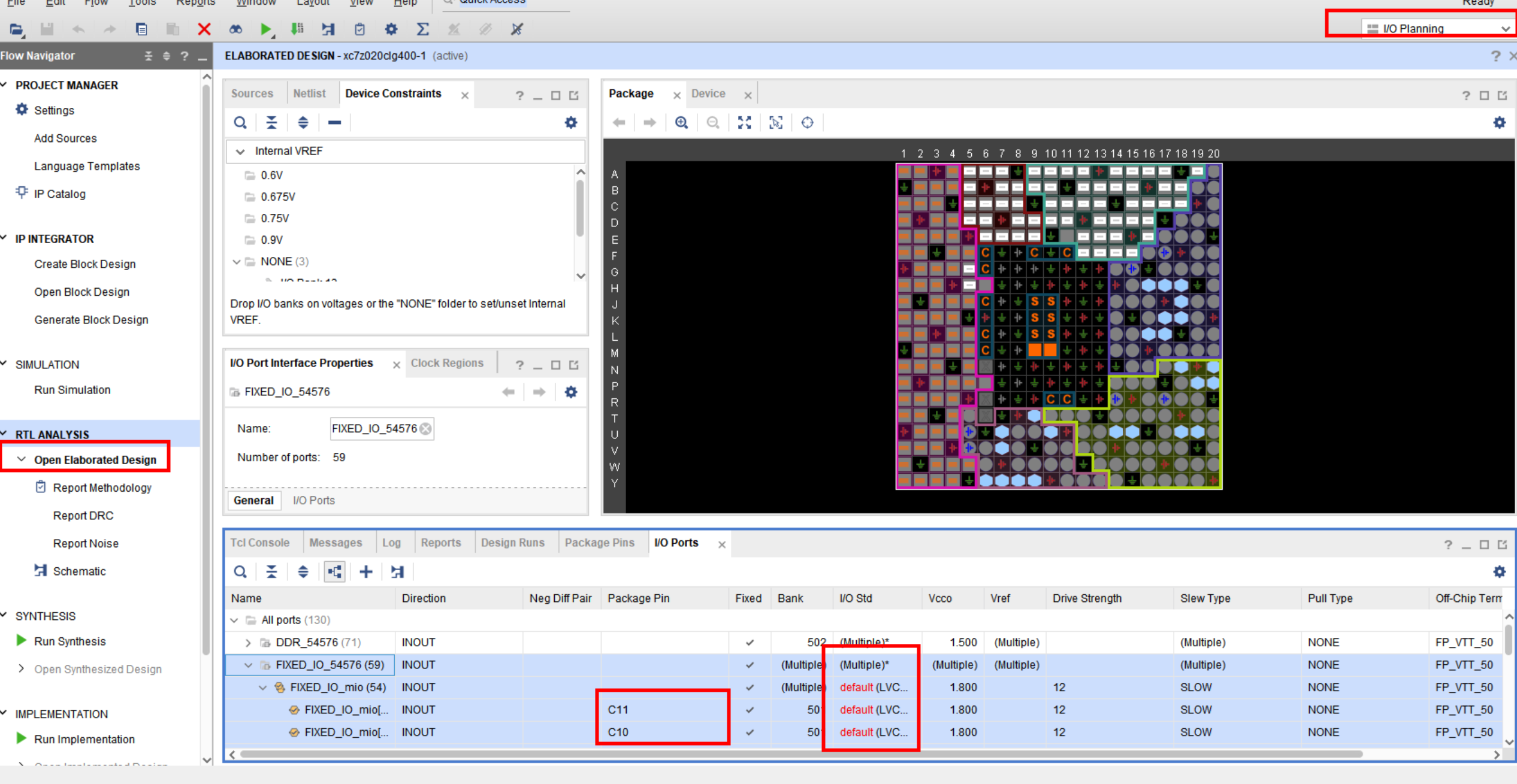

| 配置用到的引脚电平 复用的引脚选择 |  | |

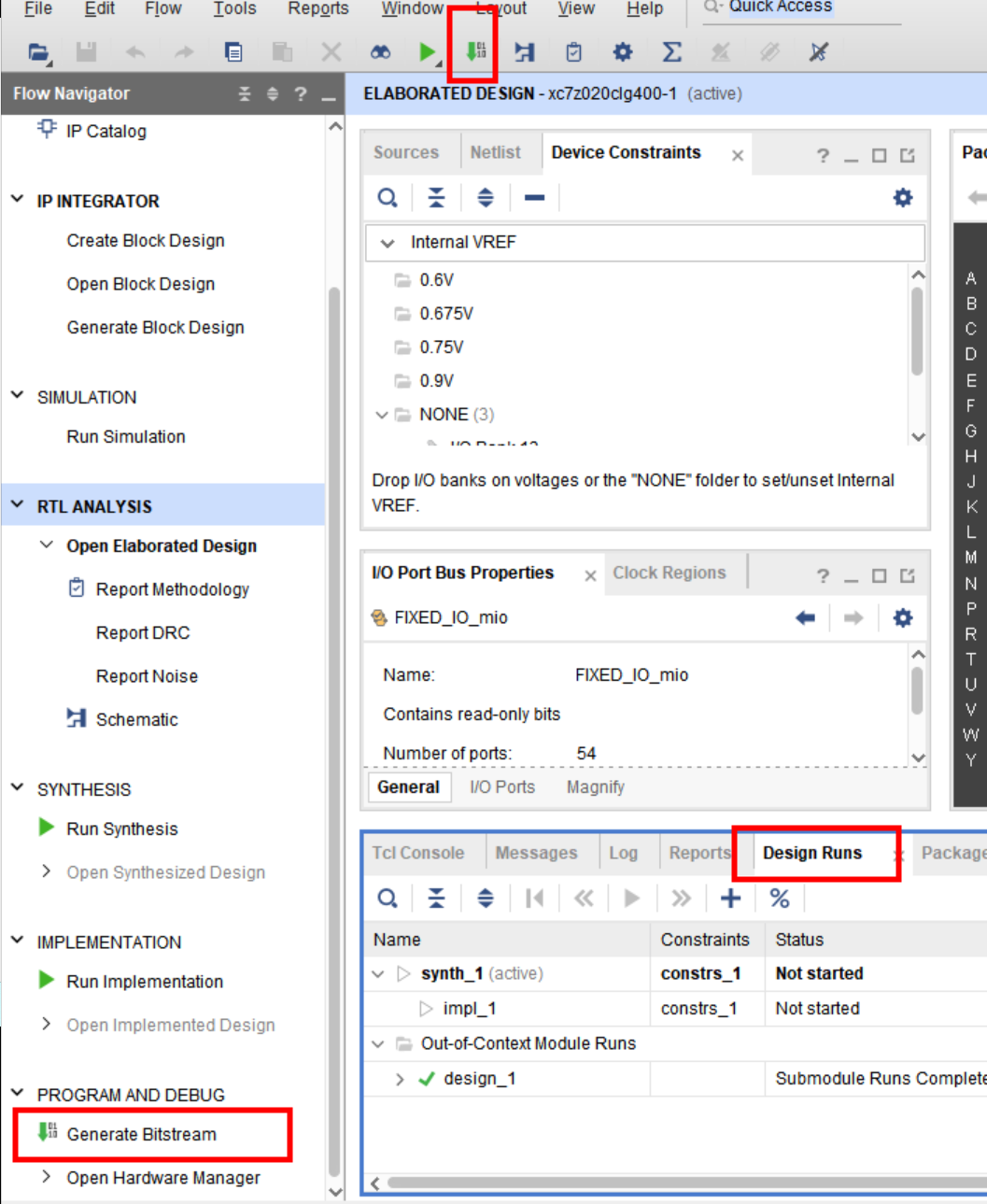

| 生成FPGA的烧录文件(比特流) |  | |

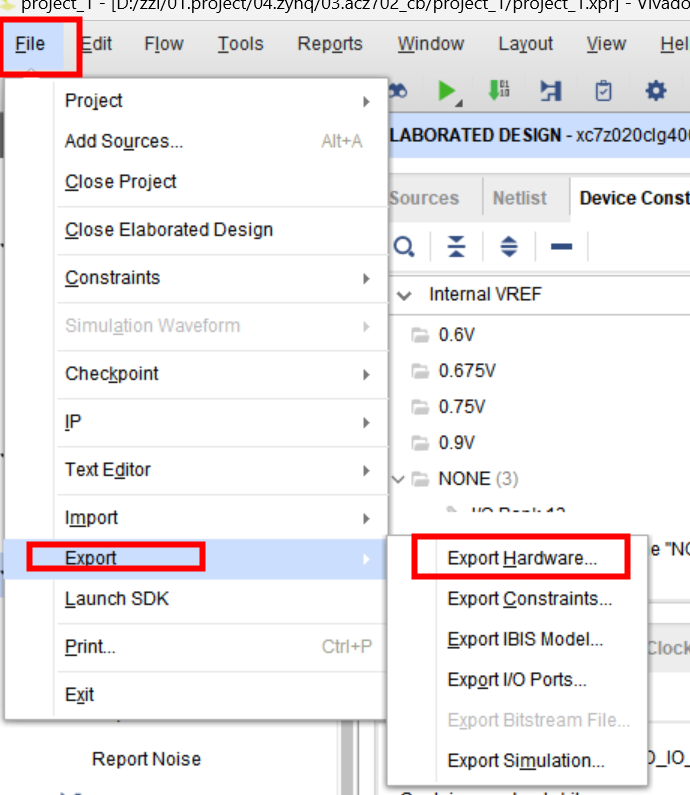

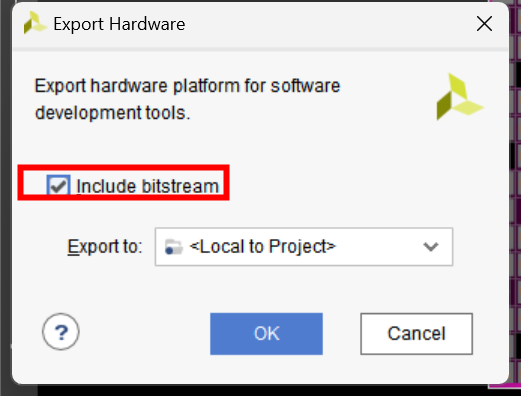

| 导出设计,勾选导出比特流 |   | |

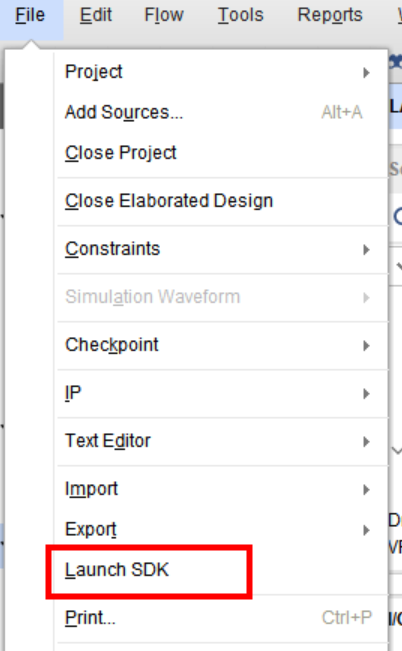

| 打开SDK |  | |

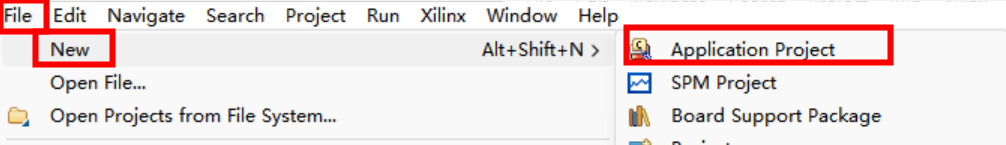

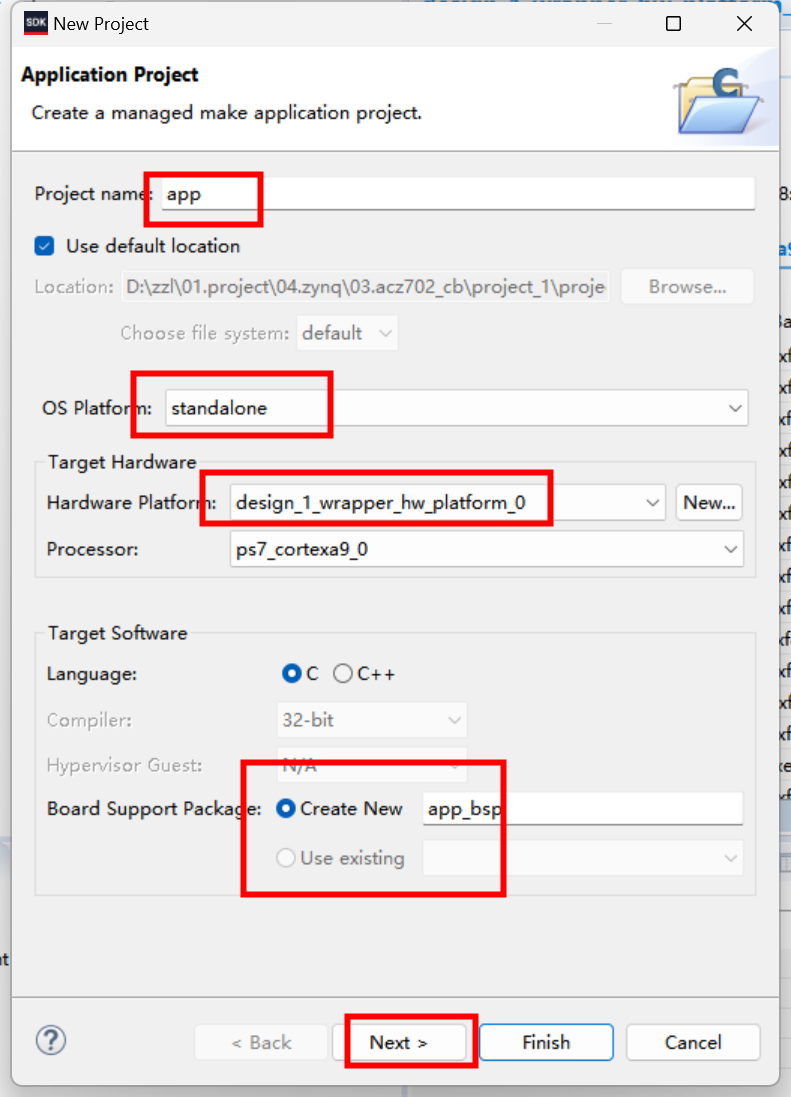

| SDK开发 | 新建一个APP |  |

| 填写文件名 选择操作系统 选择硬件 选择新建BSP,或者使用已有的BSP 然后下一步 |  · · | |

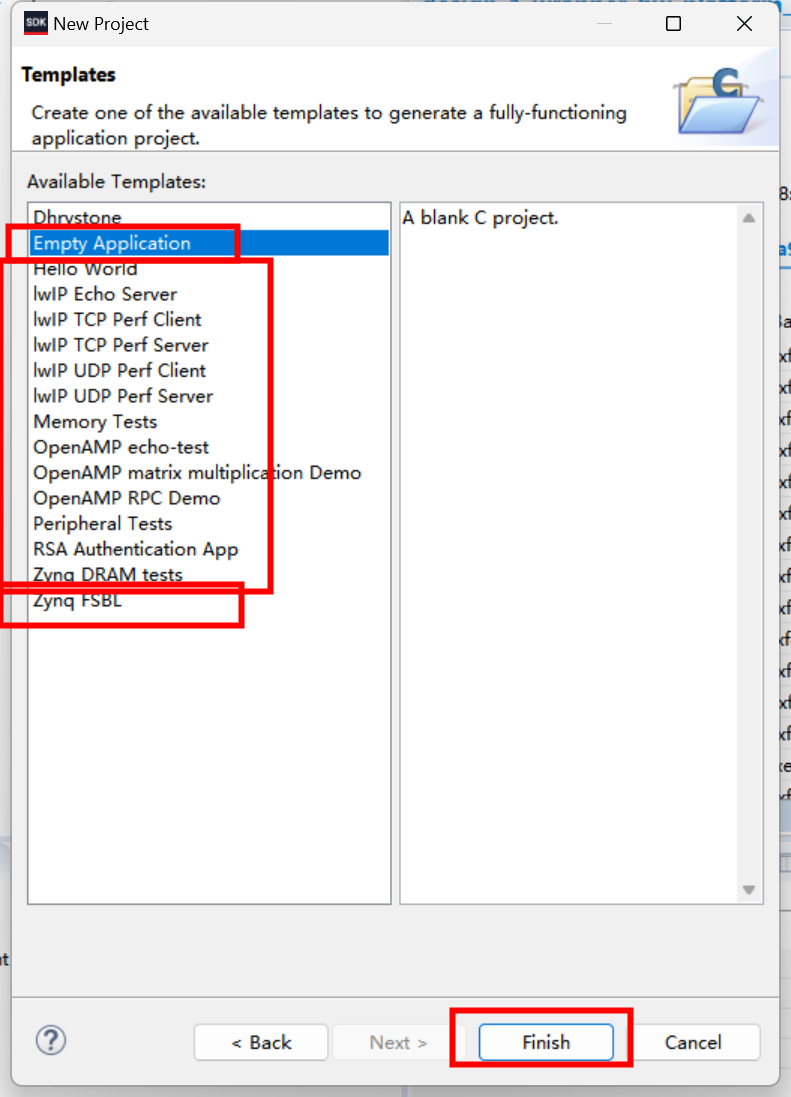

| 选择: 空白程序 示例程序 first stage boot loader 然后下一步 |  | |

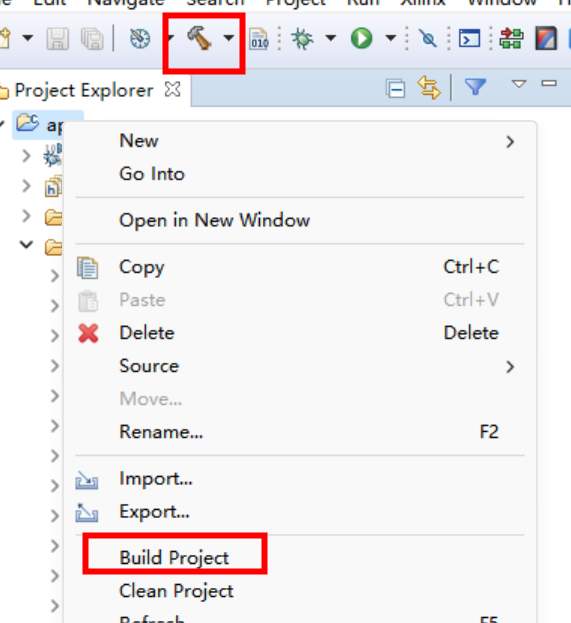

| 编译 |  | |

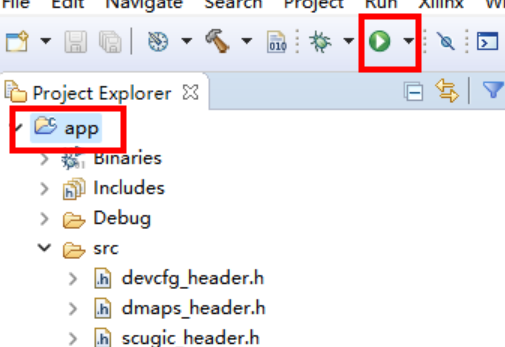

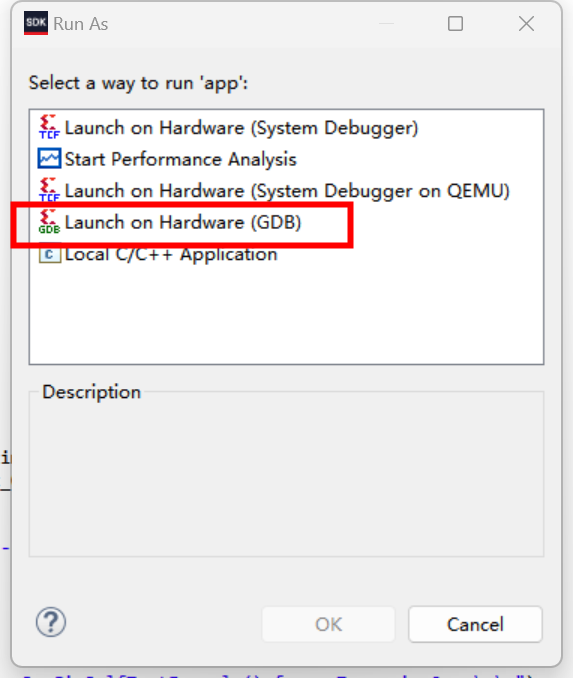

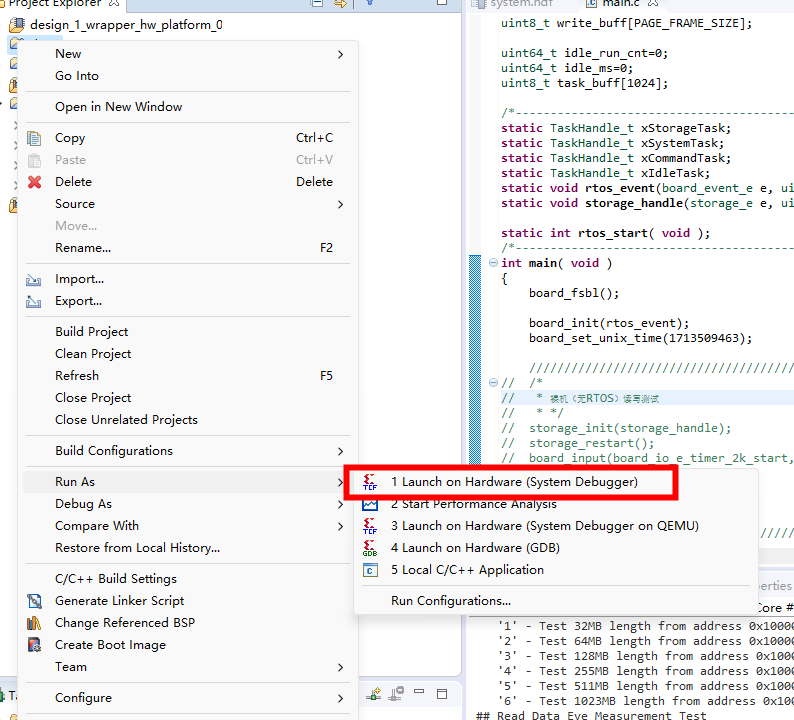

| 第一次下载,需要直接下载 |   | |

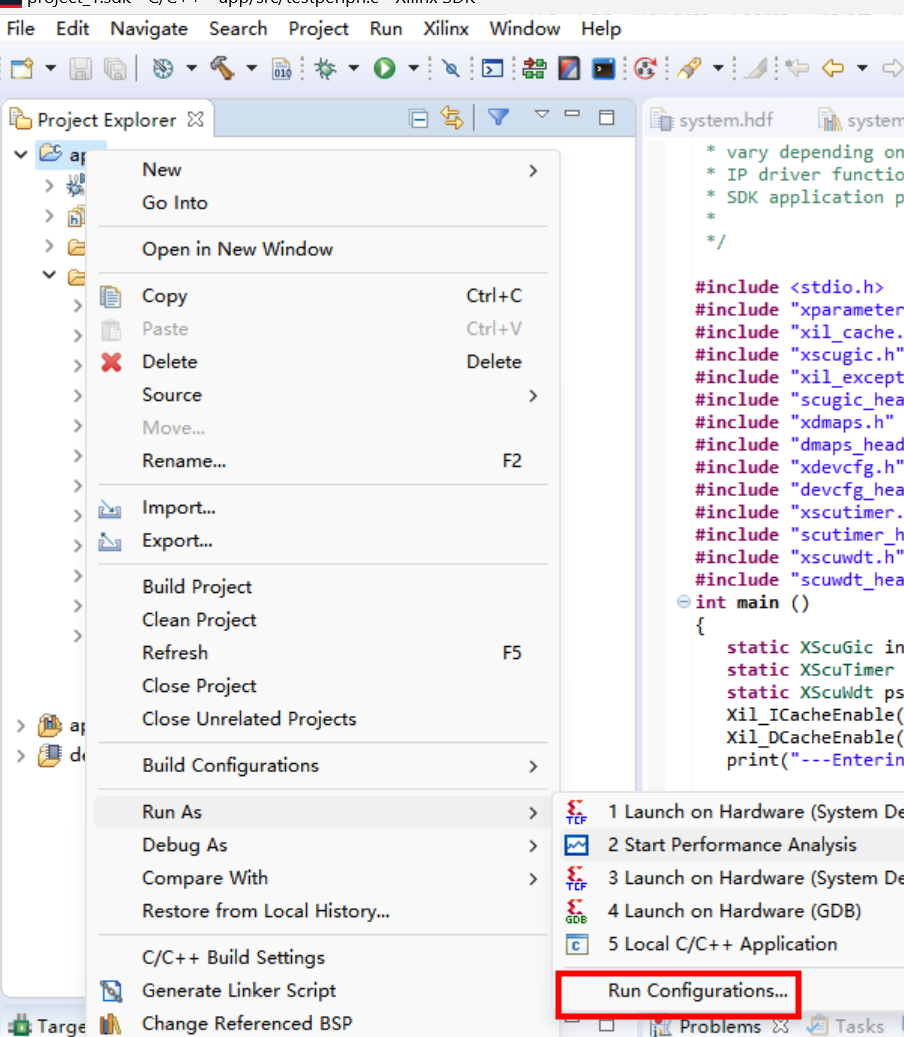

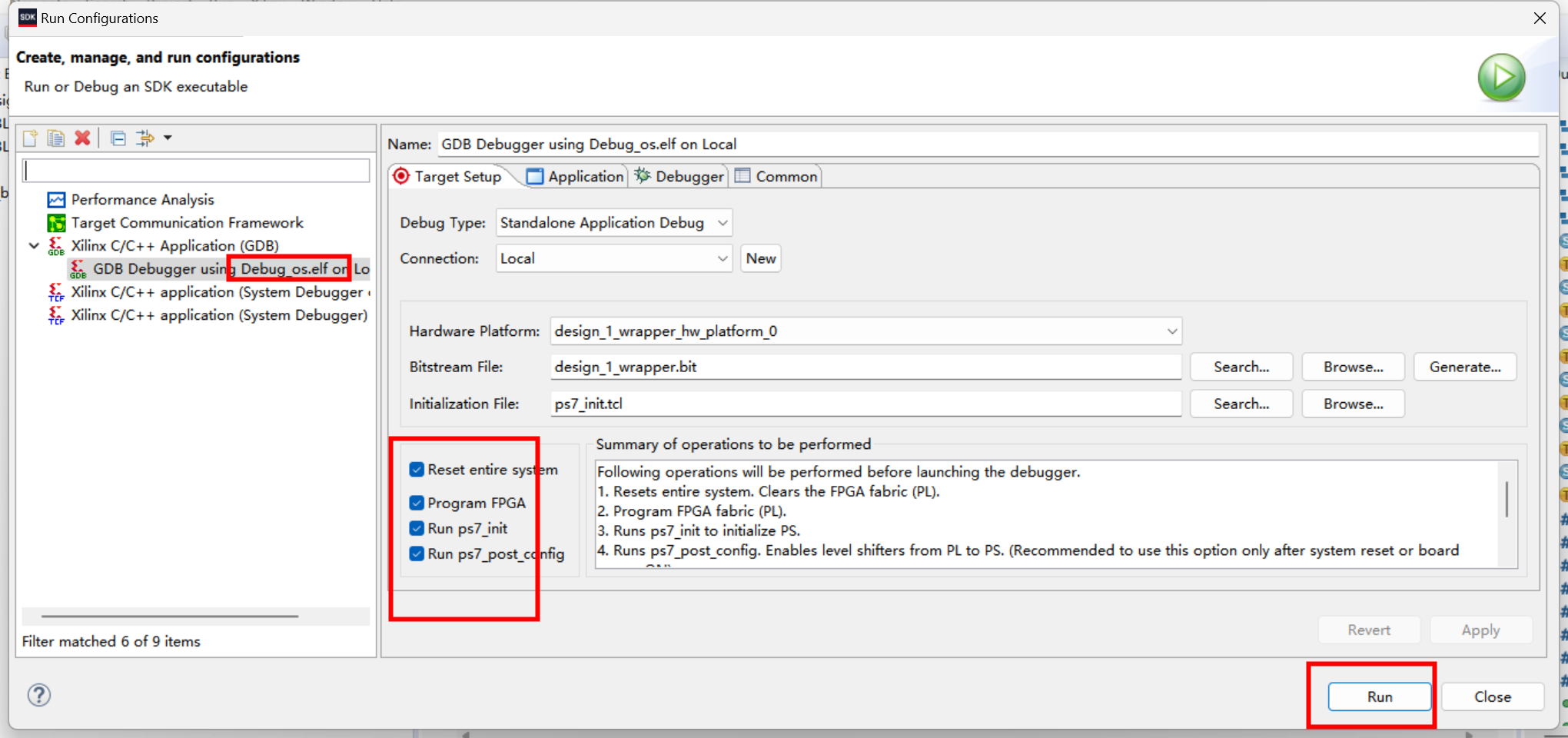

| 然后配置重启和下载FPGA数据 后续的调试就可以直接按的下载键了 |   | |

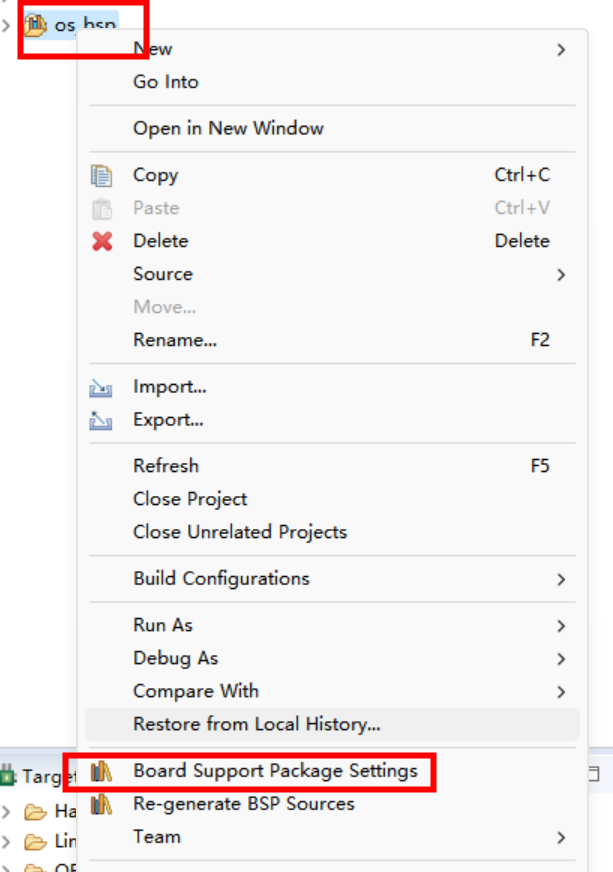

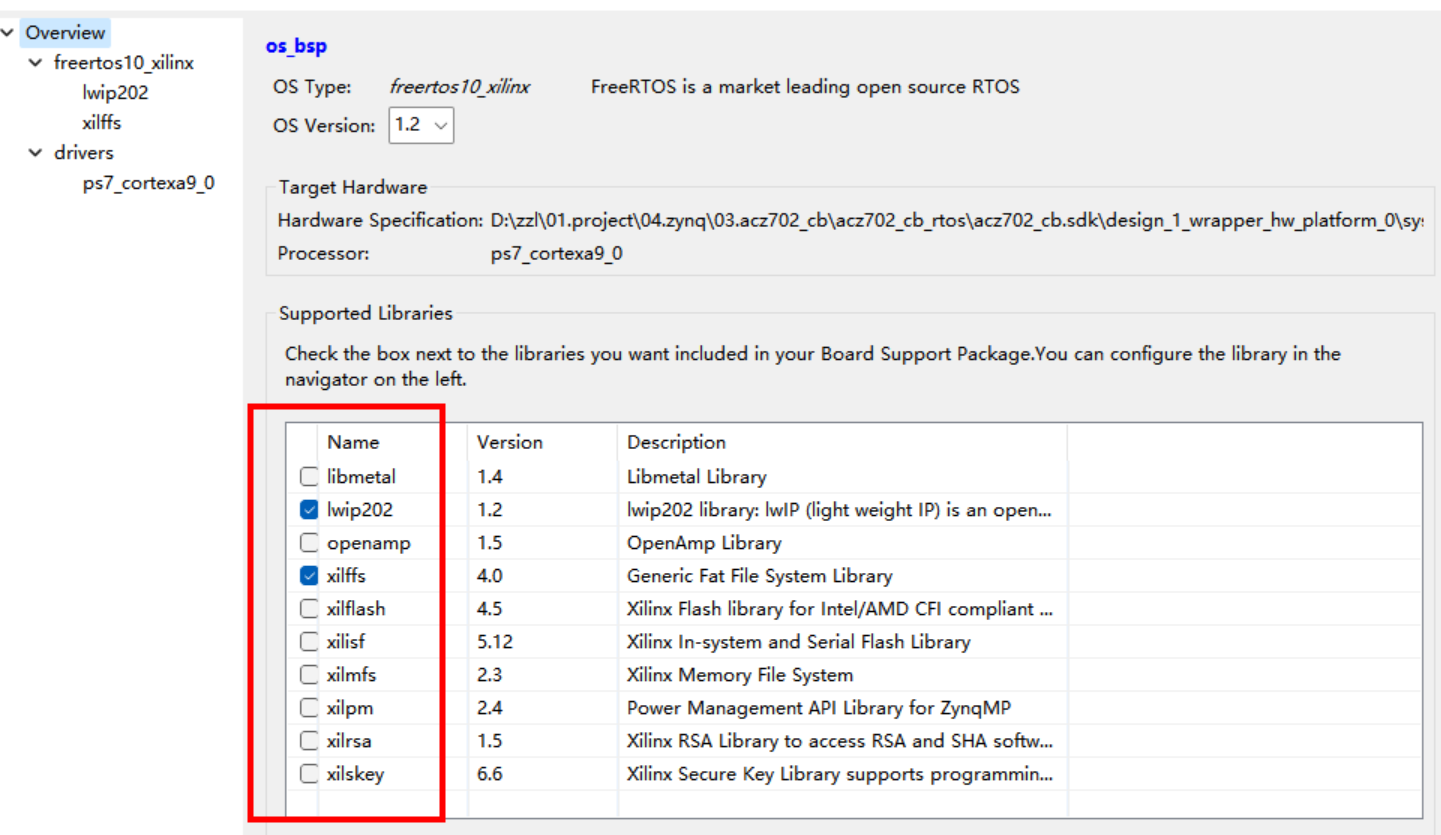

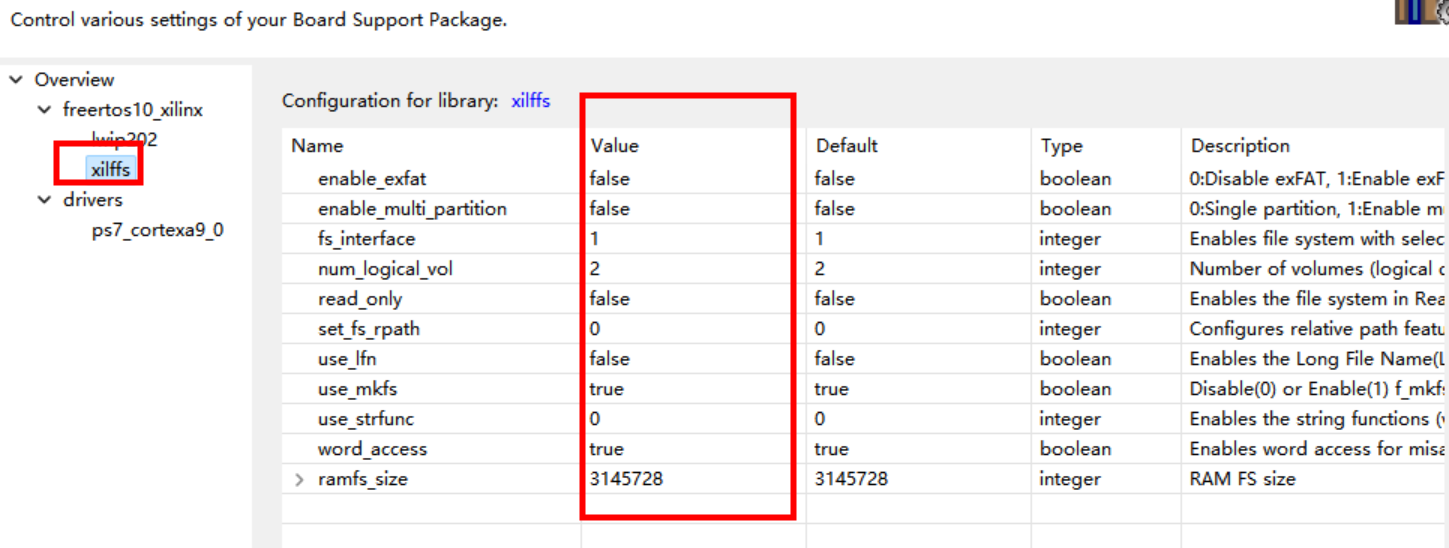

| 添加系统库 | BSP右键,选择BSP seting 可以添加不同的库函数 |   |

| 点击已有的库,可以设置库参数 |  | |

| USB复合设备开发 | 修改设备描述符 | |

| 修改 1. 配置描述符 2. 接口描述符 3. 类描述符 4. 端点描述符 | ||

| 添加端点处理 1. 端点0,枚举的step 2. 其他端点,功能函数 | ||

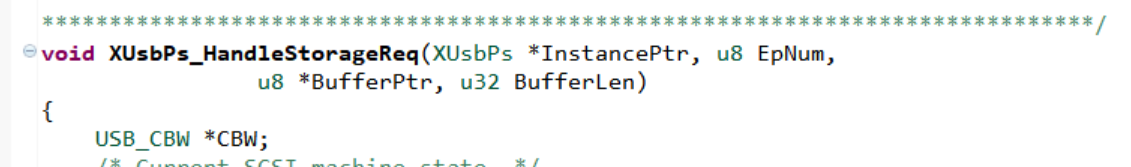

| USB大容量存储设备MSC开发 | 找到SCSI协议的handle |  |

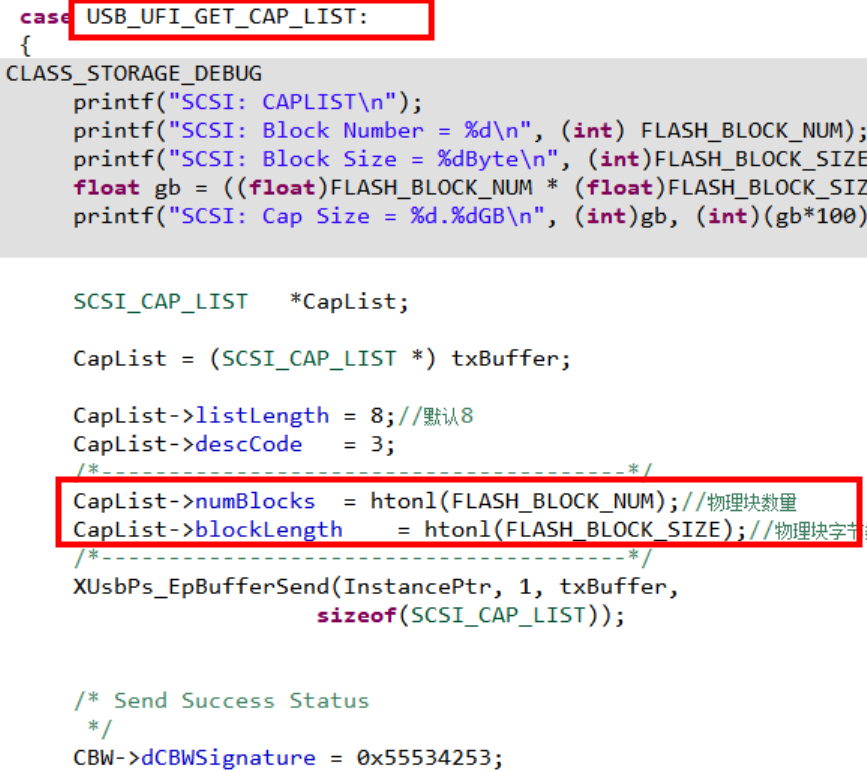

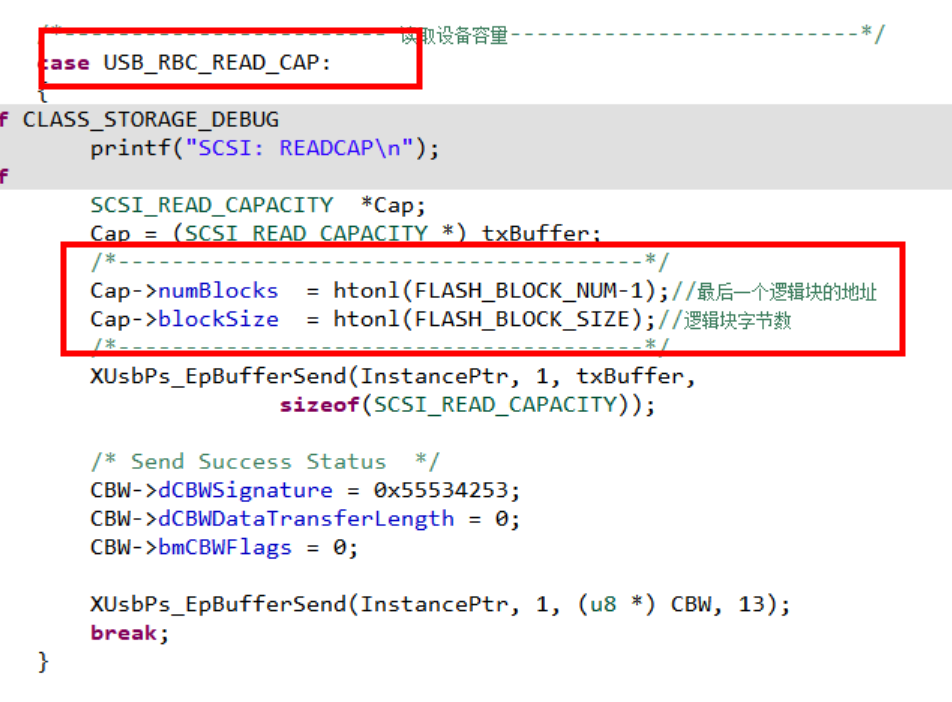

| 修改回调中,设备容量表 |  | |

| 修改回调中,设备容量 |  | |

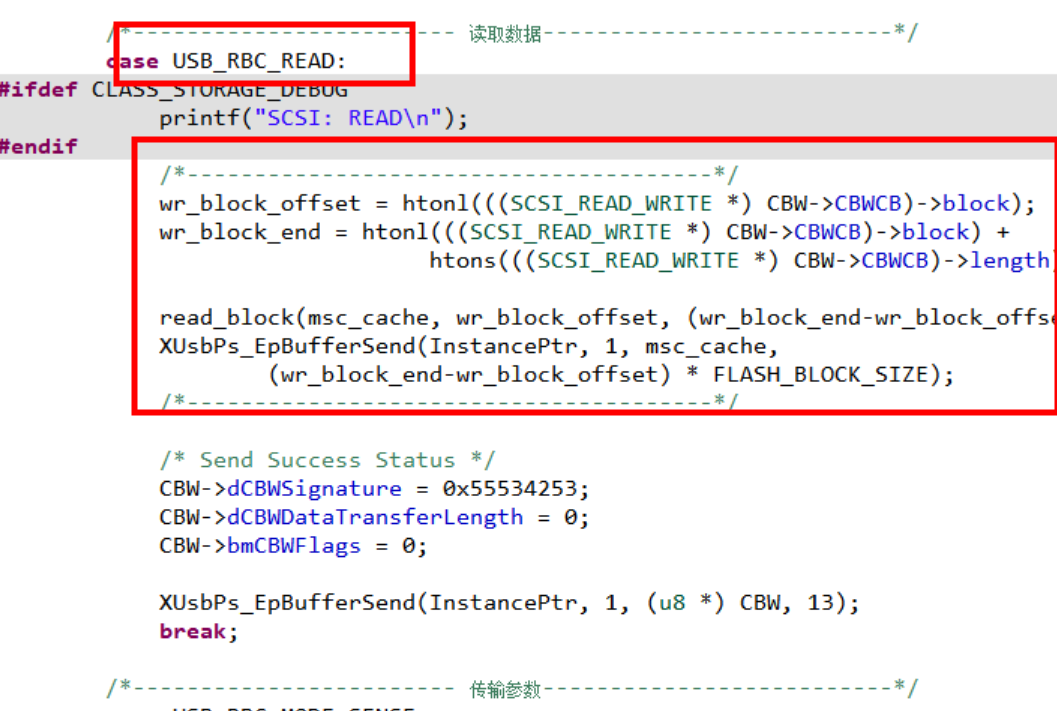

| 修改回调中,读取数据 |  | |

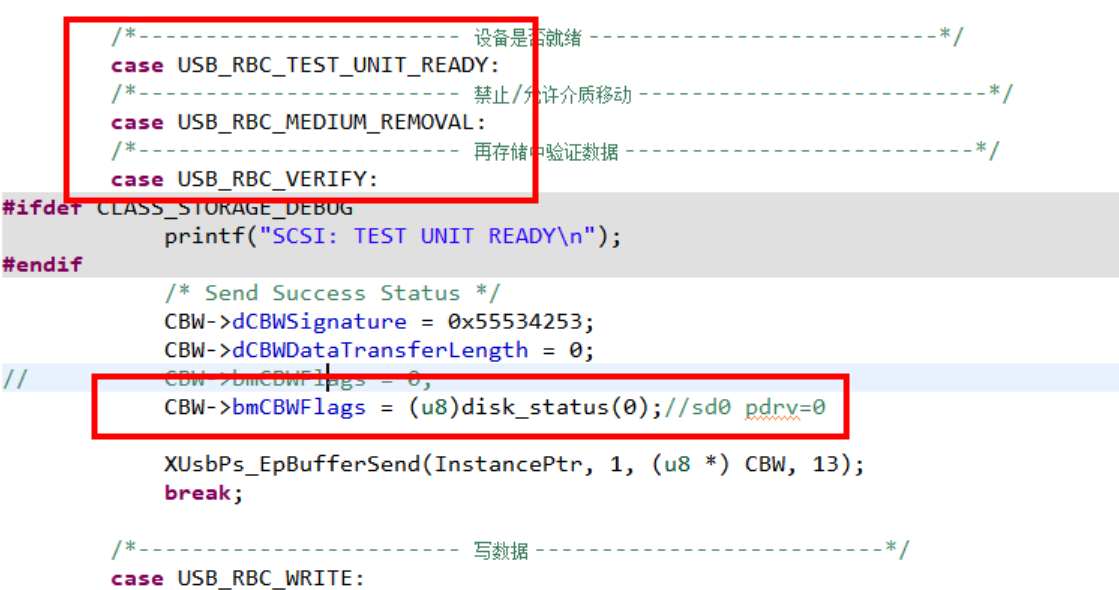

| 修改回调中,设备就绪 |  | |

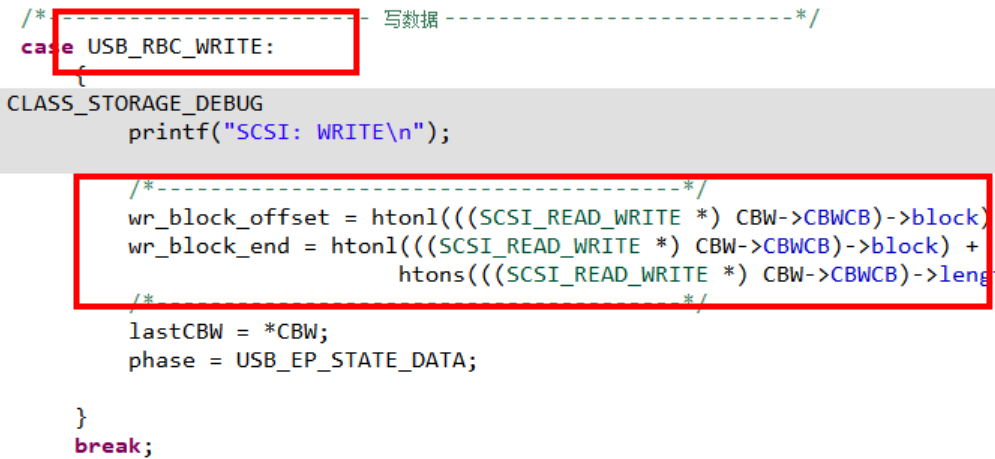

| 修改回调中,开始写入数据 |  | |

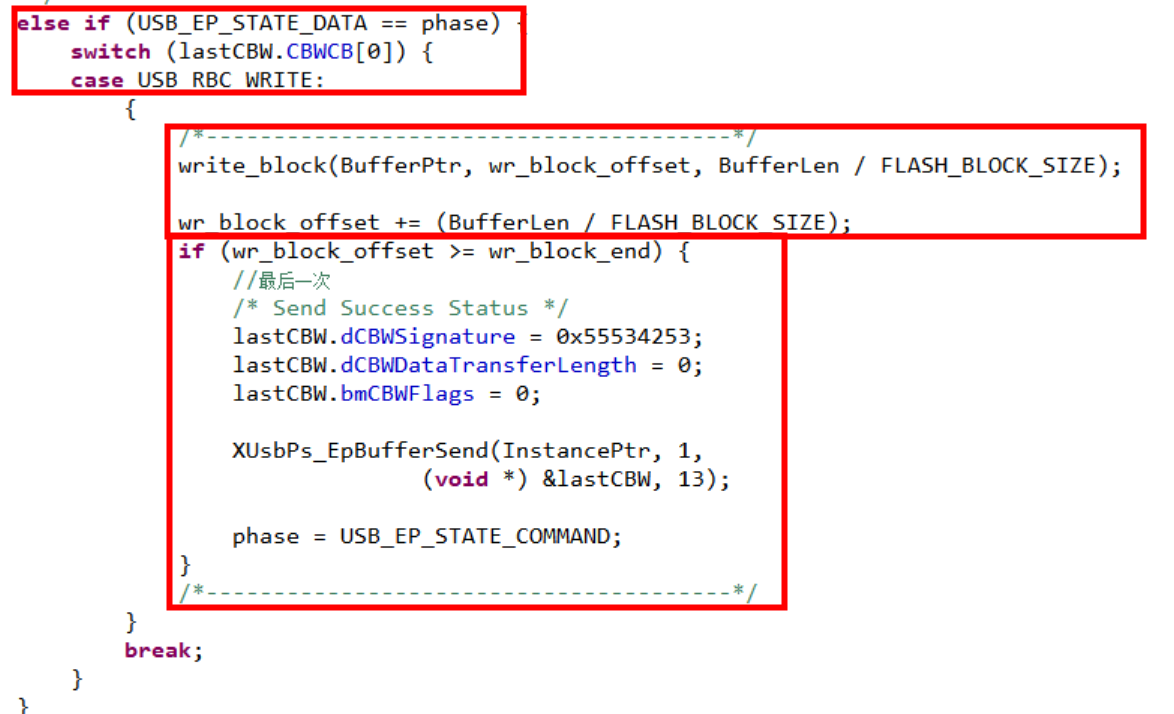

| 修改回调中,写入数据和数据写入完成 |  | |

| 以太网开发 | 配置硬件(ZYNQ ip) | |

| 跑通PHY | ||

| BSP setting中,选择LWIP协议栈 | ||

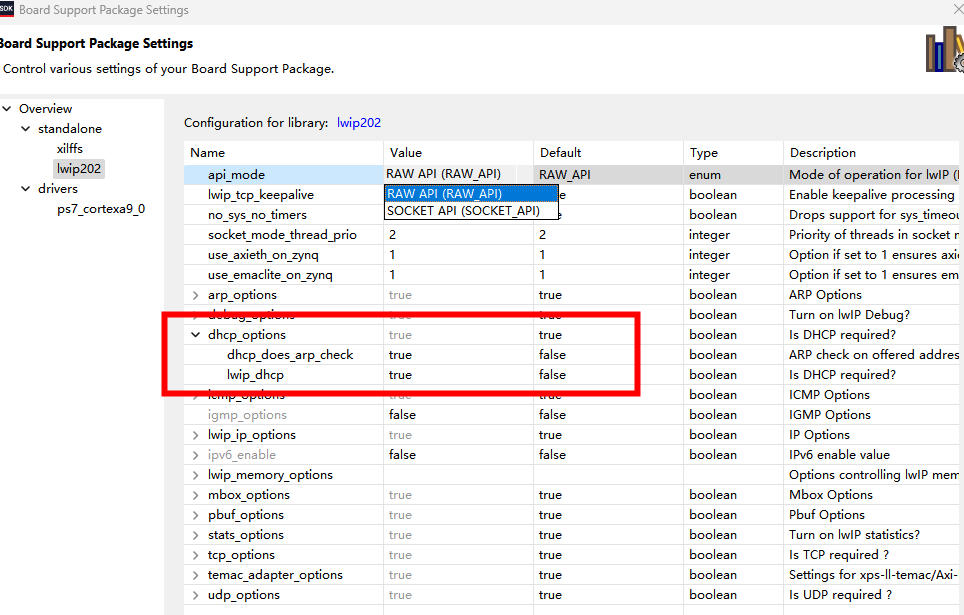

| 开启DHCP |  | |

| 新建APP,选择echo例程 | ||

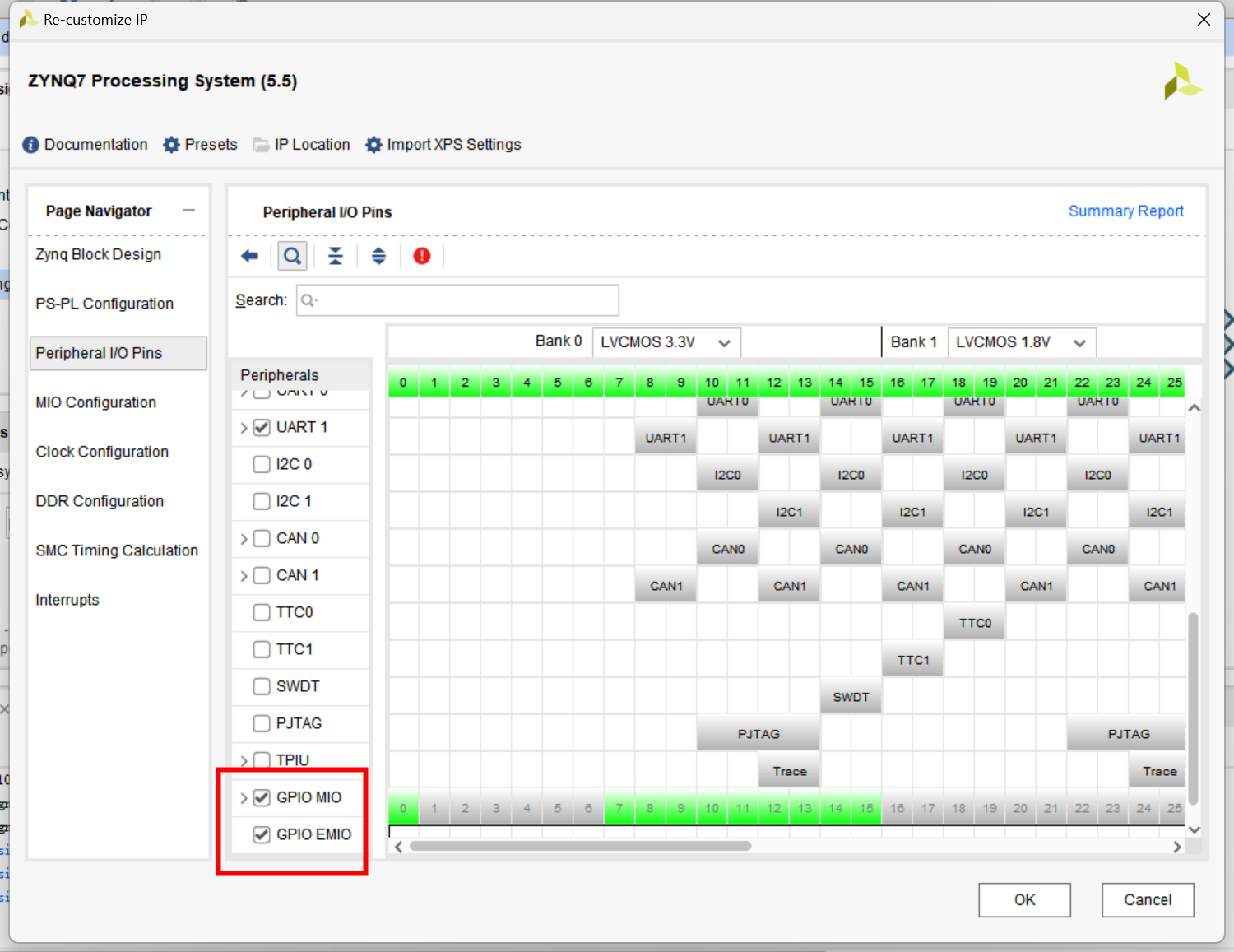

| GPIO | 勾选后,所有没有被外设占用的GPIO,都可以配置和使用 |  |

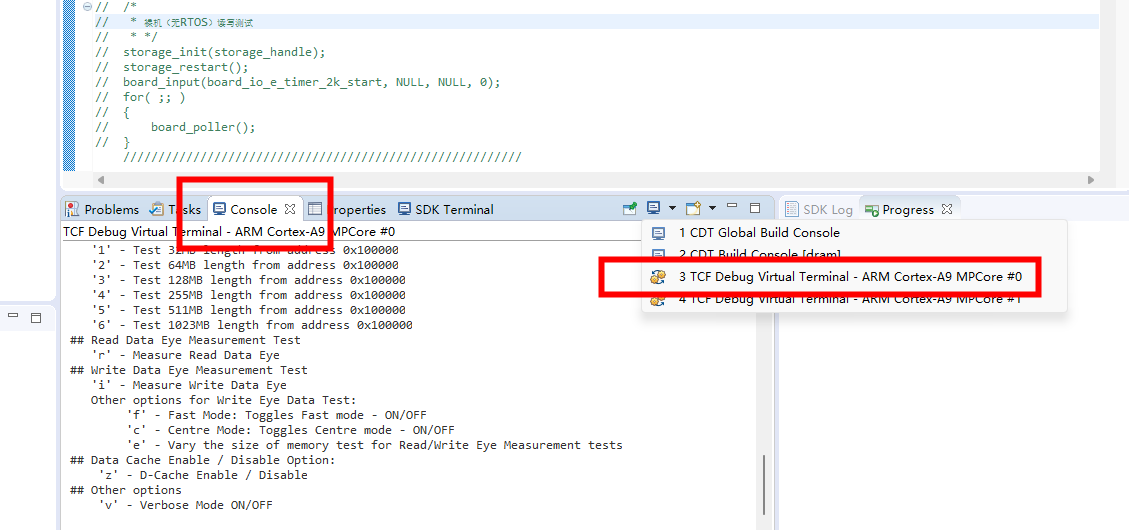

| JTAG串口 | 请教一下,在SDK中,可以运用print函数,通过JTAG,将print函数需要打印的数据,显示在console(工作台)上吗?或者有什么其他的方式显示在console上吗? (xilinx.com) |  使用系统debug 使用系统debug |

选择内核 选择内核 |

8086

8086

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?