VIVADO时序约束工具简要操作

项目简述

这里提醒,在看这篇文章之前一定要先把前一篇时序约束的文章看完,前面一篇才是重点,这篇就是一些简单的工具使用。

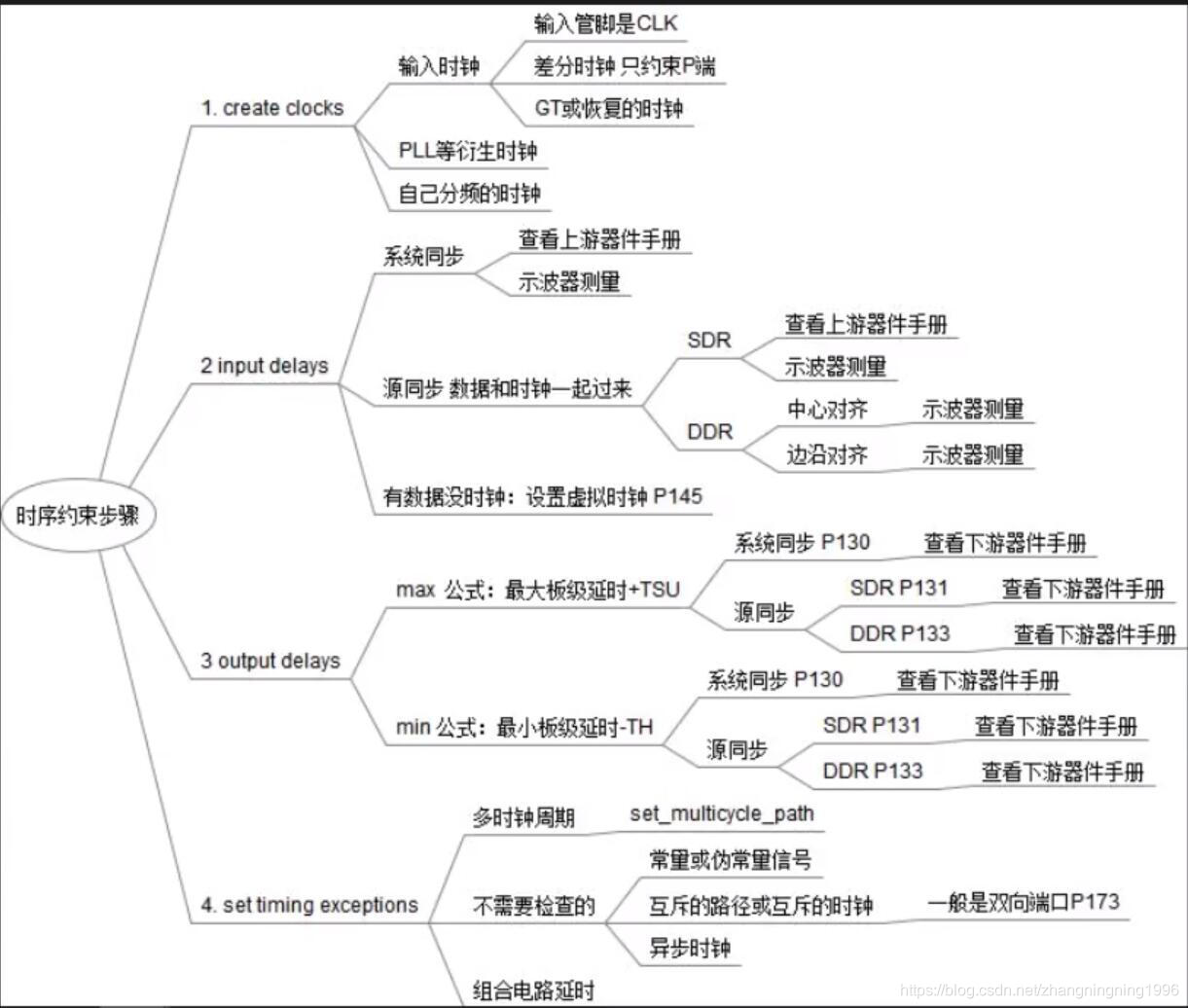

前面我们已经介绍了时序约束原理、参数的计算、Quartus II中时序约束方法。接下来,我们进行Xlinx的EDA工具VIVADO的时序约束方法。该约束方法我们将按照下图依次讲解,具体参数的计算我们在这篇博客中也将与前面的理论相联系。这篇博客中,我们分别进行原语、GUI的操作,使大家更容易明白其时序约束原理与时序参数。

基于原语的时序操作

首先这里需要注意的是,在进行时序约束之前一定要绑定引脚,否则进行的时序约束没有意义。

原语在Xlinx的工具中经常性的使用到。所谓的原语,同学们可以理解成为没有定制界面的IP,就给我们了一个顶层文件进而实现相应的功能。

时钟的约束

上面的时钟分为很多种情况,但是输入管脚是CLK、差分时钟、GT或恢复时钟是一类,另外的都属于生成时钟的种类。

输入时钟的约束

输入的时钟,使用以下原语进行约束:

create_clock -name <clock_name> -period <period> [get_ports <clock port>]

上面的 period 是时钟周期,clock port是输入时钟的管脚,clock_name是自己给这个时钟重新起的名字。

生成时钟的约束

生成时钟包括上面PLL等衍生时钟、自己分频的时钟。注意这里VIVADO对PLL的衍生时钟已经默认自己加了约束,当然我们也可以重新添加约束,约束是我们后添加的为准。

生成时钟的约束语句如下:

分频时钟:

# Generate a clock with a divided frequency from the master clock

# Generated frequency = master_clock_frequency / div_factor

create_generated_clock -name <generated_clock_name> \

-source <master_clock source_pin_or_port> \

-divide_by <div_factor> \

<pin_or_port>

上面generated_clock_name是我们对生成的时钟取得名字;master_clock source_pin_or_port这个是原时钟信号,对应于PLL的输入时钟;div_factor是分频的倍数;pin_or_port是生成的时钟信号。

倍频时钟:

# Generate a clock with a multiplied frequency from its master clock

# Generated frequency = master_clock_frequency * mult_factor

create_generated_clock -name <generated_clock_name> \

-source <master_clock source_pin_or_port> \

-multiply_by <mult_factor> \

<pin_or_port>

上面generated_clock_name是我们对生成的时钟取得名字;master_clock source_pin_or_port这个是原时钟信号,对应于PLL的输入时钟;mult_factor是倍频的倍数;pin_or_port是生成的时钟信号。

分数频时钟:

# Generated a clock with a fractional frequency of the master clock frequency:

# Generated frequency = master_clock_frequency * (mult_factor/div_factor)

create_generated_clock -name <generated_clock_name> \

-source <master_clock_source_pin_or_port> \

-multiply_by <mult_factor> \

-divide_by <div_factor> \

<pin_or_port>

上面generated_clock_name是我们对生成的时钟取得名字;master_clock source_pin_or_port这个是原时钟信号,对应于PLL的输入时钟;mult_factor是分频的倍数;div_factor是分频倍数;div_factor,pin_or_port是生成的时钟信号。

Input Delay约束

input delay的作用及计算方法在第一篇博客中我们已经进行了详细的说明。

定义1:input delay:我们在EDA软件中设置的input delay的值是以FPGA为中心,数据到达FPGA与时钟沿到达FPGA时间的差值。

由上面的定义,我们便可以得到input delay值得定义:

i n p u t d e l a y ( F P G A 为 中 心 ) = 数 据 到 达 时 间 ( F P G A 引 脚 ) − 时 钟 到 达 时 间 ( F P G A 引 脚 ) input\ delay(FPGA为中心) =数据到达时间(FPGA引脚)-时钟到达时间(FPGA引脚) input delay(FPGA为中心)=数据到达时间(FPGA引脚)−时钟到达时间(FPGA引脚)

i n p u t d e l a y ( F P G A 为 中 心 ) = T c o + T d b d − T c d − T c b d input\ delay(FPGA为中心) =Tco+Tdbd-Tcd-Tcbd input delay(FPGA为中心)=Tco+Tdbd−Tcd−Tcbd

其实对于大多数PCB板做了等长处理,所以一般 T d b d Tdbd Tdbd与 T c b d Tcbd Tcbd相等,而且 T c o − T c d Tco-Tcd Tco−Tcd在上游器件得技术手册中是给出得,一般命名为 T c o Tco Tco,那么对于PCB板做了等长处理得器件,可以得下式:

i n p u t d e l a y m a x = T c o ( m a x ) input\ delay\ max=Tco(max) input delay max=Tco(max)

i n p u t d e l a y m i n = T c o ( m i n ) input\ delay\ min=Tco(min) input delay min=Tc

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

448

448

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?