基于FPGA的以太网图片接收

项目简述

本次实验我们将完成千兆以太网接收模块的设计。上位机利用千兆以太网发送图片到FPGA开发板,并且经过DDR3缓存,最后经由USB3.0接口传输到上位机。本次实验是基于我们前面DDR3模块的基础上做的,只需要把相应的数据产生模块换成以太网接收模块即可。本次实验用到的软硬件工具如下:

1、VIVADO2019.1开发软件

2、米联客MA7035(100T)开发板

3、V3学院上位机发送软件

4、米联客上位机接收软件

上面两个上位机软件稍微有点不兼容,所以最终的实验效果有点小瑕疵,但是经过ila的抓包可以判断FPGA程序没有问题。毕竟现在在家硬件不充足,只能这样做,大家相互理解。但是经过这篇文章,大家确确实实可以学会千兆网接收的时序设计。

UDP协议讲解

因为米联客开发板上面的千兆网是RGMII接口,所以我们得使用前篇文章中设计的iddr来进行数据从双沿到单沿的转变。

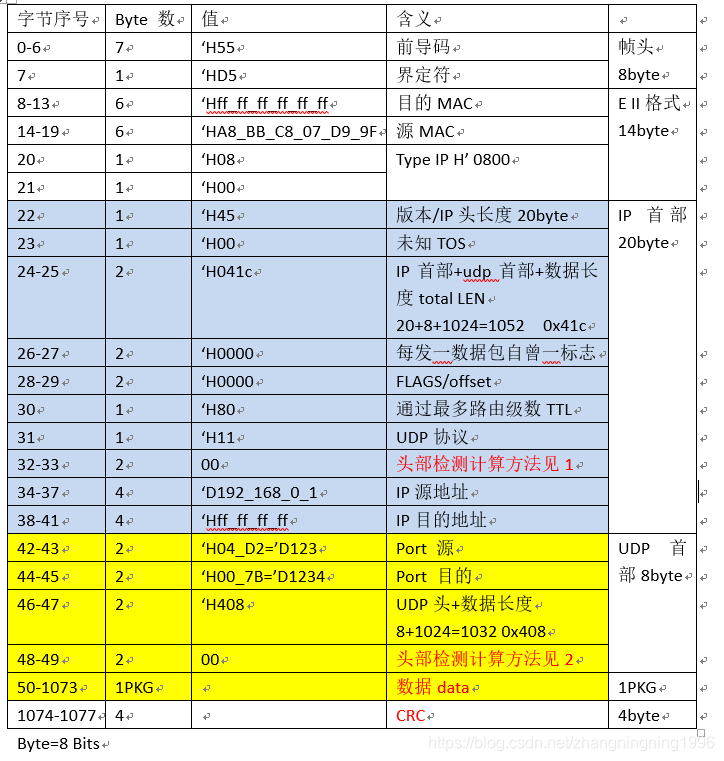

常见UDP协议的数据流每一位所占据的意义如下:

从上面我们可以学习到UDP协议的数据流含义。而且,我们可以看出以太网传输主要分为三层,即MAC层、IP层、UDP层,如下图:

IP头部checksum 算法1

把IP头部20byte 按2byte 即16bit 分开分别相加后,如果大于FFFF那么把高位与低16位相加,直到最终结果为16bit数。最后把结果取反作为ip_checksum。

例如,抓个IP数据包,取IP数据报报头部分(20B),数据如下:

45 00 00 30 80 4c 40 00 80 06 b5 2e d3 43 11 7b cb 51 15 3d

下面我来计算一下校验和:

(1)将校验和字段置为0:

将b5 2e置为00 00,即变成:

45 00 00 30 80 4c 40 00 80 06 00 00 d3 43 11 7b cb 51 15 3d

(2)反码求和

4500+0030+804c+4000+8006+0000+d343+117b+cb51+153d=34ace

将将进位(3)加到低16位(4ace)上:0003+4ace=4ad1

(3)取反码

将4ad1取反得ip_checksum=b52e

2.接收IP数据报检验IP校验和

(1)对首部中每个16 bit进行二进制反码求和;

(2)将(1)中得到的和再取反码 ,看是否为0.

接收到的IP数据报首部:

45 00 00 30 80 4c 40 00 80 06 b5 2e d3 43 11 7b cb 51 15 3d

下面来验证下:

(1)反码求和

4500+0030+804c+4000+8006+b52e+d343+117b+cb51+153d=3fffc

0003+fffc=ffff

(2)取反码:~ffff=0 正确

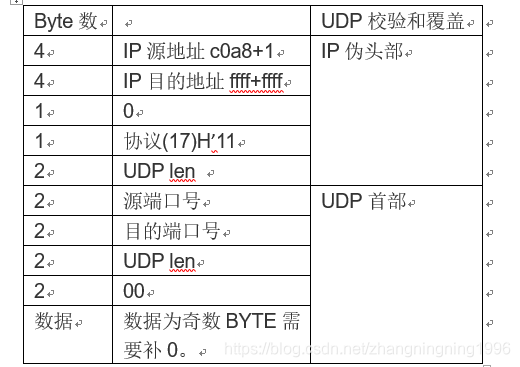

UDP checksum 计算方法

UDP _sum=(Ip伪头部+(UDP首部+数据 每两个字节拼接分别相加的和))

头包:ip伪头部=c0a8+0001+ffff+ffff+0011+0108

数据包1:ip伪头部=c0a8+0001+ffff+ffff+0011+04c2

数据包2:ip伪头部=c0a8+0001+ffff+ffff+0011+04c2

数据包3:ip伪头部=c0a8+0001+ffff+ffff+0011+02b2

以太网(IEEE 802.3)帧格式:

1、前导码:7字节0x55,一串1、0间隔,用于信号同步 有的说是AA

2、帧起始定界符:1字节0xD5(10101011),表示一帧开始 有的说是AB

3、DA(目的MAC):6字节 如果设置为全1 为广播包

4、SA(源MAC):6字节

5、类型/长度:2字节,0~1500保留为长度域值,1536~65535保留为类型域值(0x0600~0xFFFF)

6、数据:46~1500字节

7、帧校验序列(FCS):4字节,使用CRC计算从目的MAC到数据域这部分内容而得到的校验和。

以CSMA/CD作为MAC算法的一类LAN称为以太网。CSMA/CD冲突避免的方法:先听后发、边听边发、随机延迟后重发。一旦发生冲突,必须让每台主机都能检测到。关于最小发送间隙和最小帧长的规定也是为了避免冲突。

考虑如下极限的情况,主机发送的帧很小,而两台冲突主机相距很远。 在主机A发送的帧传输到B的前一刻,B开始发送帧。这样,当A的帧到达B时,B检测到冲突,于是发送冲突信号。假如在B的冲突信号传输到A之前,A的帧已 经发送完毕,那么A将检测不到冲突而误认为已发送成功。由于信号传播是有时延的,因此检测冲突也需要一定的时间。这也是为什么必须有个最小帧长的限制。

按照标准,10Mbps以太网采用中继器时,连接的最大长度是 2500米,最多经过4个中继器,因此规定对10Mbps以太网一帧的最小发送时间为51.2微秒。这段时间所能传输的数据为512位,因此也称该时间为 512位时。这个时间定义为以太网时隙,或冲突时槽。512位=64字节,这就是以太网帧最小64字节的原因。

512位时是主机捕获信道的时间。如果某主机发送一个帧的64字节仍无冲突,以后也就不会再发生冲突了,称此主机捕获了信道。由于信道是所有主机共享的,为避免单一主机占用信道时间过长,规定了以太网帧的最大帧长为1500。

100Mbps以太网的时隙仍为512位时,以太网规定一帧的最小发送时间必须为5.12μs。

1000Mbps以太网的时隙增至512字节,即4096位时,4.096μs。

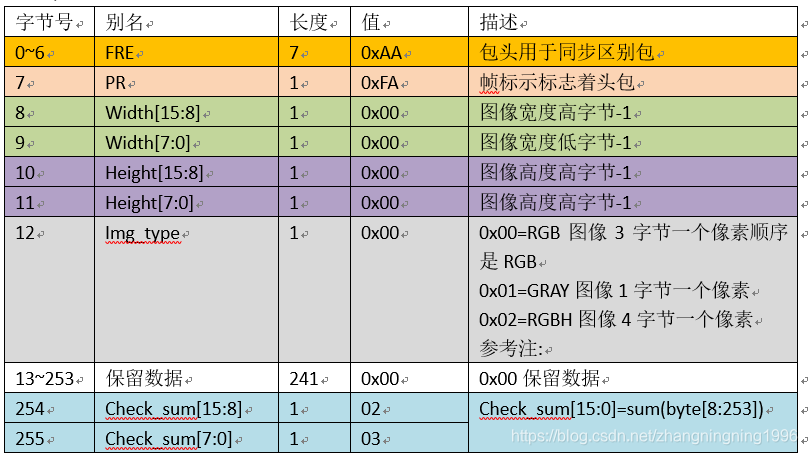

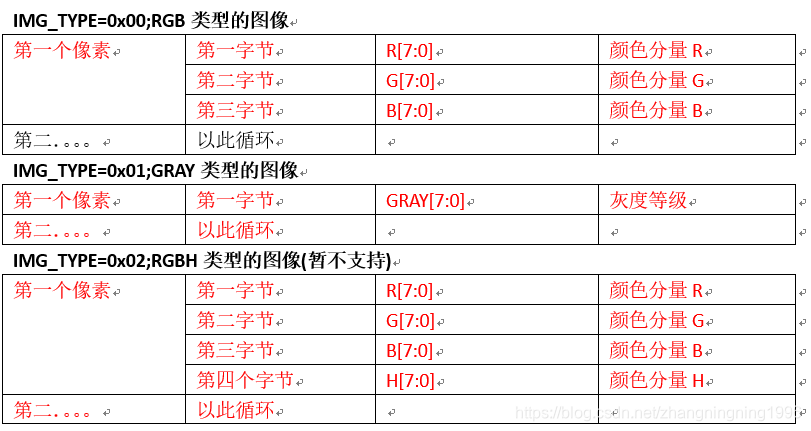

V3学院的上位机传送图像数据的数据流

图像数据在千兆以太网数据流中所在的位置是在上面50~1073里面,主要分为图像的数据头包与图像的数据包。这里说明一下,下面的数据协议都是自己定义的,可以根据不同的需求编写不同的协议,同时编写相应的上位机。数据头包是指在发送第一行图像数据前发送的帧头数据,标志着下一包图像数据即将到来。

注:check sum 计算是把一帧内第8字节到第253字节之和的低16位作为check_sum,为了给软件提供校验帧数据的作用,校验方法判断接收端计算的check_sum和接收到的check_sum是否一致。03+FF+02+FF=104+FF=’h203

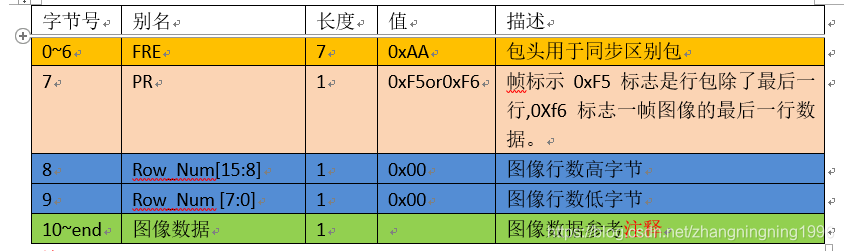

图像行数据帧

跟在数据头包之后的图像行数据包,一次发送一行图像数据。

如果RGB图像一行超过400pixel需要把一行像素分包发送,由于每个UDP包不能超过1.5k长度。

限定最大发送图像宽度为1200pixel

小于等于400pixel 发送一个udp包

大于400小于等于800pixel分两个udp包发送

大于800小于等于1200pixel分三个udp包发送

这里也讲解一下对图像数据进行上面编码的作用:因为电脑随机会产生一些冗余的以太网包,那么如何去除相应的废包,一个方法就是进行编码,当然也可以通过使用指定phy芯片的MAC地址的方法。但是在本次实验中,我们使用的是广播包的形式,所以只有通过编码进行相应冗余包的处理。

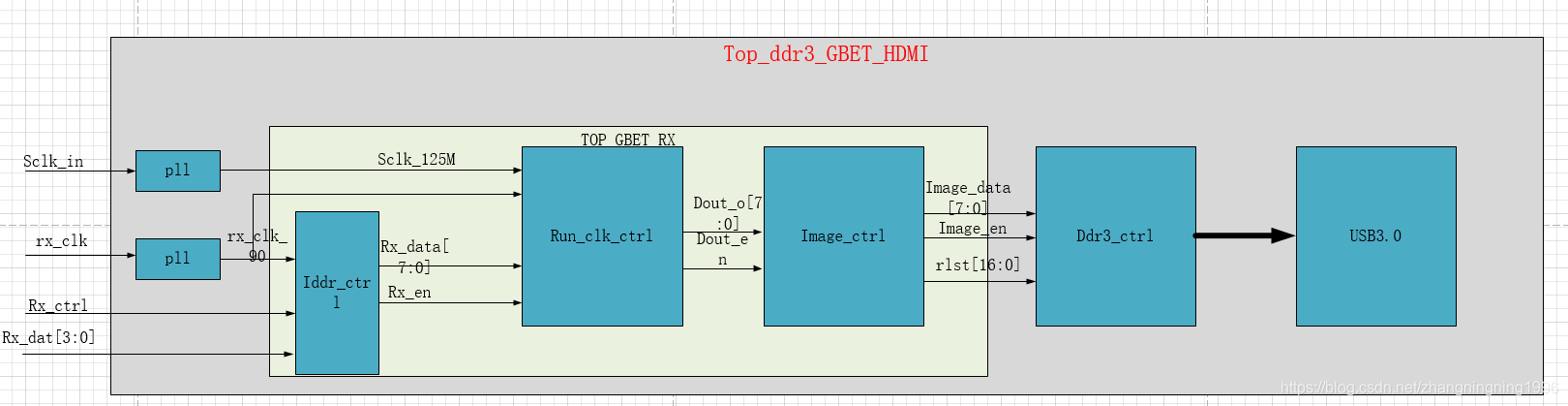

项目的实验框图

接下来为了让同学们方便理解这个项目的流程,我们给出相应的系统框图如下:

这里简述一下几个模块的功能:

1、Iddr_ctrl模块:使用RGMII相移90度的时钟将双沿数据转化成单沿数据,注意这里使用相移90度的原因是为了采集数据的稳定性。

2、Run_clk_ctrl:这个模块的设计思想特别重要,是处理跨时钟域最常见的处理方法,将RGMII的时钟域转换到系统时钟域,特别特别重要

3、Image_ctrl模块:将上面用户进行编码的图像数据进行相应的译码,然后放到DDR3中进行缓存。4、4、Ddr3_ctrl模块:DDR3的驱动模块,进行数据的读取与写出。

5、USB3.0模块:将图像数据经由USB3.0传输到上位机中去。

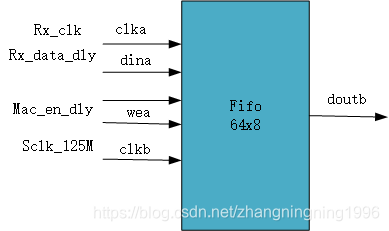

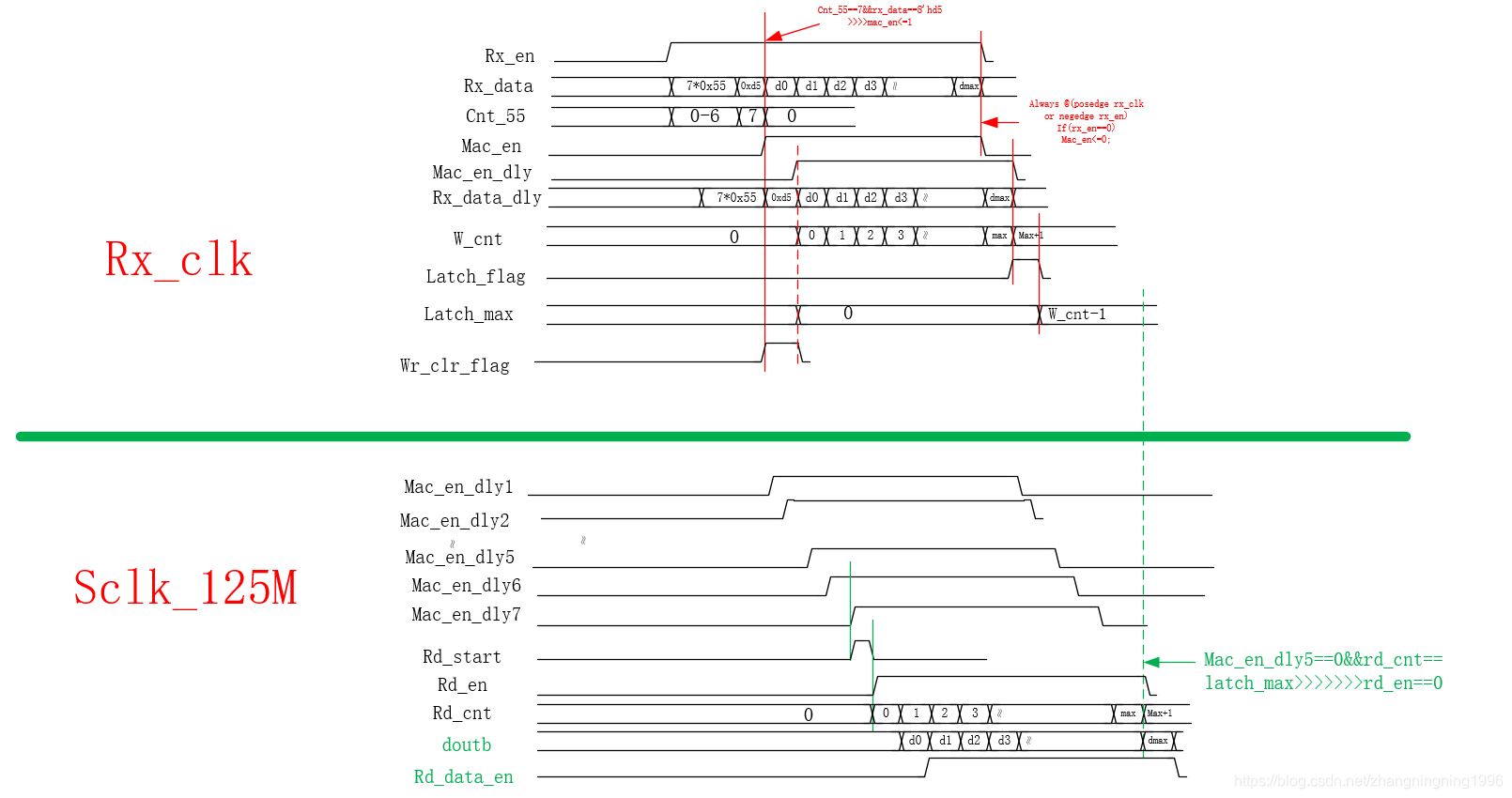

跨时钟域处理时序图

这里的跨时钟域处理特别重要,主要包括上面的run_clk_ctrl、pll、iddr_ctrl模块,其中pll就是调用pll的IP实现移位90度,iddr_ctrl前面的博客我们已经讲解过,那么接下来我们主要讲解run_clk_ctrl模块的时序图。

时序图如下:

从上面的原理我们可以看出这次的跨时钟域处理主要是利用FIFO来实现的,其中上面mac_en_dly移位了8拍是为了同步同时是为了让后面进行处理时,latch_max已经有效供我们去除CRC校验位。

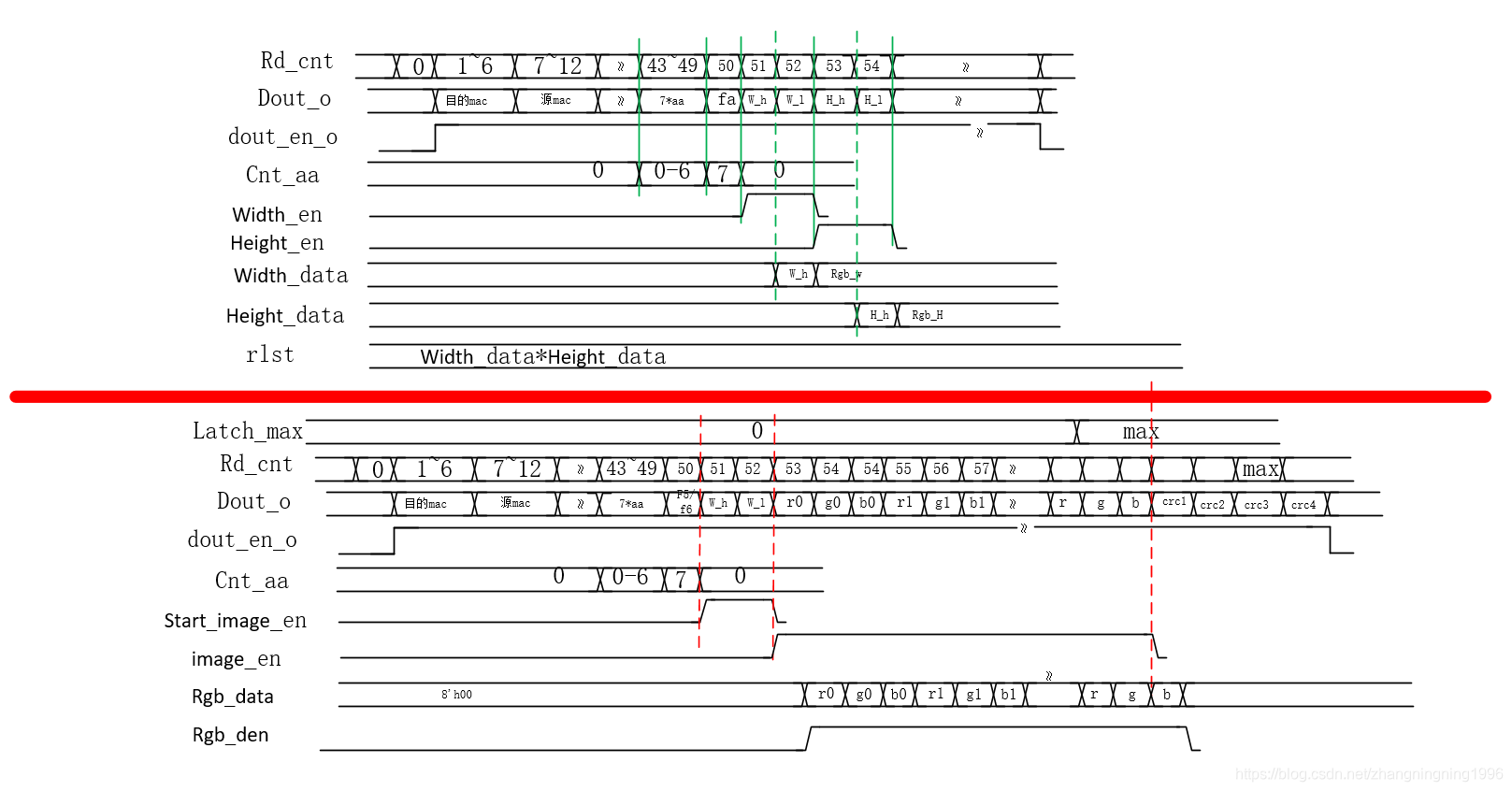

Image_ctrl时序图

该模块是为了解码出相应图像数据,具体的时序图如下:

经过上面的时序图,相信大家可以很简单写出时序图。接下来,我们给出相应的代码。

工程代码

top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : top.v

// Create Time : 2020-03-01 20:33:42

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module top(

//System Interfaces

input sclk ,

input rst_n ,

//DDR3 Interfaces

output wire [13:0] ddr3_addr ,

output wire [ 2:0] ddr3_ba ,

output wire ddr3_cas_n ,

output wire ddr3_ck_n ,

output wire ddr3_ck_p ,

output wire ddr3_cke ,

output wire ddr3_ras_n ,

output wire ddr3_reset_n ,

output wire ddr3_we_n ,

inout [31:0] ddr3_dq ,

inout [ 3:0] ddr3_dqs_n ,

inout [ 3:0] ddr3_dqs_p ,

output wire [ 0:0] ddr3_cs_n ,

output wire [ 3:0] ddr3_dm ,

output wire [ 0:0] ddr3_odt ,

//Gigbit Interfaces

output wire phy_rst_n ,

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk ,

//USB3 Interfaces

output wire USBSS_EN ,

input USB_clk ,

inout [15:0] data ,

inout [ 1:0] be ,

input rxf_n ,

input txf_n ,

output wire oe_n ,

output wire wr_n ,

output wire siwu_n ,

output wire rd_n ,

output wire wakeup ,

output wire [ 1:0] gpio

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//clk_wiz_0_inst

wire clk_200m ;

wire locked ;

wire clk_125m ;

//ddr3_drive_inst

wire init_calib_complete ;

wire c3_p0_cmd_clk ;

wire c3_p0_cmd_en ;

wire [ 2:0] c3_p0_cmd_instr ;

wire [27:0] c3_p0_cmd_byte_addr ;

wire [ 6:0] c3_p0_cmd_bl ;

wire c3_p0_wr_clk ;

wire c3_p0_wr_en ;

wire [31:0] c3_p0_wr_mask ;

wire [255:0] c3_p0_wr_data ;

wire [10:0] c3_p0_wr_count ;

wire c3_p1_cmd_clk ;

wire c3_p1_cmd_en ;

wire [ 2:0] c3_p1_cmd_instr ;

wire [27:0] c3_p1_cmd_byte_addr ;

wire [ 6:0] c3_p1_cmd_bl ;

wire c3_p1_rd_clk ;

wire c3_p1_rd_en ;

wire [255:0] c3_p1_rd_data ;

wire [10:0] c3_p1_rd_count ;

//sensor_data_gen_inst

wire clk_24m ;

wire data_wr_en ;

wire [31:0] data_wr ;

//usb3_drive_inst

wire [15:0] data_in ;

wire data_req ;

wire [ 7:0] image_data ;

wire image_data_en ;

wire [31:0] rlst ;

wire rlst_flag ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

clk_wiz_0 clk_wiz_0_inst(

// Clock out ports

.clk_out1 (clk_200m ), // output clk_out1

.clk_out2 (clk_125m ),

.clk_out3 (clk_50m ),

// Status and control signals

.reset (~rst_n ), // input reset

.locked (locked ), // output locked

// Clock in ports

.clk_in1 (sclk )

); // input clk_in1

ddr3_top ddr3_top_inst(

//System Interfaces

.rst_n (rst_n ),

.locked (locked ),

.clk_200m (clk_200m ),

//DDR3 Interfaces

.ddr3_addr (ddr3_addr ),

.ddr3_ba (ddr3_ba ),

.ddr3_cas_n (ddr3_cas_n ),

.ddr3_ck_n (ddr3_ck_n ),

.ddr3_ck_p (ddr3_ck_p ),

.ddr3_cke (ddr3_cke ),

.ddr3_ras_n (ddr3_ras_n ),

.ddr3_reset_n (ddr3_reset_n ),

.ddr3_we_n (ddr3_we_n ),

.ddr3_dq (ddr3_dq ),

.ddr3_dqs_n (ddr3_dqs_n ),

.ddr3_dqs_p (ddr3_dqs_p ),

.ddr3_cs_n (ddr3_cs_n ),

.ddr3_dm (ddr3_dm ),

.ddr3_odt (ddr3_odt ),

//User Interfaces

.init_calib_complete (init_calib_complete ),

.c3_p0_cmd_clk (c3_p0_cmd_clk ),

.c3_p0_cmd_en (c3_p0_cmd_en ),

.c3_p0_cmd_bl (c3_p0_cmd_bl ),

.c3_p0_cmd_byte_addr (c3_p0_cmd_byte_addr ),

.c3_p0_cmd_empty ( ),

.c3_p0_cmd_full ( ),

.c3_p0_wr_clk (c3_p0_wr_clk ),

.c3_p0_wr_en (c3_p0_wr_en ),

.c3_p0_wr_mask (c3_p0_wr_mask ),

.c3_p0_wr_data (c3_p0_wr_data ),

.c3_p0_wr_full ( ),

.c3_p0_wr_empty ( ),

.c3_p0_wr_count (c3_p0_wr_count ),

.c3_p1_cmd_clk ('d0 ),

.c3_p1_cmd_en ('d0 ),

.c3_p1_cmd_bl ('d0 ),

.c3_p1_cmd_byte_addr ('d0 ),

.c3_p1_cmd_empty ( ),

.c3_p1_cmd_full ( ),

.c3_p1_wr_clk ('d0 ),

.c3_p1_wr_en ('d0 ),

.c3_p1_wr_mask ('d0 ),

.c3_p1_wr_data ('d0 ),

.c3_p1_wr_full ( ),

.c3_p1_wr_empty ( ),

.c3_p1_wr_count ( ),

.c3_p2_cmd_clk (c3_p1_cmd_clk ),

.c3_p2_cmd_en (c3_p1_cmd_en ),

.c3_p2_cmd_bl (c3_p1_cmd_bl ),

.c3_p2_cmd_byte_addr (c3_p1_cmd_byte_addr ),

.c3_p2_cmd_empty ( ),

.c3_p2_cmd_full ( ),

.c3_p2_rd_clk (c3_p1_rd_clk ),

.c3_p2_rd_en (c3_p1_rd_en ),

.c3_p2_rd_data (c3_p1_rd_data ),

.c3_p2_rd_full ( ),

.c3_p2_rd_empty ( ),

.c3_p2_rd_count (c3_p1_rd_count ),

.c3_p3_cmd_clk ('d0 ),

.c3_p3_cmd_en ('d0 ),

.c3_p3_cmd_bl ('d0 ),

.c3_p3_cmd_byte_addr ('d0 ),

.c3_p3_cmd_empty ( ),

.c3_p3_cmd_full ( ),

.c3_p3_rd_clk ('d0 ),

.c3_p3_rd_en ('d0 ),

.c3_p3_rd_data ( ),

.c3_p3_rd_full ( ),

.c3_p3_rd_empty ( ),

.c3_p3_rd_count ( )

);

ddr3_drive ddr3_drive_inst(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.c3_p0_cmd_clk (c3_p0_cmd_clk ),

.c3_p0_cmd_en (c3_p0_cmd_en ),

.c3_p0_cmd_instr (c3_p0_cmd_instr ),

.c3_p0_cmd_byte_addr (c3_p0_cmd_byte_addr ),

.c3_p0_cmd_bl (c3_p0_cmd_bl ),

.c3_p0_wr_clk (c3_p0_wr_clk ),

.c3_p0_wr_en (c3_p0_wr_en ),

.c3_p0_wr_mask (c3_p0_wr_mask ),

.c3_p0_wr_data (c3_p0_wr_data ),

.c3_p0_wr_count (c3_p0_wr_count ),

.c3_p1_cmd_clk (c3_p1_cmd_clk ),

.c3_p1_cmd_en (c3_p1_cmd_en ),

.c3_p1_cmd_instr (c3_p1_cmd_instr ),

.c3_p1_cmd_byte_addr (c3_p1_cmd_byte_addr ),

.c3_p1_cmd_bl (c3_p1_cmd_bl ),

.c3_p1_rd_clk (c3_p1_rd_clk ),

.c3_p1_rd_en (c3_p1_rd_en ),

.c3_p1_rd_data (c3_p1_rd_data ),

.c3_p1_rd_count (c3_p1_rd_count ),

//Write DDR3

.clk_24m (clk_125m ),

.data_wr_en (data_wr_en ),

.data_wr (data_wr ),

////Read DDR3

.USB_clk (USB_clk ),

.wr_n (data_req ),

.data_in (data_in )

);

gbit_top gbit_top_inst(

//System Interfaces

.clk_50m (clk_50m ),

.clk_125m (clk_125m ),

.rst_n (locked ),

//Gigbit Interfaces

.phy_rst_n (phy_rst_n ),

.rx_data (rx_data ),

.rx_ctrl (rx_ctrl ),

.rx_clk (rx_clk ),

//Communication Interfaces

.image_data (image_data ),

.image_data_en (image_data_en ),

.rlst (rlst ),

.rlst_flag (rlst_flag )

);

conver_bit conver_bit_inst(

//System Interfaces

.sclk (clk_125m ),

.rst_n (locked ),

//Gigbit Interfaces

.image_data (image_data ),

.image_data_en (image_data_en ),

//Communication Interfaces

.rgb_data ({

data_wr[15:8],data_wr[23:16],data_wr[31:24],data_wr[7:0]} ),

.rgb_data_en (data_wr_en )

);

//sensor_data_gen sensor_data_gen_inst(

// .clk (clk_24m ),

// .rst_n (init_calib_complete ),

// .rgb ({data_wr[15:0],data_wr[31:16]} ),

// .de (data_wr_en ),

// .vsync ( ),

// .hsync ( )

//);

//lways @(posedge clk_24m)

// if(init_calib_complete == 1'b0)

// data_wr_en <= 1'b0;

// else

// data_wr_en <= 1'b1;

//lways @(posedge clk_24m)

// if(init_calib_complete == 1'b0)

// data_wr <= 32'd0;

// else if(data_wr_en == 1'b1)

// data_wr <= data_wr + 1'b1;

usb3_drive usb3_drive_inst(

//System Interfaces

.rst_n (init_calib_complete ),

//USB3 Interfaces

.USBSS_EN (USBSS_EN ),

.sclk (USB_clk ),

.data (data ),

.be (be ),

.rxf_n (rxf_n ),

.txf_n (txf_n ),

.oe_n (oe_n ),

.wr_n (wr_n ),

.siwu_n (siwu_n ),

.rd_n (rd_n ),

.wakeup (wakeup ),

.gpio (gpio ),

//Communication Interfaces

.data_in (data_in ),

.data_req (data_req )

);

//========================================================================================\

//******************************* Debug **********************************

//========================================================================================/

ila_3 ila_3_inst (

.clk (clk_125m ), // input wire clk

.probe0 (image_data ), // input wire [7:0] probe0

.probe1 (image_data_en ), // input wire [0:0] probe1

.probe2 (data_wr ), // input wire [31:0] probe2

.probe3 (data_wr_en ) // input wire [0:0] probe3

);

endmodule

ddr3_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : ddr3_top.v

// Create Time : 2020-02-27 23:16:16

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module ddr3_top(

//System Interfaces

input rst_n ,

input locked ,

input clk_200m ,

//DDR3 Interfaces

output wire [13:0] ddr3_addr ,

output wire [ 2:0] ddr3_ba ,

output wire ddr3_cas_n ,

output wire ddr3_ck_n ,

output wire ddr3_ck_p ,

output wire ddr3_cke ,

output wire ddr3_ras_n ,

output wire ddr3_reset_n ,

output wire ddr3_we_n ,

inout [31:0] ddr3_dq ,

inout [ 3:0] ddr3_dqs_n ,

inout [ 3:0] ddr3_dqs_p ,

output wire [ 0:0] ddr3_cs_n ,

output wire [ 3:0] ddr3_dm ,

output wire [ 0:0] ddr3_odt ,

//User Interfaces

output wire init_calib_complete ,

input c3_p0_cmd_clk ,

input c3_p0_cmd_en ,

input [ 6:0] c3_p0_cmd_bl ,

input [27:0] c3_p0_cmd_byte_addr ,

output wire c3_p0_cmd_empty ,

output wire c3_p0_cmd_full ,

input c3_p0_wr_clk ,

input c3_p0_wr_en ,

input [31:0] c3_p0_wr_mask ,

input [255:0] c3_p0_wr_data ,

output wire c3_p0_wr_full ,

output wire c3_p0_wr_empty ,

output wire [10:0] c3_p0_wr_count ,

input c3_p1_cmd_clk ,

input c3_p1_cmd_en ,

input [ 6:0] c3_p1_cmd_bl ,

input [27:0] c3_p1_cmd_byte_addr ,

output wire c3_p1_cmd_empty ,

output wire c3_p1_cmd_full ,

input c3_p1_wr_clk ,

input c3_p1_wr_en ,

input [31:0] c3_p1_wr_mask ,

input [255:0] c3_p1_wr_data ,

output wire c3_p1_wr_full ,

output wire c3_p1_wr_empty ,

output wire [10:0] c3_p1_wr_count ,

input c3_p2_cmd_clk ,

input c3_p2_cmd_en ,

input [ 6:0] c3_p2_cmd_bl ,

input [27:0] c3_p2_cmd_byte_addr ,

output wire c3_p2_cmd_empty ,

output wire c3_p2_cmd_full ,

input c3_p2_rd_clk ,

input c3_p2_rd_en ,

output wire [255:0] c3_p2_rd_data ,

output wire c3_p2_rd_full ,

output wire c3_p2_rd_empty ,

output wire [10:0] c3_p2_rd_count ,

input c3_p3_cmd_clk ,

input c3_p3_cmd_en ,

input [ 6:0] c3_p3_cmd_bl ,

input [27:0] c3_p3_cmd_byte_addr ,

output wire c3_p3_cmd_empty ,

output wire c3_p3_cmd_full ,

input c3_p3_rd_clk ,

input c3_p3_rd_en ,

output wire [255:0] c3_p3_rd_data ,

output wire c3_p3_rd_full ,

output wire c3_p3_rd_empty ,

output wire [10:0] c3_p3_rd_count

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//mig_7series_0_inst

wire [27:0] app_addr ;

wire [ 2:0] app_cmd ;

wire app_en ;

wire [255:0] app_wdf_data ;

wire app_wdf_end ;

wire app_wdf_wren ;

wire [255:0] app_rd_data ;

wire app_rd_data_end ;

wire app_rd_data_valid ;

wire app_rdy ;

wire app_wdf_rdy ;

wire [31:0] app_wdf_mask ;

wire ui_clk ;

wire ui_clk_sync_rst ;

//a7_wr_ctrl_inst1

wire app_en_wr1 ;

wire [ 3:0] app_cmd_wr1 ;

wire [27:0] app_addr_wr1 ;

wire app_wdf_wren_wr1 ;

wire [255:0] app_wdf_data_wr1 ;

wire [31:0] app_wdf_mask_wr1 ;

wire app_wdf_end_wr1 ;

wire a7_wr_start_wr1 ;

wire [ 6:0] a7_wr_bl_wr1 ;

wire [27:0] a7_wr_init_addr_wr1 ;

wire [255:0] a7_wr_data_wr1 ;

wire [31:0] a7_wr_mask_wr1 ;

wire a7_wr_end_wr1 ;

wire a7_wr_req_wr1 ;

//a7_wr_ctrl_inst2

wire app_en_wr2 ;

wire [ 3:0] app_cmd_wr2 ;

wire [27:0] app_addr_wr2 ;

wire app_wdf_wren_wr2 ;

wire [255:0] app_wdf_data_wr2 ;

wire [31:0] app_wdf_mask_wr2 ;

wire app_wdf_end_wr2 ;

wire a7_wr_start_wr2 ;

wire [ 6:0] a7_wr_bl_wr2 ;

wire [27:0] a7_wr_init_addr_wr2 ;

wire [255:0] a7_wr_data_wr2 ;

wire [31:0] a7_wr_mask_wr2 ;

wire a7_wr_end_wr2 ;

wire a7_wr_req_wr2 ;

//a7_rd_ctrl_inst1

wire app_en_rd1 ;

wire [ 3:0] app_cmd_rd1 ;

wire [27:0] app_addr_rd1 ;

wire app_rd_data_valid_rd1 ;

wire a7_rd_start_rd1 ;

wire [ 6:0] a7_rd_bl_rd1 ;

wire [27:0] a7_rd_init_addr_rd1 ;

wire [255:0] a7_rd_data_rd1 ;

wire a7_rd_data_valid_rd1 ;

wire a7_rd_end_rd1 ;

//a7_rd_ctrl_inst2

wire app_en_rd2 ;

wire [ 3:0] app_cmd_rd2 ;

wire [27:0] app_addr_rd2 ;

wire app_rd_data_valid_rd2 ;

wire a7_rd_start_rd2 ;

wire [ 6:0] a7_rd_bl_rd2 ;

wire [27:0] a7_rd_init_addr_rd2 ;

wire [255:0] a7_rd_data_rd2 ;

wire a7_rd_data_valid_rd2 ;

wire a7_rd_end_rd2 ;

//arbit_inst

//wire c3_p0_cmd_empty ;

//wire c3_p1_cmd_empty ;

//wire c3_p2_cmd_empty ;

//wire c3_p3_cmd_empty ;

//rst delay

reg [ 5:0] rst_cnt ;

//========================================================================================\

//************** Main

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4872

4872