flash M25P128读操作

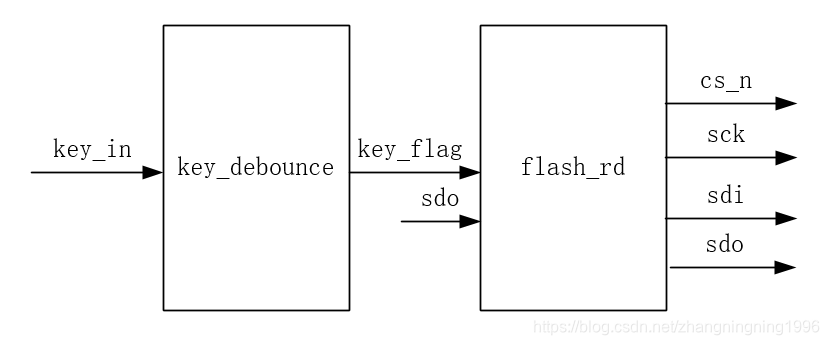

我们本次实验的内容是,对flash读一个字节的数据,系统框图如下:

所用到的软硬件环境为:

所用到的软硬件环境为:

硬件:锆石A4plus开发板

软件:quartus II 13.1

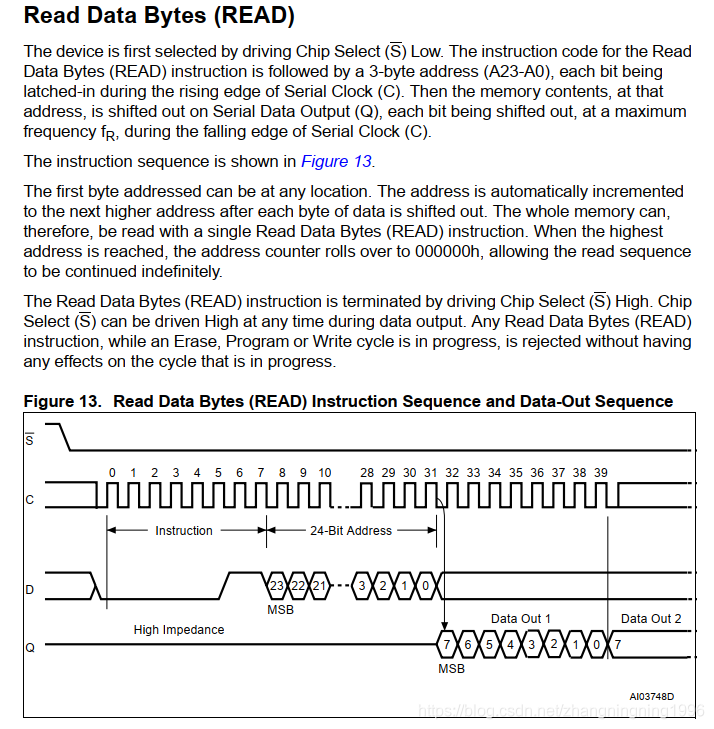

从技术手册中我们可以得到如下信息:

从上述信息中我们可以得到:

1、一个读指令操作可以读取整个flash的数据。

2、所利用的时序仍为SPI时序

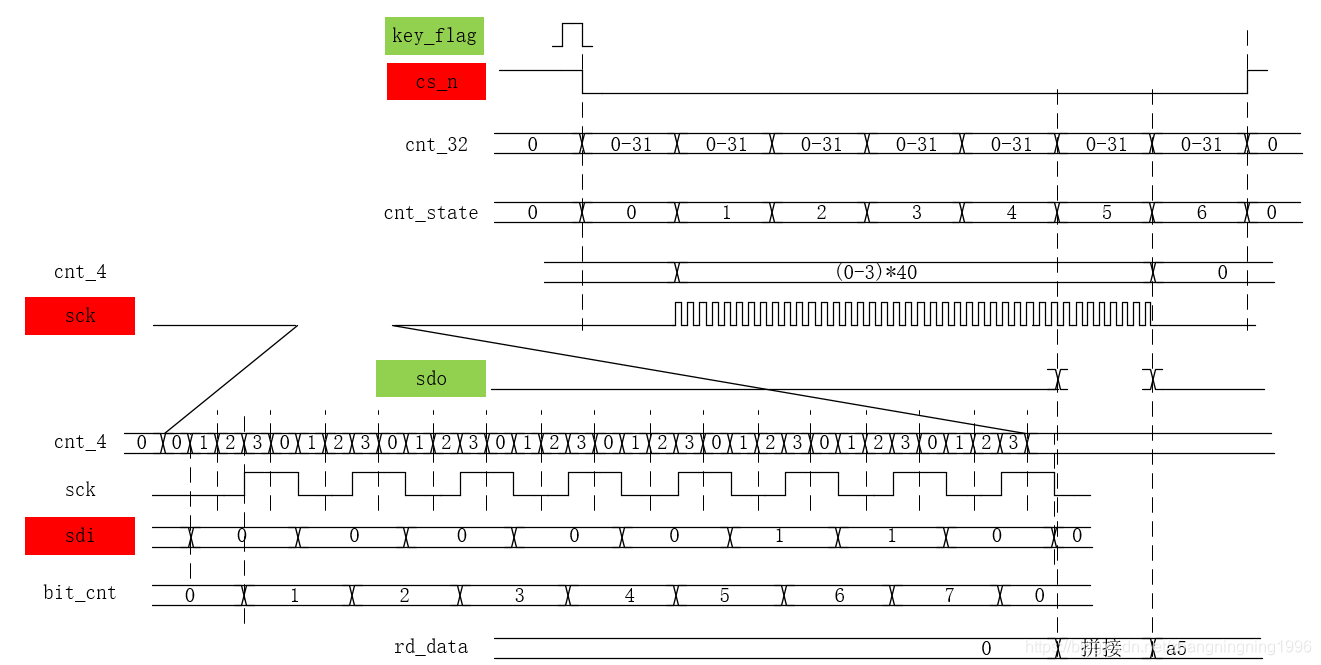

时序图设计

同样我们也对flash的擦除时序进行一定程度的更改如下:

这里的时序图画的稍微乱点,但相信同学们有了前面的基础肯定可以学会。接下来便直接上代码。

flash_read模块的书写

这里的传统不说废话,直接上代码:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : flash_read.v

// Create Time : 2020-01-09 12:52:26

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module flash_read(

input sclk ,

input rst_n ,

input key_flag ,

output reg cs_n ,

output reg sck ,

output reg sdi ,

input sdo ,

output reg [ 7:0] data_out ,

output reg data_flag

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

parameter READ_INST = 8'h03 ;

parameter READ_ADDR = 24'h00_03_21 ;

reg [ 4:0] cnt_32 ;

reg [ 2:0] cnt_state ;

reg [ 1:0] cnt_4 ;

reg [ 4:0] bit_cnt ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

cs_n <= 1'b1;

else if(key_flag == 1'b1)

cs_n <= 1'b0;

else if(cnt_32 == 'd31 && cnt_state == 'd6)

cs_n <= 1'b1;

else

cs_n <= cs_n;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

cnt_32 <= 5'd0;

else if(cnt_32 == 'd31)

cnt_32 <= 5'd0;

else if(cs_n == 1'b0)

cnt_32 <= cnt_32 + 1'b1;

else

cnt_32 <= 5'd0;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

cnt_state <= 3'd0;

else if(cnt_state == 'd6 && cnt_32 == 'd31)

cnt_state <= 3'd0;

else if(cnt_32 == 'd31)

cnt_state <= cnt_state + 1'b1;

else

cnt_state

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1715

1715