笔者之前从事硬件研发工作,曾经对高速信号的信号完整性工作做过一些研究,但是始终没有找到门径,现在在美国一家公司从事芯片的电源完整和信号完整性性能测试方面的工作,开始对电源完整性和信号完整性有了一定的认识,从现在开始我将会和大家分享一些对信号完整性和电源完整性方面的心得,有一部分内容可能不是原创,是我之前的学习笔记,我在这里分享出来,主要是想梳理清楚思路,如果有侵犯到您的版权,请与我联系,我会及时删改,谢谢!

同时我之前使用的是latex写的学习笔记,因为知乎不支持语法编辑,我无法实现一些诸如上标和下标等格式,所以保留了latex里的格式标记。

另外我的文章也会在SI-list【中国】微信公众号上同步更新,大家也可以通过关注SI-list【中国】微信公众号关注我的更新。谢谢!

======================================================================

前面几篇文章大概介绍了一下电源分布网络,这一节我想通过对PDN网络模型的分析来让大家了解一下PDN网络的一些特点。

最简化模型分析

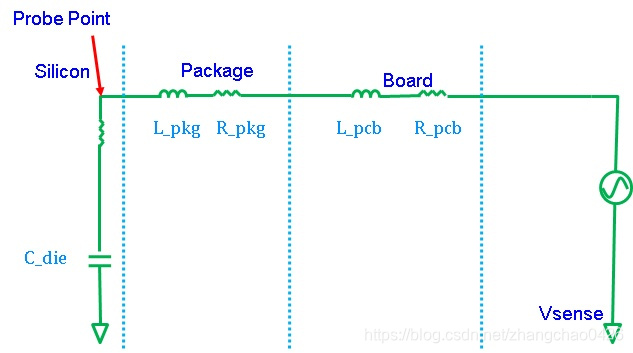

最初的芯片功能相对来说比较简单,运行的频率也比较低,所以也很少出现电源完整性问题。当时的工程师也很少考虑电源完整性相关的设计。我们可以使用下图所示的PDN网络模型来分析早期比较简单的芯片。

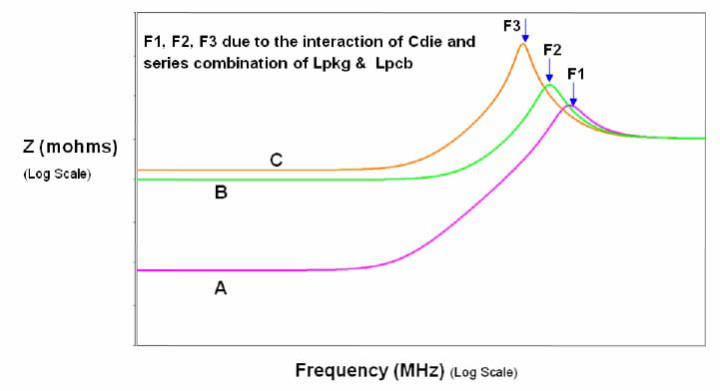

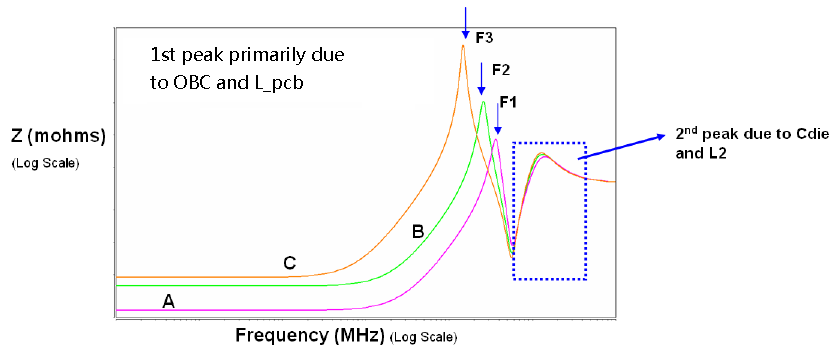

可以看到早期的芯片,并没有在封装上设计去耦电容。在这个模型中,die包含寄生电阻R_{die}和寄生电容C_{die},封装包含了寄生电感L_{pkg}。同时PCB上也没有设计去耦电容以及电源平面。这是一个典型的平行谐振电路,并行谐振电路存在并行谐振点。下图显示了从上图的测试点看到的阻抗曲线。

通过如下公式我们可以计算谐振频率。

上图同时显示了谐振频率与电感的关系。图中曲线A是在R_{pcb}和L_{pcb}都为0时的阻抗曲线,此时的并行谐振频率为F1.这个例子展示的是完全理想的PCB,没有任何的寄生参数。

图中曲线B是表征了在比较低的PCB寄生参数情况下的阻抗曲线,此时的并行谐振频率为F2.此时PCB有比较低的寄生电感和寄生电阻。从图中可以看出,阻抗的峰值向左(低频)移动,同时峰值的幅度也有所增大。增加的PCB寄生电阻使得整个阻抗曲线都向上移动。

图中曲线C表征的是高PCB寄生参数时的阻抗曲线,此时PCB有比较高的寄生电感和寄生电阻。此时的阻抗峰值向更加低频方向移动,而且峰值幅度进一步提高。整个曲线的阻抗也得到了提高。

添加PCB上电容模型分析

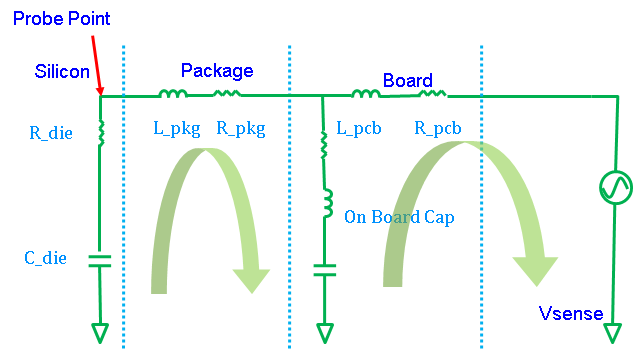

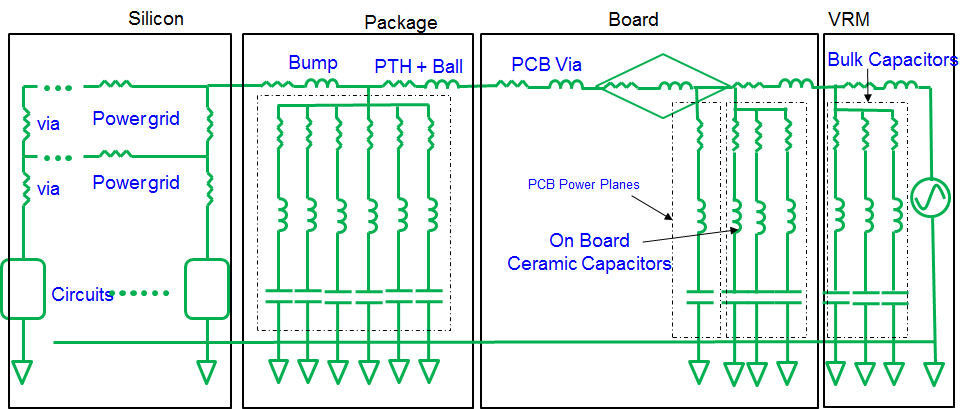

随着芯片功能越来越复杂,需要消耗越来越多的电流,同时芯片的运行频率也不断的提高,在一些系统中,工程师开始在PCB上添加去耦电容。当PDN网络中添加PCB上去耦电容以后,PDN网络的模型变为如下图所示。

下图显示了从上图测试点看到的阻抗曲线。靠右边的第二个阻抗峰值是由die上的电容和从die到PCB的串联寄生电感相互作用产生的。第一个阻抗封装是由PCB上的去耦电容和PCB传播电感之间作用形成的。

上图显示了如下三种情况下的仿真结果:

- 理想PCB情况下的阻抗曲线

- 低寄生参数下的阻抗曲线

- 高寄生参数下的阻抗曲线

这种情况就是我们现在大量采用的wire bond封装芯片的电源分布网络简化拓扑图。通过上面的分析我们可以得到以下几点结论:

1.由片上电容与die到PCB这段电感组成了第一个LOOP,这个loop的有一个特征谐振频率。而这个谐振频率主要受到片上电容以及die到PCB的寄生电感的影响。PCB上的去耦电容数量,大小等对这个谐振频率影响很小。但是PCB上的去耦电容的位置会影响到该谐振频率,我们需要尽量将去耦电容放置到靠近芯片的电源管脚的位置,这样可以减小die与PCB上去耦电容之间的寄生电感。

2. PCB板上电容与PCB上寄生电感形成第二个LOOP,这个LOOP的谐振频率受到芯片电源管脚附近的去耦电容容值,以及去耦电容与VRM之间传输通道的寄生电感影响。

2.谐振频率点的左侧主要表现为容性特性,右侧主要变现为感性特性。也就是说如果增加去耦电容,谐振频率会变高。如果寄生电感变大,则谐振频率会变低。

添加封装上电容模型分析

随着芯片瞬态电流的不断增大,我们需要进一步降低PDN网络的阻抗。但是根据前面的分析,die与PCB之间的电感无法做到足够低响很小,这时很多公司在封装上添加去耦电容,将第一个比较大的LOOP分割成2个较小的LOOP。这样使得第一个LOOP减小,LOOP1的寄生电感大幅减小,这样会使得第一个谐振频率向高频移动,同时会降低谐振频率附近的阻抗。

当我们讲PCB上电容以及VRM都考虑进去,就会得到一个完整的PDN模型,如下图所示。

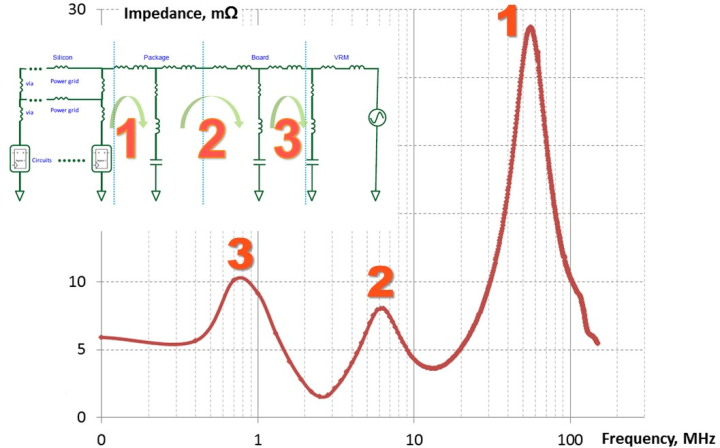

下图为我们测得的某个系统的阻抗曲线,阻抗曲线有三个明显的峰值。最主要一个是1\#峰值,大概在50MHz附近,是由片上电容和封装电感的谐振产生的。2\#峰值在10MH在以下,是由于封装电容与PCB的电感谐振产生的。最后一个3\#峰值通常都是在1MHz一下的范围,是由PCB板上小的去耦电容,小的去耦电容与电压转换器之间连线的寄生电感的谐振产生的。

实例分析

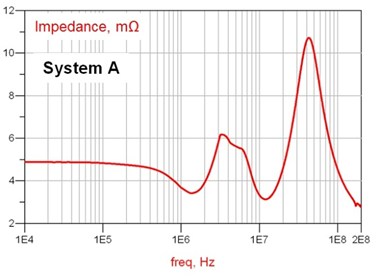

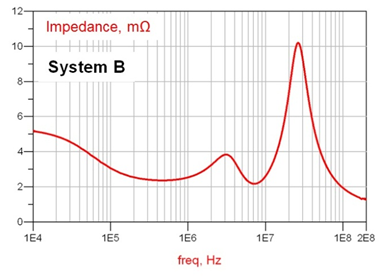

前面进行了理论的分析,现在我们将几个实例拿来进一步验证一下我们之前的分析,大家可以参考分析文献,里面提到了3个系统,3个系统的阻抗曲线分别如下:

系统A和系统B采用相同的芯片设计架构以及相同的生产工艺,均采用Flip chip封装,所以单位芯片面试的电容容值是相同的,但是系统B的die的面积更大,这样系统B的on die电容容值更大,是的系统B的一次谐振频率低,为26MHz,而系统A的一次谐振频率为38MHz。

系统C是wire bond封装,封装上没有去耦电容,所以系统C就少一个loop,通常表现为一个peak或者2个谐振频率。另外由于die与PCB去耦电容之间的寄生电感比较大,使得一次谐振频率变得更低。

总结:

1. 对于flip chip,PCB板级设计几乎不会影响到一次谐振频率与幅度

2. 对于wire bond芯片,将去耦电容尽量靠近芯片电源管脚,可以减少die与PCB去耦电容之间的寄生电感,有效的降低系统的阻抗以及提高系统的谐振频率。

3. 通常情况下芯片的一次谐振频率处的阻抗最高。

参考文献:

1. “Distributed Modeling and Characterization of On-Chip/System Level PDN and Jitter Impact”

37

37

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?