计算机组成原理与体系结构(分值比例6/75)

一、数据的表示

1.进制转换

①R进制转十进制

使用按权展开法,其具体操作方式为:将R进制数的每一位数值用Rk形式表示,即幂的底数是R,指数为k,k与该位和小数点之间的距离有关。当该位位于小数点左边,k值是该位和小数点之间数码的个数,而当该位位于小数点右边,k值是负值,其绝对值是该位和小数点之间数码的个数加1。

②十进制转R进制

使用短除法

③二进制转八进制与十六进制数。

二进制转八进制:从右往左依次分段,每段三个数字,高位不足三个时在高位补零。将每段转为八进制依次书写。

二进制转十六进制:从右往左依次分段,每段四个数字,高位不足四个时在高位补零。将每段转为十六进制依次书写。

十六进制,八进制转二进制则反之。

2.数据表示中的编码问题

①数据的表示

在原码反码补码中首位代表正负,补码中可以相加。

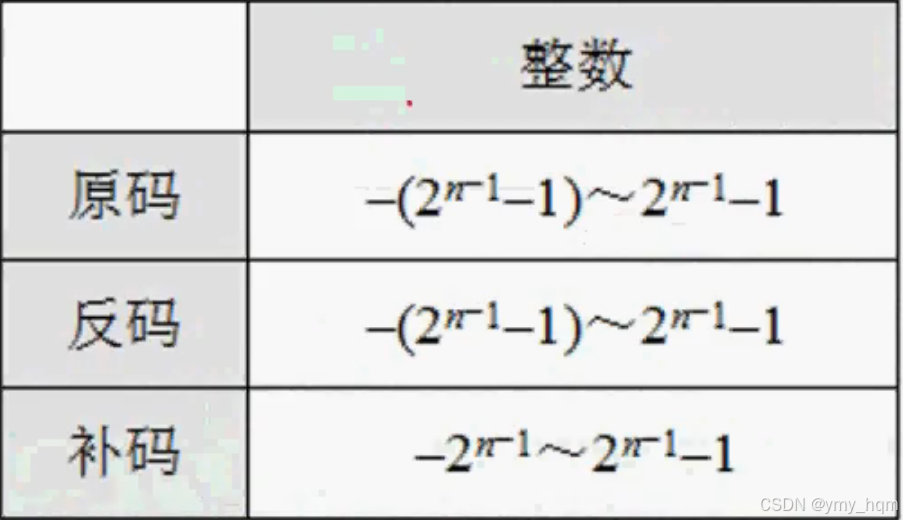

②数值表示范围

3.浮点数运算

浮点数表示:

N = M*Re

其中M称为尾数,e是指数,R为基数。

对阶→尾数计算→结果格式化

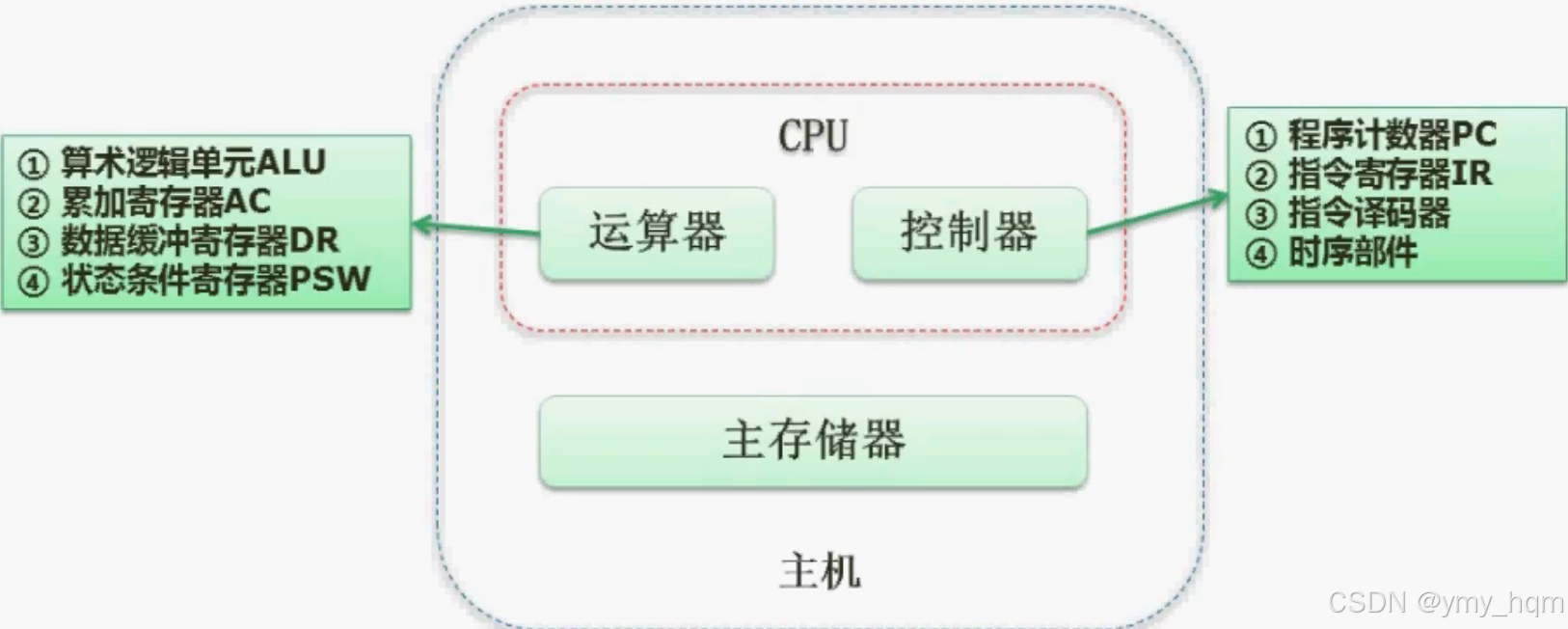

二、计算机结构

三、Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块::一个 | 单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块::多个 | 各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块::多个 | 被证明不可能,至少是不实际 | 目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块::多个 | 能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

四、CISC与RISC

| 指令系统类型 | 指令 | 寻址方式 | 实现方式 | 其它 |

| CISC(复杂) | 数量多,使用频率差别大,可变长格式 | 支持多种 | 微程序控制技术(微码) | 研制周期长 |

| RISC(精简) | 数量少,使用频率接近,定长格式,大部分为单周期指令,操作寄存器,只有Load/Store操作内存 | 支持方式少 | 增加了通用寄存器:硬布线逻辑控制为主:适合采用流水线 | 优化编译,有效支持高级语言 |

五、流水线技术

1.概念

流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度

步骤:取指→分析→执行

2.流水线计算

流水线周期为执行时间最长的一段

流水线计算公式为:

1条指令执行时间 +(指令条数-1)*流水线周期

①理论公式:(t1+t2+..+tk)+(n-1)*Δt

②实践公式 :(k+n-1)*Δt

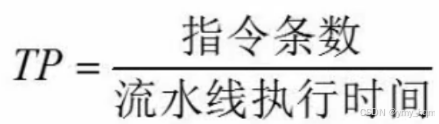

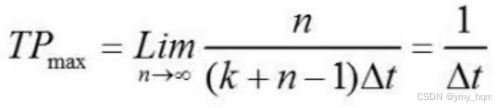

3.流水线吞吐率计算

流水线的吞吐率(ThoughPutrate,TP)是指在单位时间内流水线所完成的任务数量或输出的结果数量。计算流水线吞吐率的最基本的公式如下:

流水线最大吞吐率:

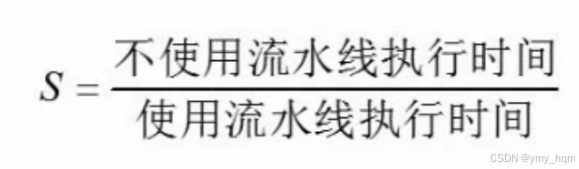

4.流水线的加速比

完成同样一批任务,不使用流水线所用的时间与使用流水线所用的时间之比称为流水线的加速比。计算流水线加速比的基本公式如下:

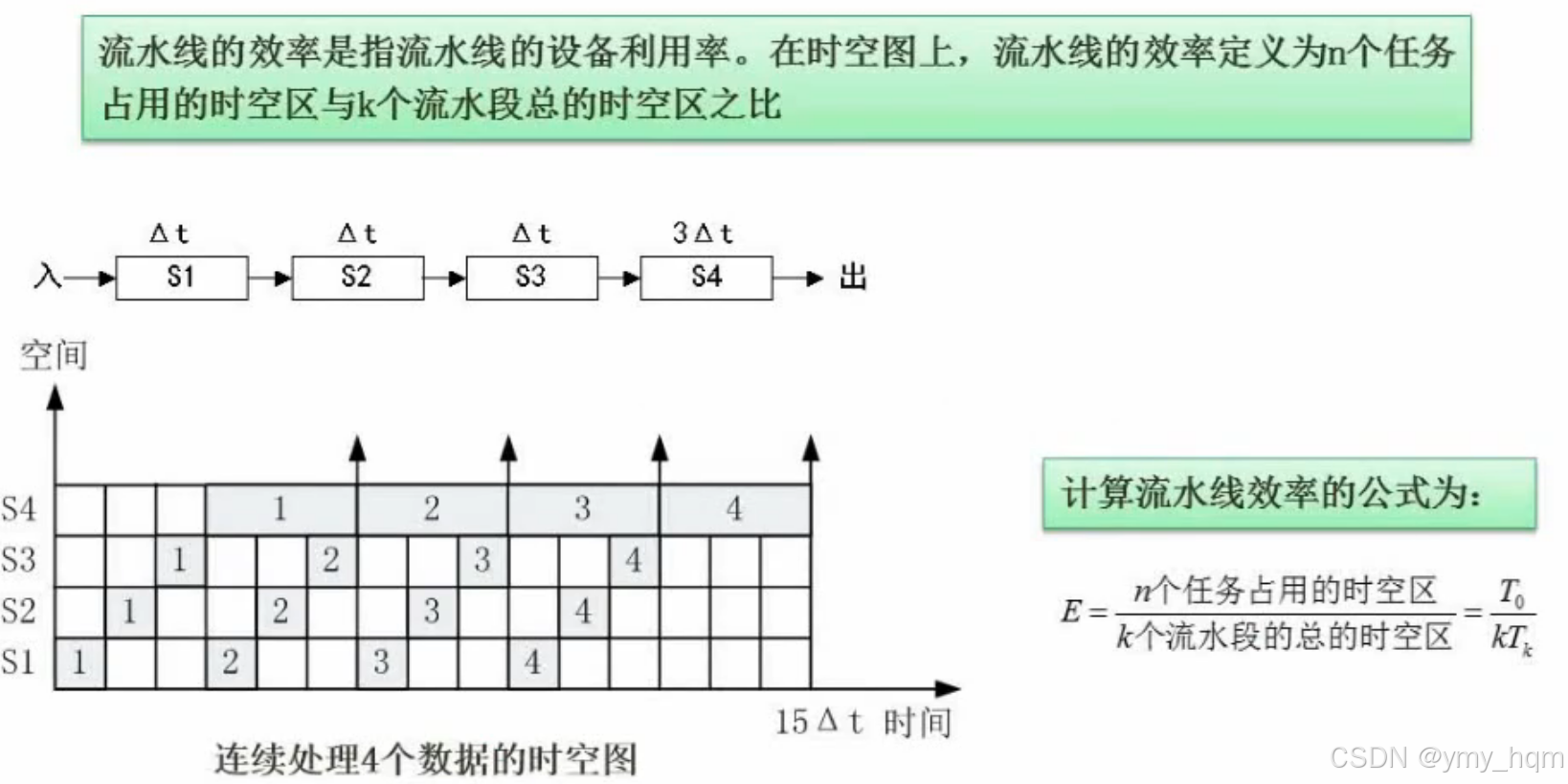

5.流水线的效率

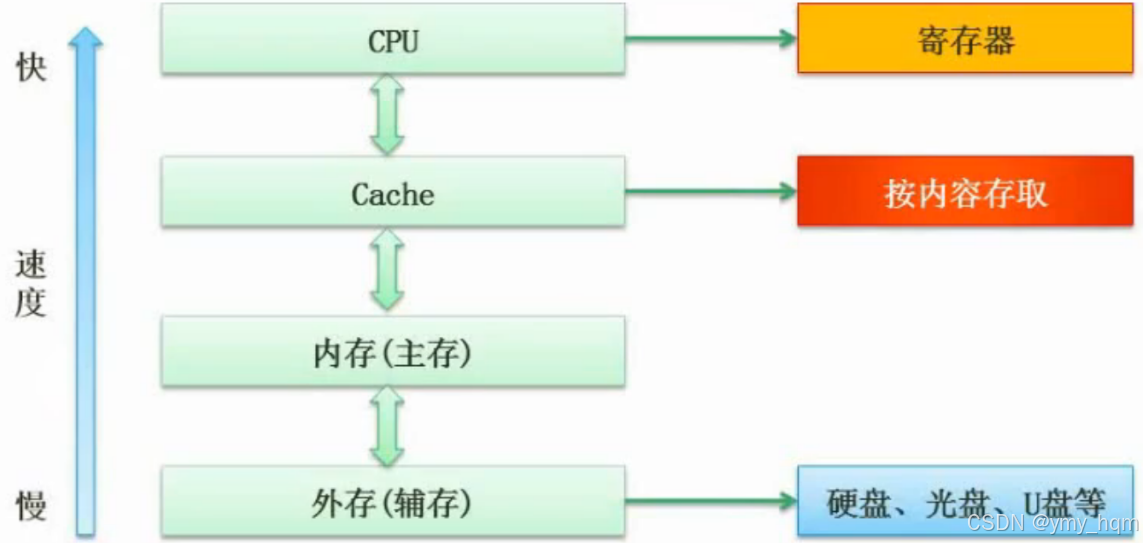

六、存储系统

1.层次化存储结构

2.Cache-概念

Cache的功能:提高CPU数据输入输出的速率,突破冯·诺依曼瓶颈,即CPU与存储系统间数据传送带宽限制。

在计算机的存储系统体系中,Cache是访问速度最快的层次。

使用Cache改善系统性能的依据是程序的局部性原理。

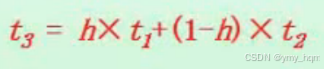

如果以h代表对Cache的访问命中率,t1表示Cache的周期时间,t2表示主存储器周期时间,以读操作为例,使用“Cache+主存储器”的系统的平均周期为t3,则:

其中,(1-h)又称为失效率(未命中率)。

3.局部性原理

时间局部性

空间局部性

工作集理论:工作集是进程运行时被频繁访问的页面集合

例:

int i, s=0;

for(i=1;i<1000;i++)

for(j=1;j<1000;j++)

s+=j;

printf("结果为:%d",s)初始化语句int i, s=0;只需执行一次。中间循环体则需频繁执行。中间循环体不需要从内存调取数据而是从Cache调取数据这就是时间局部性

4.主存-分类

| 随机存取存储器 | DRAM(DynamiCRAM,动态RAM)-SDRAM SRAM(Static RAM,静态) |

| 只读存储器 | MROM(MaskROM,掩模式ROM) PROM(Programmable ROM,一次可编程 ROM)EPROM(Erasable PROM,可擦除的PROM) 闪速存储器(flash memory,闪存) |

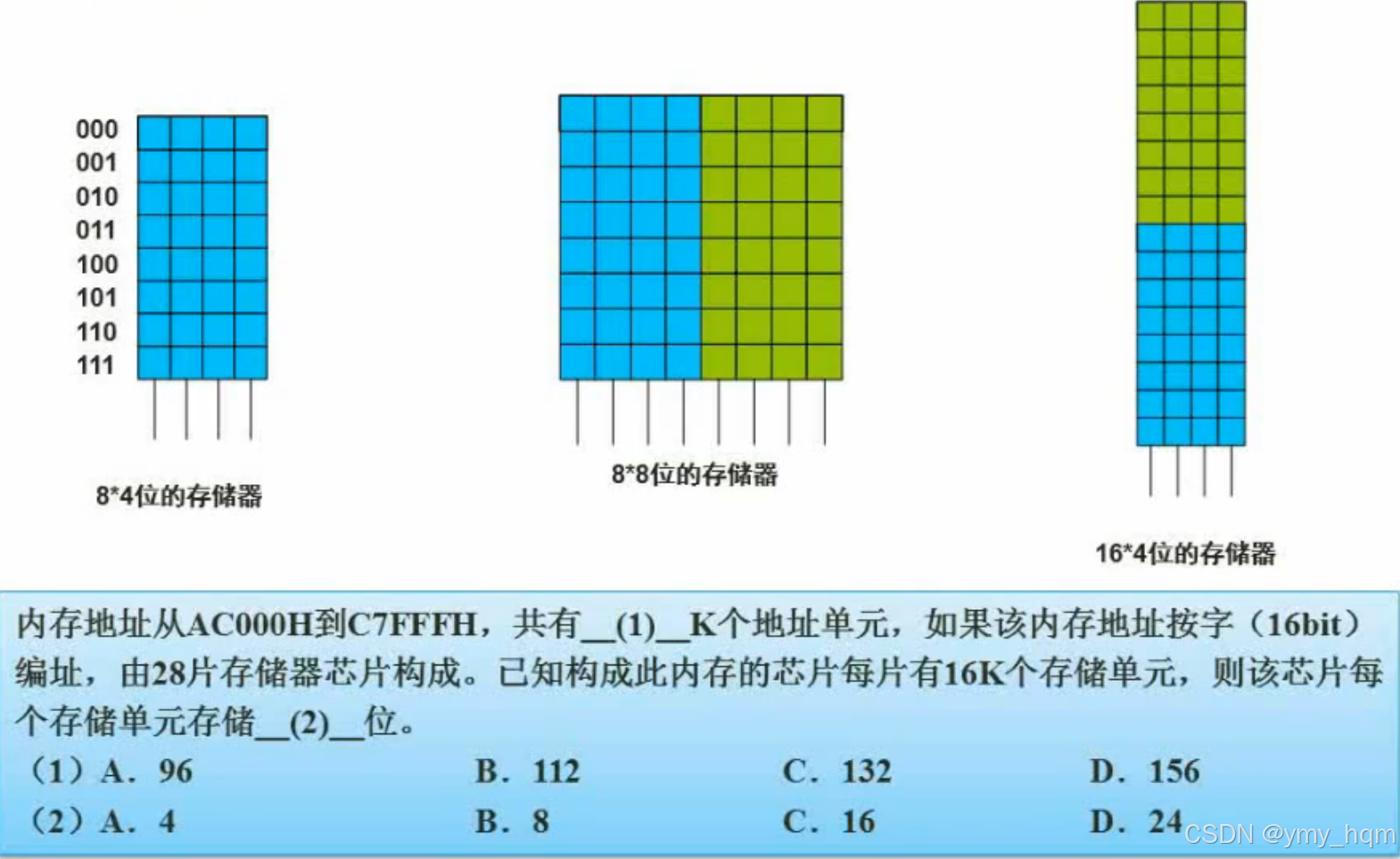

5.主存-编址

6.磁盘结构与参数

七、总线系统

1.总线

根据总线所处的位置不同,总线通常被分成三种类型,分别是:

内部总线

系统总线分为:数据总线、地址总线、控制总线

外部总线

八、可靠性

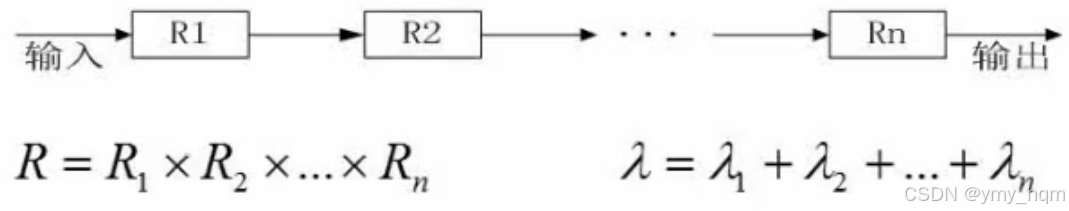

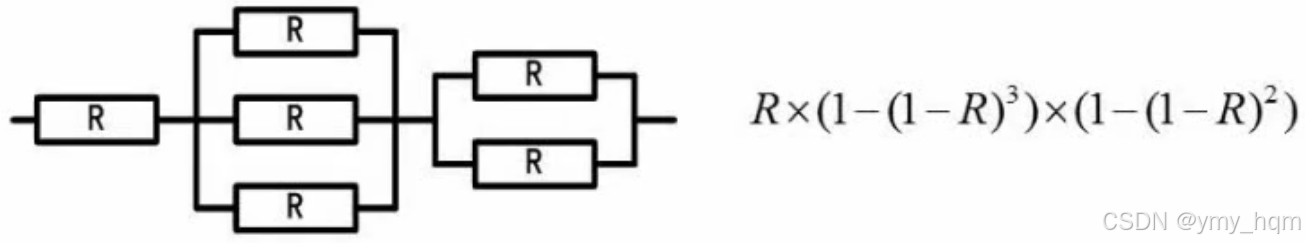

1.系统可靠性分析-串联系统与并联系统

串联模型:

R:可靠度 λ:失效率(近似公式)

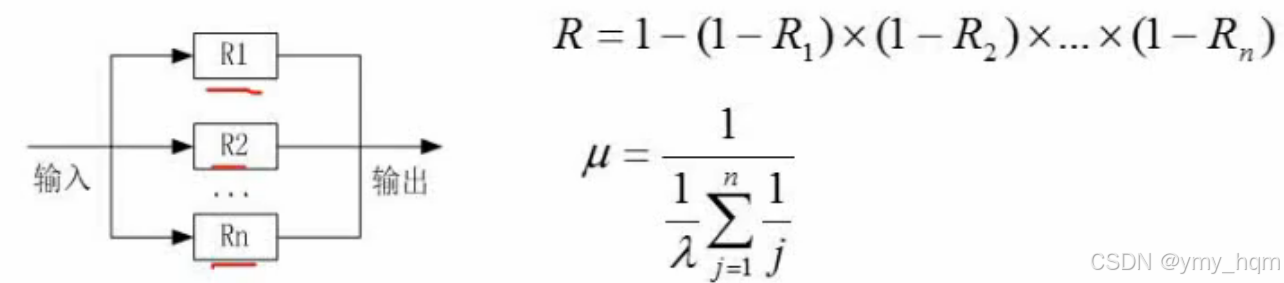

并联模型:

用1-可靠的即为失效率。

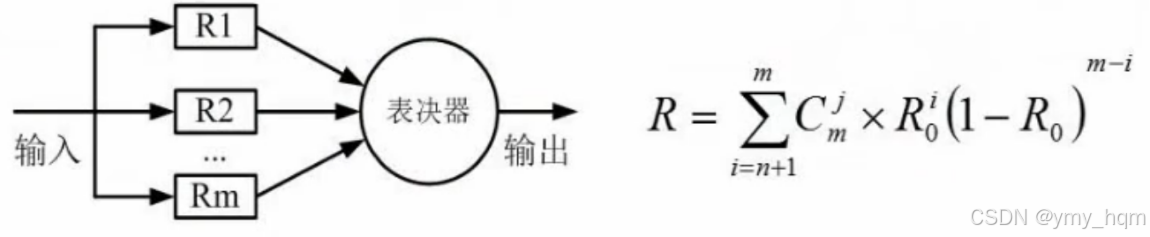

2.系统可靠性分析-模几余系统与混合系统

九、校验码

1.概念

什么是检错和纠错?

检错即检查出错误,纠错为检查出错误并纠正错误

什么是码距?

一个编码系统的码距是整个编码系统中任意(所有)两个码字的最小距离例:

若用1位长度的二进制编码。若A=1,B-0。这样A,B之间的最小码距为1。

若用2位长度的二进制编码,若以A=11,B-00为例,A、B之间的最小码距为2.(可以检错)

若用3位长度的二进制编码,可选用111,000作为合法编码。A,B之间的最小码距为3。(可以纠错)

码距与检错、纠错有何关系?

1.在一个码组内为了检测e个误码,要求最小码距d应该满足:d>=e+1

2.在一个码组内为了纠正t个误码,要求最小码距d应该满足:d>=2t+1

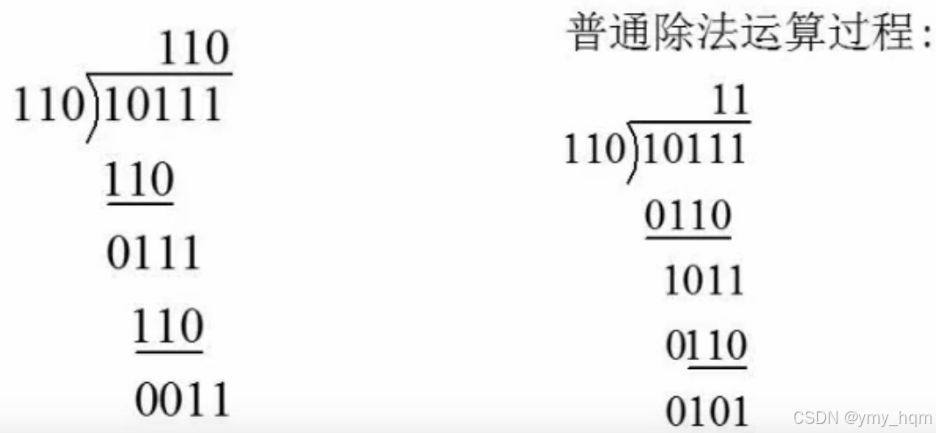

2.循环校验码CRC

什么是模2除法,它和普通的除法有何区别?

模2除法是指在做除法运算的过程中不计其进位的除法。

例如,10111对110进行模2除法为:

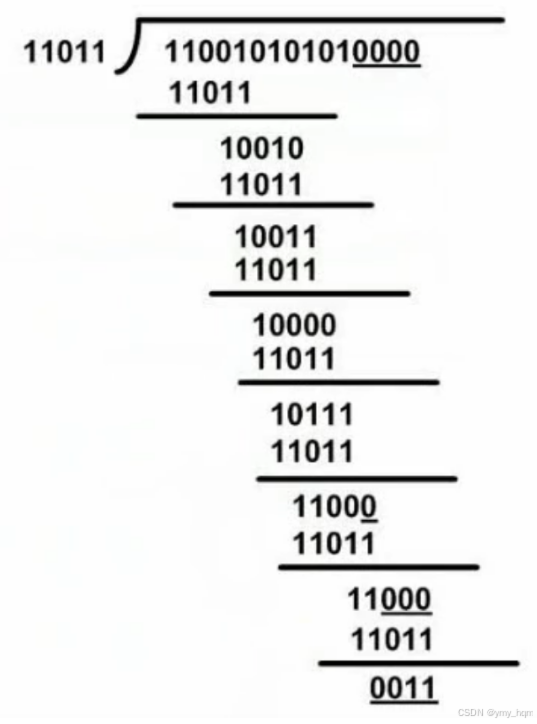

例:原始报文为“11001010101”,其生成多项式为:“x4+x3+x+1”。对其进行CRC编码后的结果为?

注:在被除数上末尾补出除数位数减一数的0,以为了除出余数。

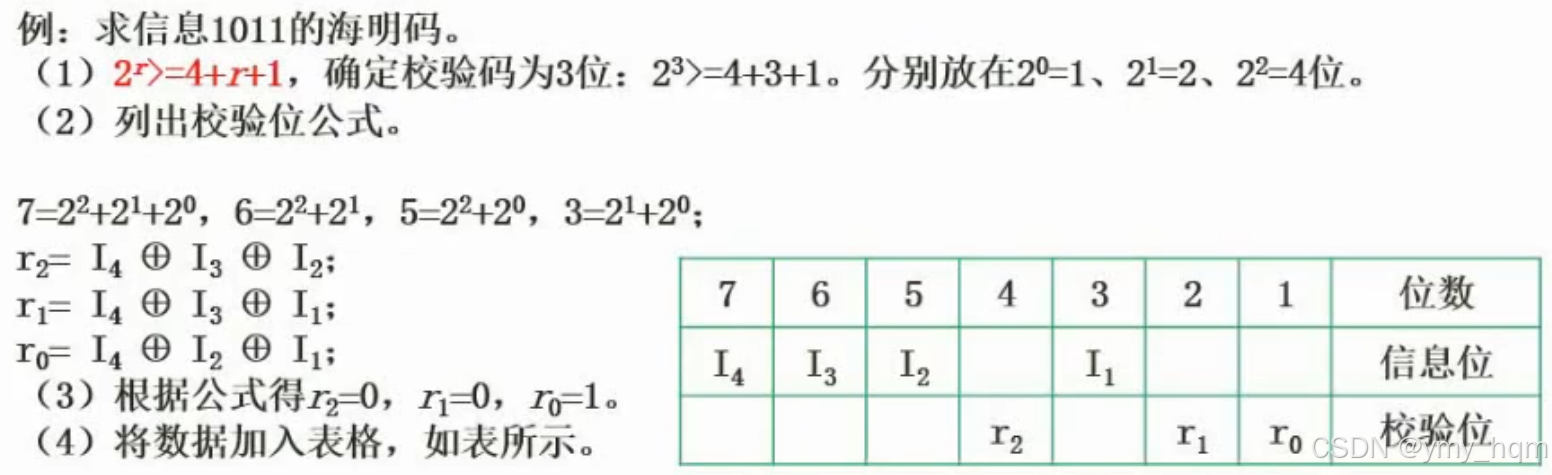

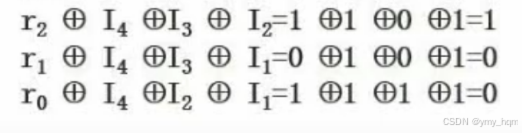

3.海明校验码

若收到的信息为:1011101则:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 位数 |

| 1 | 0 | 1 | 1 | 信息位 | |||

| 0 | 0 | 1 | 校验位 |

软考软件设计师计算机组成原理笔记

软考软件设计师计算机组成原理笔记

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?