本文为CAD芯智库整理,未经允许请勿复制、转载!

原文转自: www.xwzsoft.com/h-nd-636.html

上一篇阿芯为大家整理国产中望CAD机械2026的六大全新优化模块,而工程建设行业作为使用CAD软件核心应用行业之一,中望CAD也有配套的专用建筑版版。

对此,阿芯专门整理了中望CAD建筑2026版中对企业提效影响最大的的七大新优势,让工程师能更有针对性的体验新功能!

30秒速懂中望CAD建筑版

面向工程建筑行业的专业设计软件,集成14个专业模块、近300个功能命令,涵盖建筑行业主流设计需求。支持从概念方案到施工图设计全流程设计协同,适用于规划、建筑、景观、室内及地产开发等专业领域。

快速指引

中望 CAD 2026 企业选型优惠·试用

400··806··2030

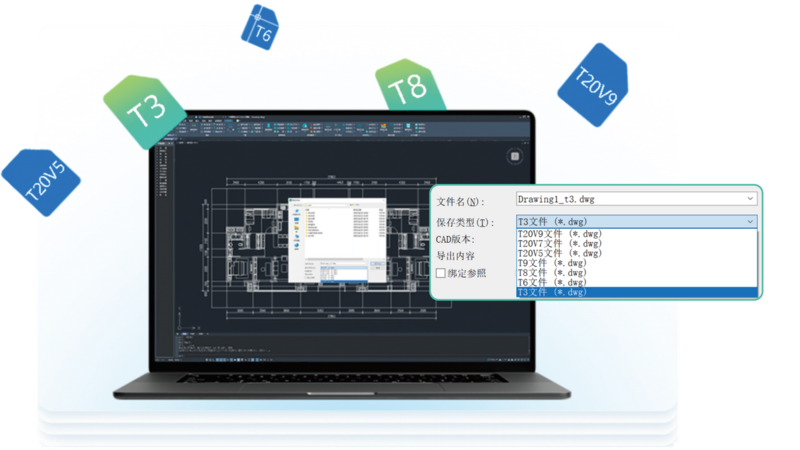

一、全面兼容主流建筑软件

中望建筑CAD全面兼容主流建筑软件及历史版本图纸,支持全专业T30V1.0及以下版本格式文件的打开、查看与轻量编辑,提供T3/T6/T8/T9/T20V5.0/T20V7.0/T20V9.0等多种通用版本格式导出功能,确保设计成果在不同平台间高效复用与无损流转。

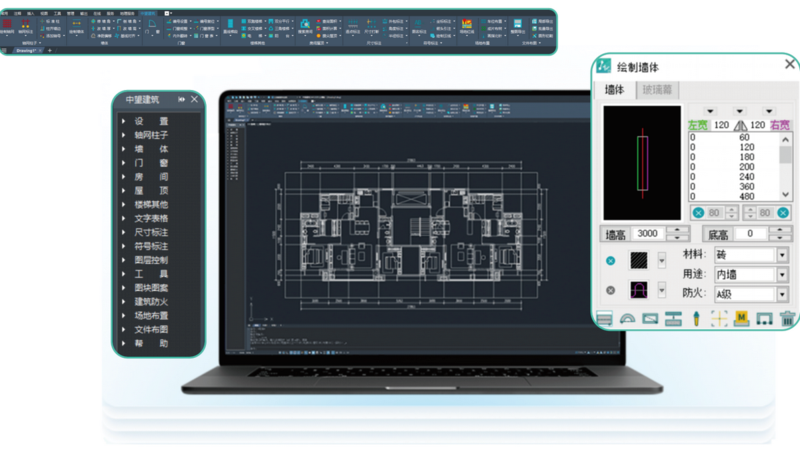

二、基础绘图功能全面更新

完整支持建筑专业设计工作流:轴网柱子-墙体-门窗-房间-屋顶-楼梯等。通过对话框设定参数可快速生成建筑构件,满足标准与非标准建筑构件的设计需求。

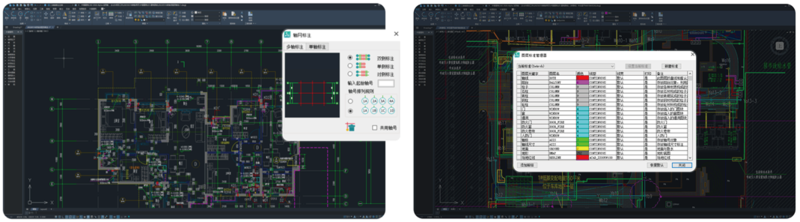

三、丰富智能的标注系统及图层管理器

新版本提供便捷和智能联动的建筑尺寸标注及符号标注;优化【图层管理器】命令,提供更多适配建筑绘图的图层管理功能。

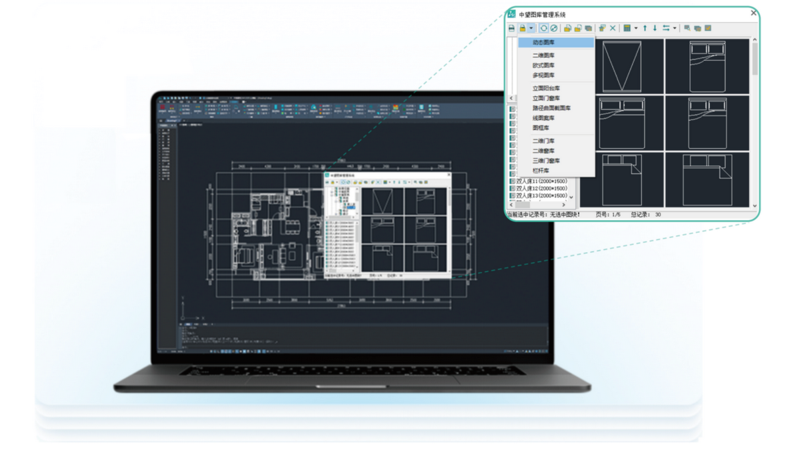

四、图库系统全新升级

提供5000+标准化建筑图块,支持拖拽排序、批量改名及新图入库管理等,帮助用户快速调用设计素材,显著提升设计效率。

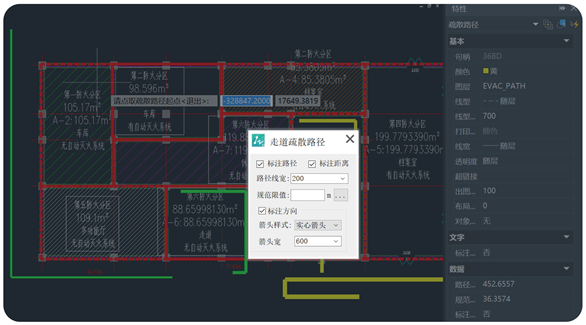

五、新增建筑防火模块

中望建筑CAD 2026提供部分建筑防火设计相关功能,同步更新国家现行规范要求,支持在绘图命令中直接查看防火规范内容,避免设计过程中频繁查阅资料,有效提升设计质量与工作效率。

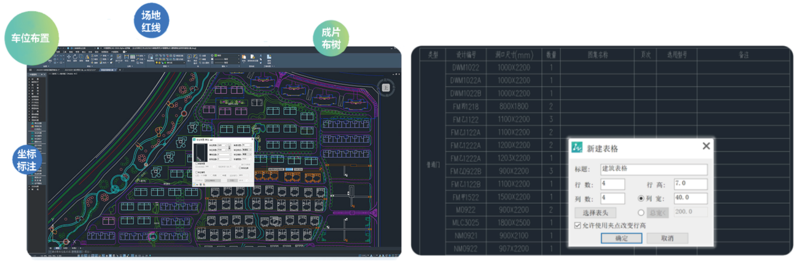

六、优化文字表格及总图布置相关功能

参照办公类软件的编辑方式,优化了单元格、表行、表列的操作逻辑,使表格编辑更高效。

通过增加场地红线生成方法、拓展车位布置模式、新增车位编号及统计功能,并强化景观绿化布置能力,全面提升总平面图设计效率。

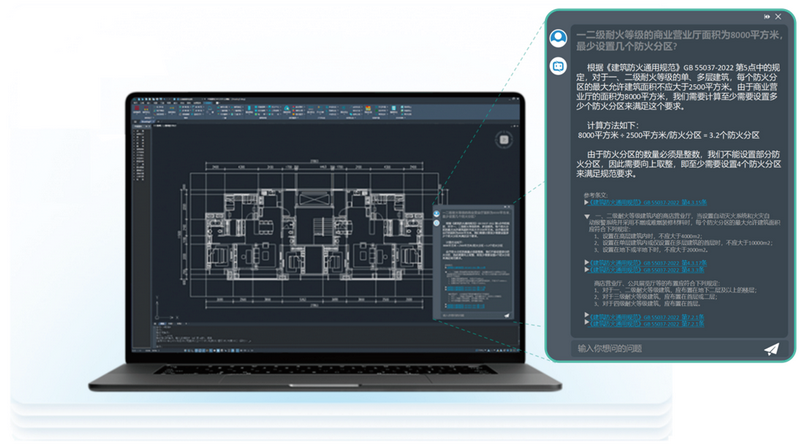

七、专业规范智能查询助手

基于AI技术提供专业规范智能查询功能,涵盖40+规范6000+条文并持续更新,帮助用户快速获取建筑规范内容、相关问题的解答,并且支持本地化部署,保证用户数据安全,全面提升设计效率与成果质量。

我们也为您解答:

中望CAD建筑版企业选型方案 | 400·806·2030 | xwzsoft.com

1. 中望CAD建筑版跟中望CAD专业版有何区别?

2. 中望CAD建筑版的AI智能技术能查询多少行业数据库数据?

3.中望CAD建筑Linux版视频哪些国产信创系统、硬件设备?

CAD芯智库是芯维智旗下企业高效CAD/3D选型技巧、规避CAD版权风险知识库。

668

668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?