uart发送器:uart发送器-并转串

uart接受器:uart接受器-串转并

联合仿真uart协议:

发送器和接收器为异步时钟

`timescale 1ns/1ns

module tb_uart #(parameter WORD_SIZE=8)();

wire clk_50M,clk_400M;

reg rst_n;

reg byte_ready;

reg t_ready;

reg [WORD_SIZE-1:0] data_in;

wire error1,error2,read_ready_out;

wire [WORD_SIZE-1:0] data_ou;

reg clk_25M;

reg clk_25M2;

initial begin

rst_n=0;

#200 rst_n=1;

end

initial begin

byte_ready=0;t_ready=0;data_in=0;

#220 gen_test_data();

end

//clk_25M与clk_25M2异步

initial begin

clk_25M=0;

forever #20 clk_25M=~clk_25M;

end

initial begin

clk_25M2=1;

forever #20 clk_25M2=~clk_25M2;

end

clk_50M clk_50M_inst (

.inclk0 (clk_25M ),

.c0 ( clk_50M )

);

clk_400M clk_400M_inst (

.inclk0 ( clk_25M2 ),

.c0 ( clk_400M )

);

uart_xmt uart_xmt_inst(

.sclk (clk_50M ),

.rst_n (rst_n ),

.byte_ready (byte_ready ),

.t_ready (t_ready ),

.data_in (data_in ),

.serial_out (serial_out )

);

uart_rec uart_rec_inst(

. sclk (clk_400M ),

. rst_n (rst_n ),

. read_not_ready_in (1'b0 ),

. serial_in (serial_out ),

. error1 (error1 ),

. error2 (error2 ),

. read_ready_out (read_ready_out ),

. valid (valid ),

. data_ou (data_ou )

);

task gen_test_data();

integer i;

for(i=0;i<10;i=i+1)begin

data_in=8'ha7+i;

#10 byte_ready=1;

#20 byte_ready=0;

#30 t_ready=1;

#20 t_ready=0;

#350;

end

endtask

endmodule

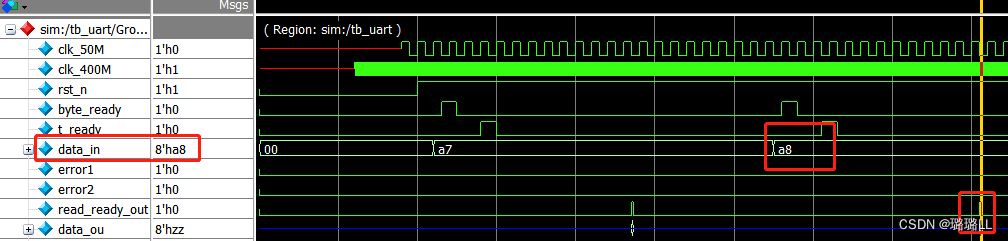

仿真结果

从仿真结果来看,两个时钟域完全异步

本文详细介绍了如何在两个异步时钟域中联合仿真UART协议,探讨了发送器和接收器的串并转换操作,并展示了实际的时钟同步问题。通过示例代码展示了如何配置和测试UART发送器和接受器,以及在仿真中观察到的异步时钟影响。

本文详细介绍了如何在两个异步时钟域中联合仿真UART协议,探讨了发送器和接收器的串并转换操作,并展示了实际的时钟同步问题。通过示例代码展示了如何配置和测试UART发送器和接受器,以及在仿真中观察到的异步时钟影响。

633

633

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?