cache 基本原理

1.cache 的功能

cache 是一种高速缓冲存储器, 是为了解决CPU 和主存之间速度不匹配而采用的一项重要技术,其原理基于程序运行中具有的空间局部性和时间局部性特征。

cache 是介于CPU 和主存M之间的小容量存储器,但存取速度比主存容量远小于主存。 cache 能高速地向CPU 提供指令和数据,从而加快了程序的执行速度。从功能上看,它是主存的缓冲存储器,由高速的SRAM组成。为追求高速 包括管理在内的全部功能由硬件实现,因而对程序员是透明的。当前,随着半导体器件集成度的进一步提高, 可以将小容量的cache与CPU集成到同一芯片中,其工作速度接近于CPU的速度 从而组成两级以上的cache 系统。

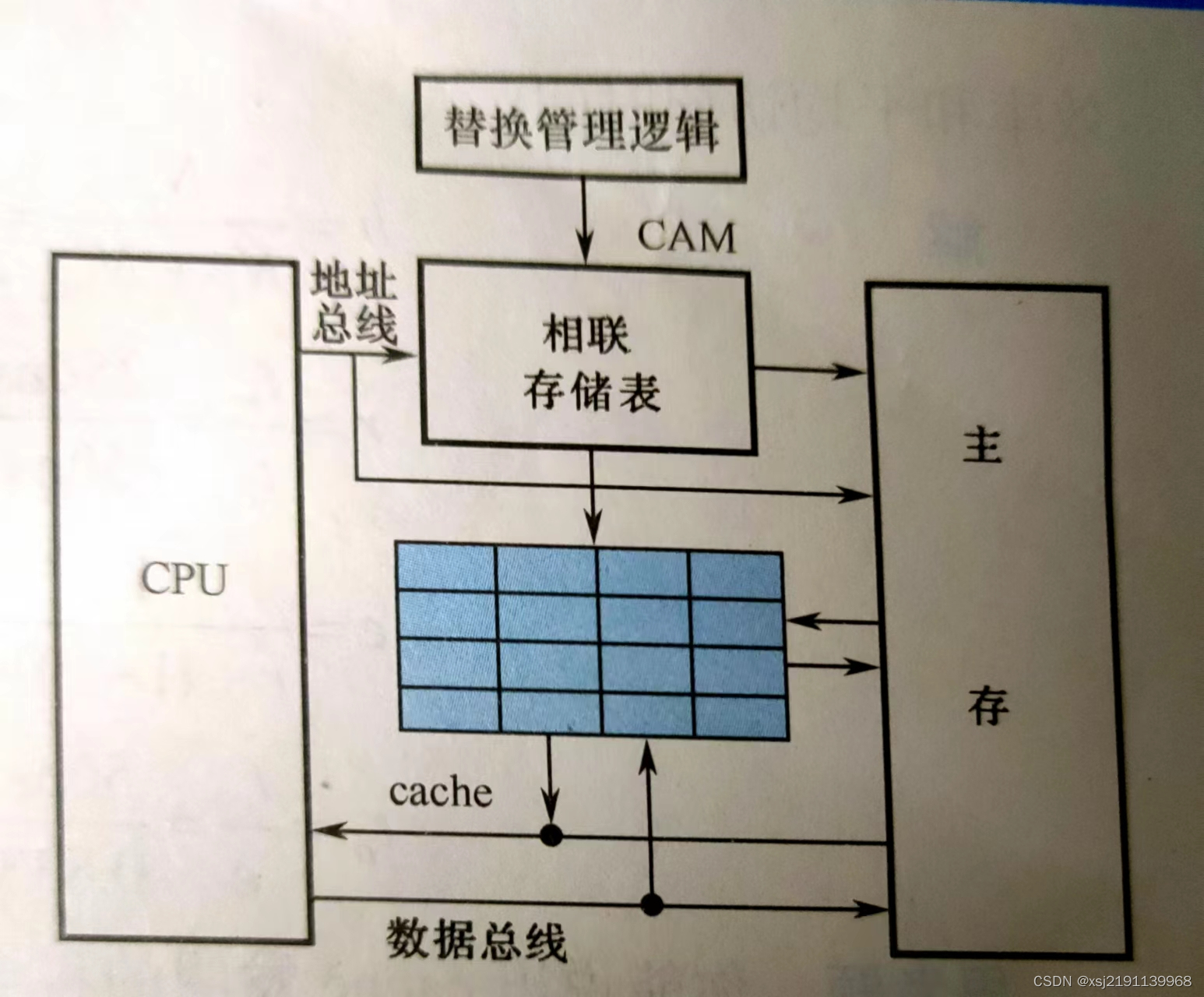

2.cache 的基本原理

cache 除包含SRAM外,还要有控制逻辑 若cache在CPU 芯片外,它的控制逻辑般与主存控制逻得合成在一起,称为主存/chace 控制器;若cache在CPU内,则由CPU提供他 的控制逻辑。

CPU与cache之间的数据交换是以字为单位,而cache 与主存之间的数据交换是以块为单位。一个块由若干字组成,是定长的。当CPU读取内存中一个字时,便发出此字的内存地址到cache 和主存。此时cache 控制逻辑依据地址判断此字当前是否在cache中:若是, cache命中 ,此字立即传送给CPU:若非,则cache 缺失(未命中),用主存读周期把此字从主存读出送到CPU,与此同时, 把含有这个字的整个数据块从主存读出送到cache 中。

3.cache 的命中率

从CPU来看,增加cache 的目的,就是在性能上使主存的平均读出时间尽可能接近cache 的读出时间。为了达到这个目的,在所有的存储器访问中由cache满足CPU需要的部分应占很高的比例,即cache的命中率应接近于1。由于程序访问的局部性,实现这个目标是可能的。

本文介绍缓存(cache)的基本原理及其如何通过利用程序访问的局部性来提高CPU访问数据的速度。文中详细解释了缓存的工作机制,包括缓存命中与缺失的情况,并探讨了如何通过增加缓存来提升整体系统的性能。

本文介绍缓存(cache)的基本原理及其如何通过利用程序访问的局部性来提高CPU访问数据的速度。文中详细解释了缓存的工作机制,包括缓存命中与缺失的情况,并探讨了如何通过增加缓存来提升整体系统的性能。

3383

3383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?