名称:mealy型状态机设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

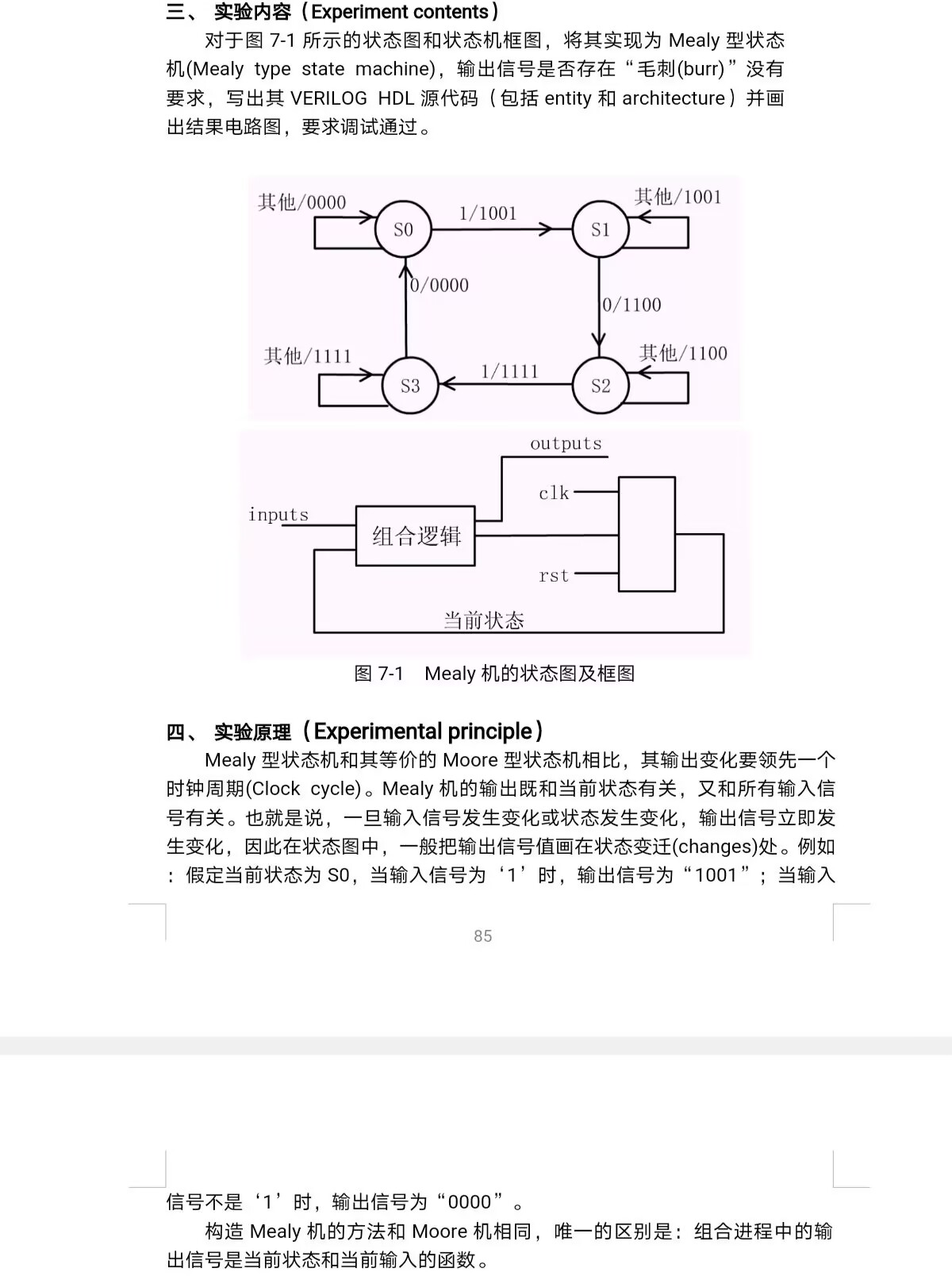

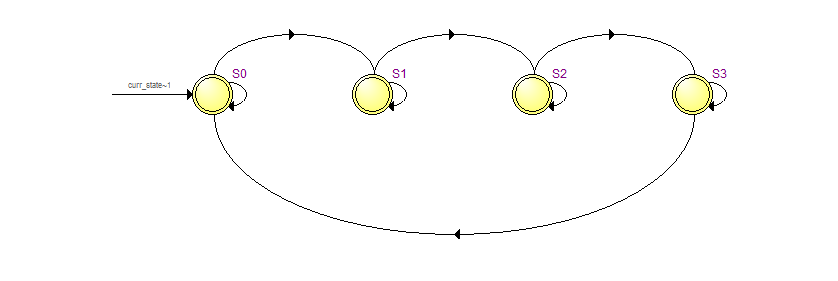

对于图7-1所示的状态图和状态机框图,将其实现为Mealy型状态机(Mealy type state machine),输出信号是否存在“毛刺(burr)”没有要求,写出其VERILOG HDL源代码(包括entity和architecture)并画出结果电路图,要求调试通过。

实验原理(Experimental principle )

Mealy型状态机和其等价的Moore型状态机相比,其输出变化要领先一个时钟周期(Clock cycle)。Mealy机的输出既和当前状态有关,又和所有输入信号有关。也就是说,一旦输入信号发生变化或状态发生变化,输出信号立即发

生变化,因此在状态图中,一般把输出信号值画在状态变迁(changes)处。例如:假定当前状态为S0,当输入信号为‘1’时,输出信号为“1001”;当输入

信号不是‘1’时,输出信号为“0000”。

构造 Mealy机的方法和Moore机相同,唯一的区别是:组合进程中的输

出信号是当前状态和当前输入的函数。

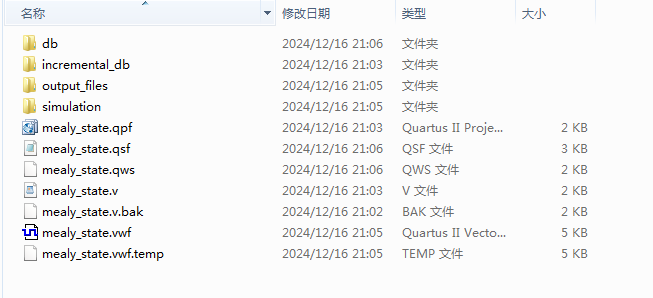

1.工程文件

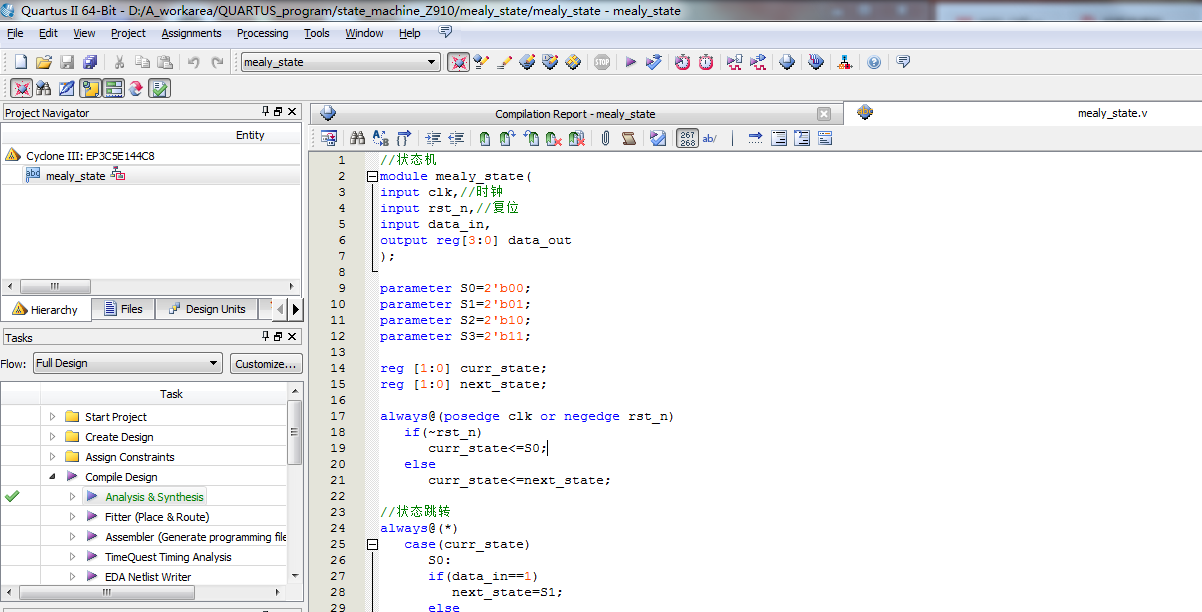

2.程序文件

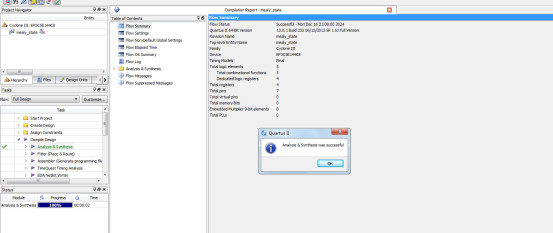

3.程序编译

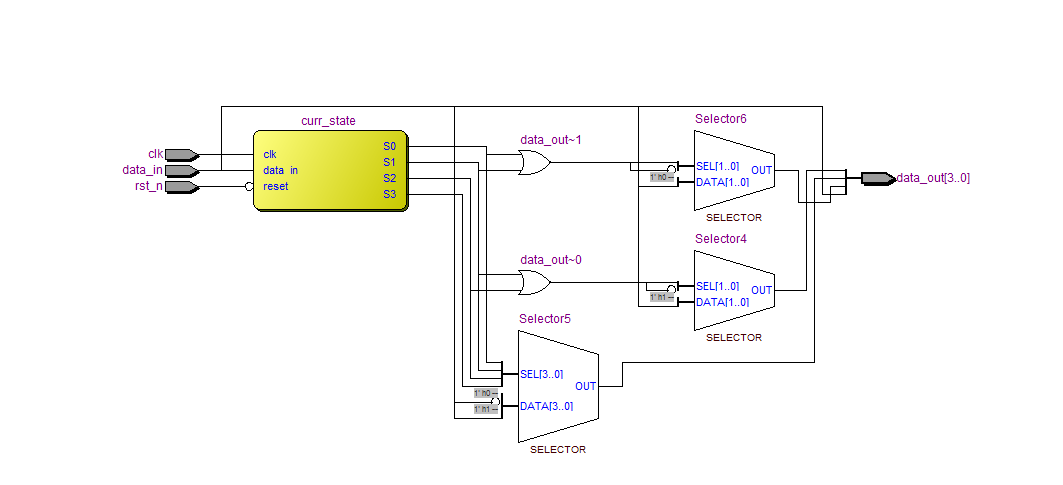

4.RTL图

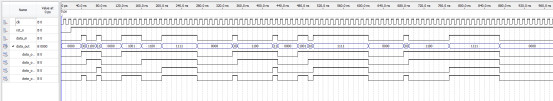

5.仿真图

部分代码展示:

//状态机 module mealy_state( input clk,//时钟 input rst_n,//复位 input data_in, output reg[3:0] data_out ); parameter S0=2'b00; parameter S1=2'b01; parameter S2=2'b10; parameter S3=2'b11; reg [1:0] curr_state; reg [1:0] next_state; always@(posedge clk or negedge rst_n) if(~rst_n) curr_state<=S0; else curr_state<=next_state; //状态跳转 always@(*) case(curr_state) S0: if(data_in==1) next_state=S1; else next_state=S0; S1: if(data_in==0) next_state=S2; else next_state=S1; S2: if(data_in==1) next_state=S3; else next_state=S2; S3: if(data_in==0) next_state=S0; else next_state=S3; endcase

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?