名称:数字密码引爆器设计Verilog代码VIVADO PYNQ开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

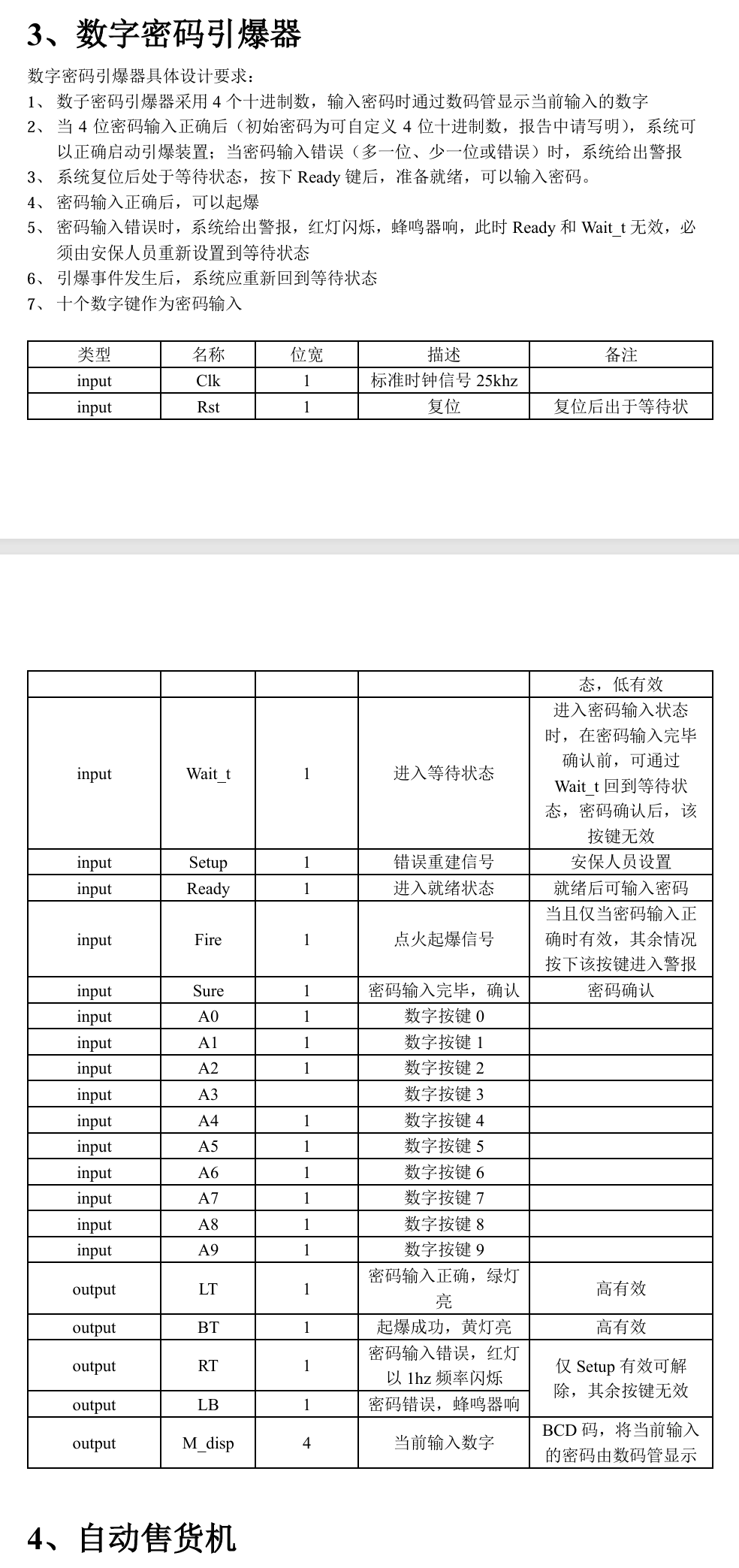

数字密码引爆器

数字密码引爆器具体设计要求:

1、数子密码引爆器采用4个十进制数,输入密码时通过数码管显示当前输入的数字

2、当4位密码输入正确后(初始密码为可自定义4位十进制数,报告中请写明),系统冋以正确启动引爆装置;当密码输入错误(多一位、少一位或错误)时,系统给岀警报

3、系统复位后处于等待状态,按下 Ready键后,准备就绪,可以输入密码

4、密码输入正确后,可以起爆

5、密码输入错误时,系统给岀警报,红灯闪烁,蜂鸣器响,此时 Ready和 Wait t无效,必须由安保人员重新设置到等待状态

6、引爆事件发生后,系统应重新回到等待状态

7、十个数字键作为密码输入

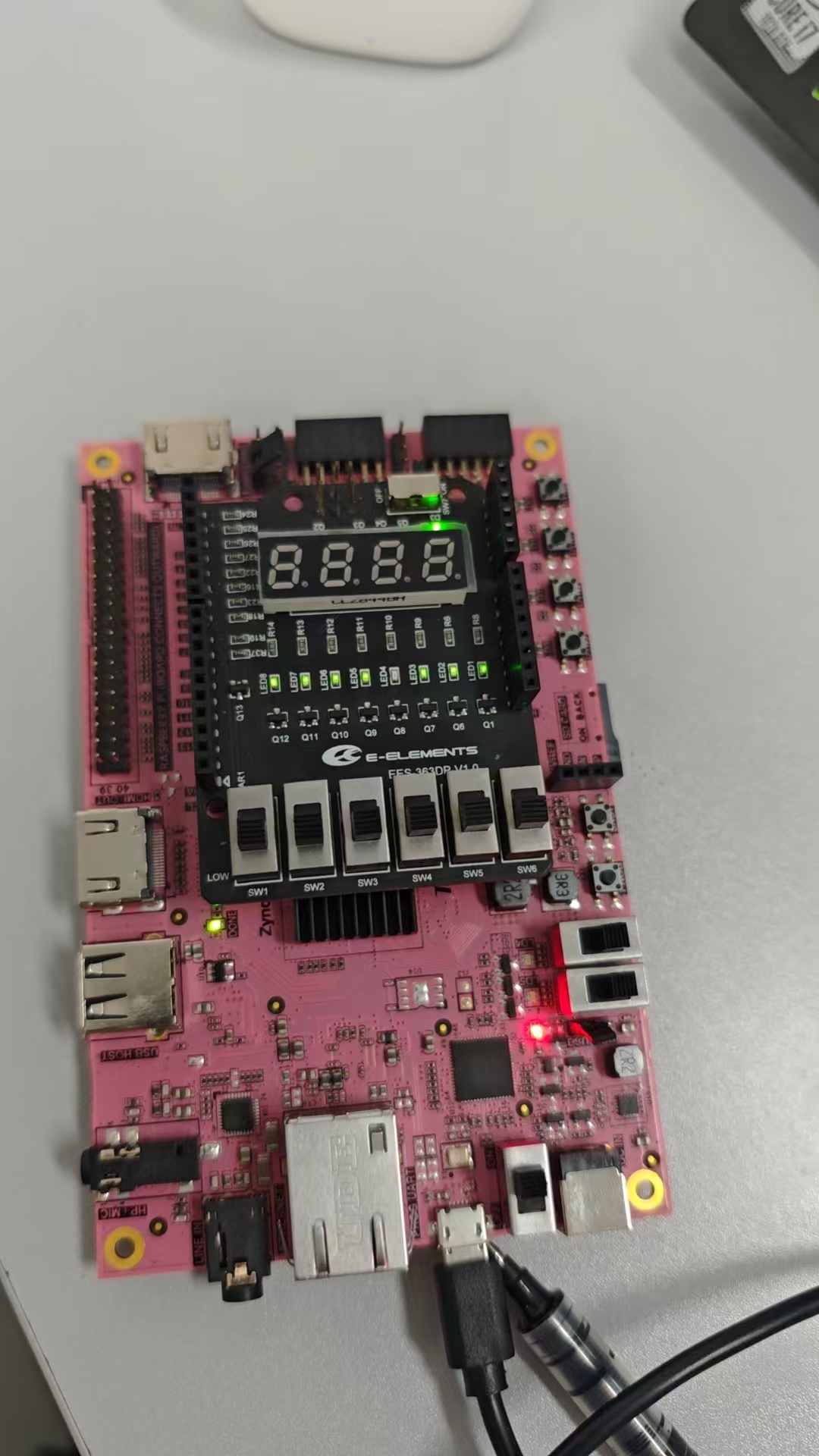

本代码已在PYNQ开发板验证,PYNQ开发板如下,其他开发板可以修改管脚适配:

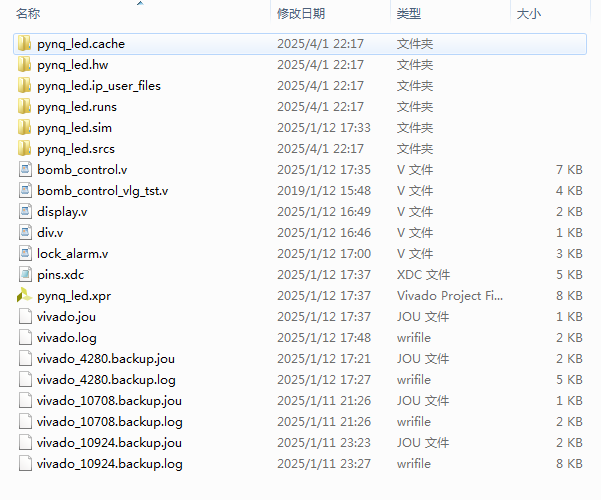

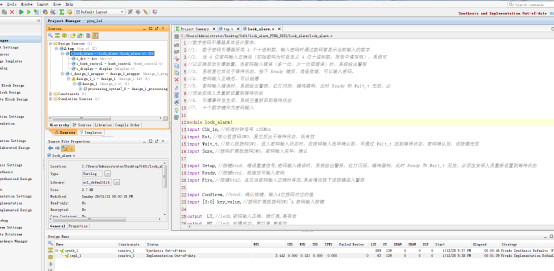

1、工程文件

2、程序文件

3、程序编译

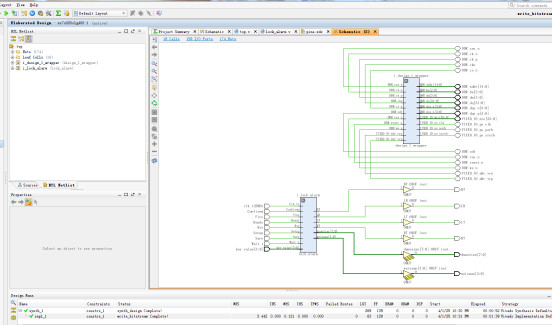

4、RTL图

5、管脚分配

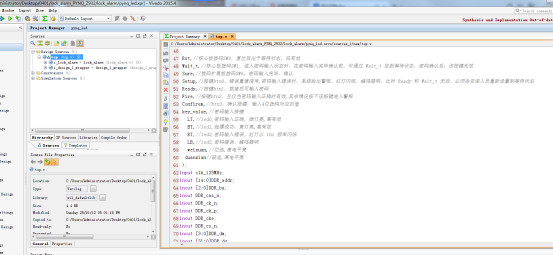

部分代码展示:

//数字密码引爆器具体设计要求: //1、 数子密码引爆器采用 4 个十进制数,输入密码时通过数码管显示当前输入的数字 //2、 当 4 位密码输入正确后(初始密码为可自定义 4 位十进制数,报告中请写明),系统可 //以正确启动引爆装置;当密码输入错误(多一位、少一位或错误)时,系统给出警报 //3、 系统复位后处于等待状态,按下 Ready 键后,准备就绪,可以输入密码。 //4、 密码输入正确后,可以起爆 //5、 密码输入错误时,系统给出警报,红灯闪烁,蜂鸣器响,此时 Ready 和 Wait_t 无效,必 //须由安保人员重新设置到等待状态 //6、 引爆事件发生后,系统应重新回到等待状态 //7、 十个数字键作为密码输入 module bomb_control( input Clk,//标准时钟信号 500Hz input Rst,//核心板拨码SW0,复位后出于等待状态,低有效 input Wait_t,//核心板拨码SW1,进入密码输入状态时,在密码输入完毕确认前,可通过 Wait_t 回到等待状态,密码确认后,该按键无效 input Sure,//拨码扩展板拨码SW6。密码输入完毕,确认 input Setup,//按键btn0,错误重建信号,密码输入错误时,系统给出警报,红灯闪烁,蜂鸣器响,此时 Ready 和 Wait_t 无效,必须由安保人员重新设置到等待状态 input Ready,//按键btn1,就绪后可输入密码 input Fire,//按键btn2,且仅当密码输入正确时有效,其余情况按下该按键进入警报 input Confirem,//btn3,确认按键,输入4位拨码对应的值 input [3:0] key_value,//密码输入按键 //input A0,//密码输入按键 //input A1,//密码输入按键 //input A2,//密码输入按键 //input A3,//密码输入按键 //input A4,//密码输入按键 //input A5,//密码输入按键 //input A6,//密码输入按键 //input A7,//密码输入按键 //input A8,//密码输入按键 //input A9,//密码输入按键 output [3:0] state, output LT,//led0,密码输入正确,绿灯亮,高有效 output BT,//led1,起爆成功,黄灯亮,高有效 output RT,//led2,密码输入错误,红灯以 1hz 频率闪烁 output LB,//led3,密码错误,蜂鸣器响 output [15:0] M_disp//当前输入数字 ); parameter mima=16'h5643;//定义初始密码为5643 //定义4个寄存器储存输入密码 reg [15:0] number_mima=16'd0;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?