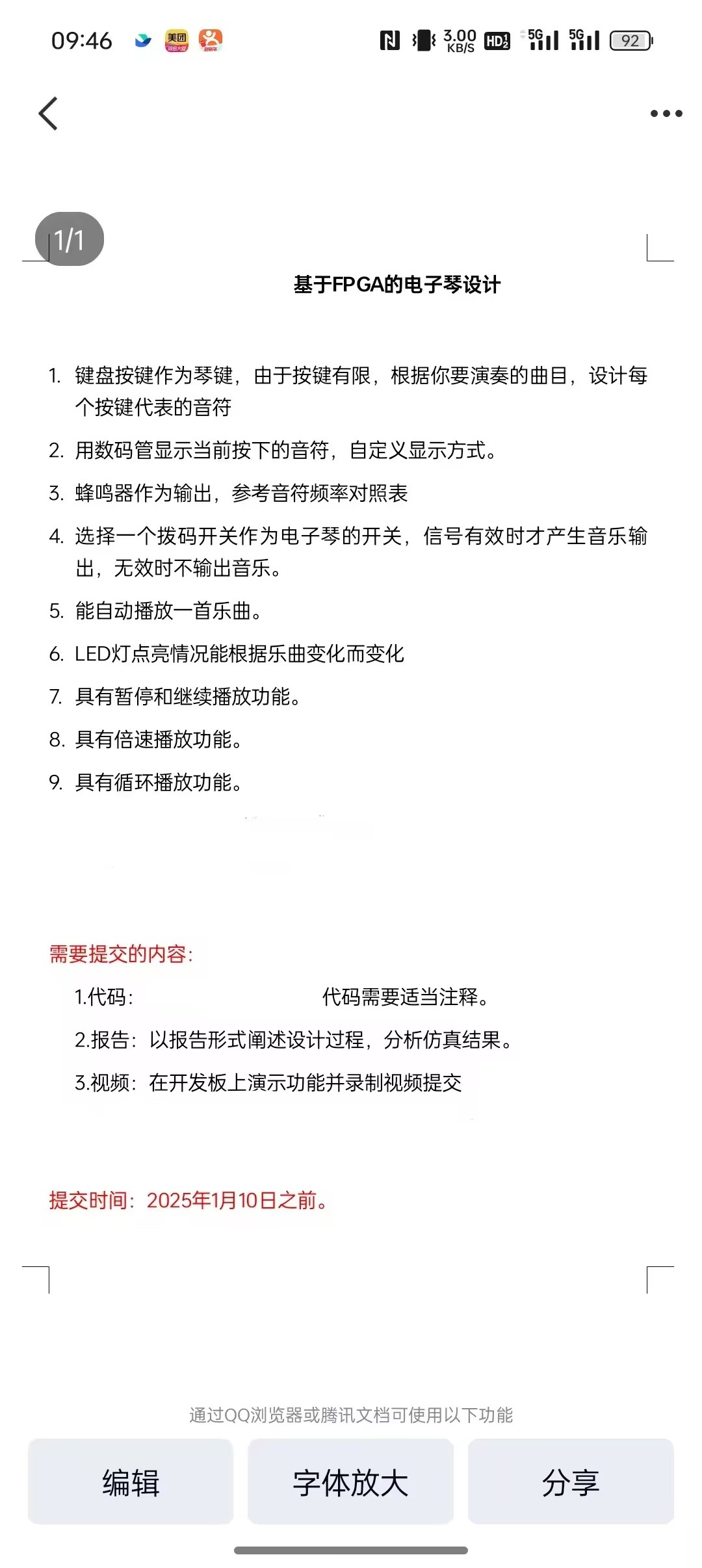

名称:基于FPGA的电子琴设计Verilog代码VIVADO 硬木课堂开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

1.键盘按键作为琴键,由于按键有限,根据你要演奏的曲目,设计每个按键代表的音符

2.用数码管显示当前按下的音符,自定义显示方式。

3.蜂鸣器作为输出,参考音符频率对照表

4.选择一个拔码开关作为电子琴的开关,信号有效时才产生音乐输出,无效时不输出音乐。

5.能自动播放一首乐曲。

6.LED灯点亮情况能根据乐曲变化而变化

7.具有暂停和继续播放功能。

8.具有倍速播放功能。

9.具有循环播放功能

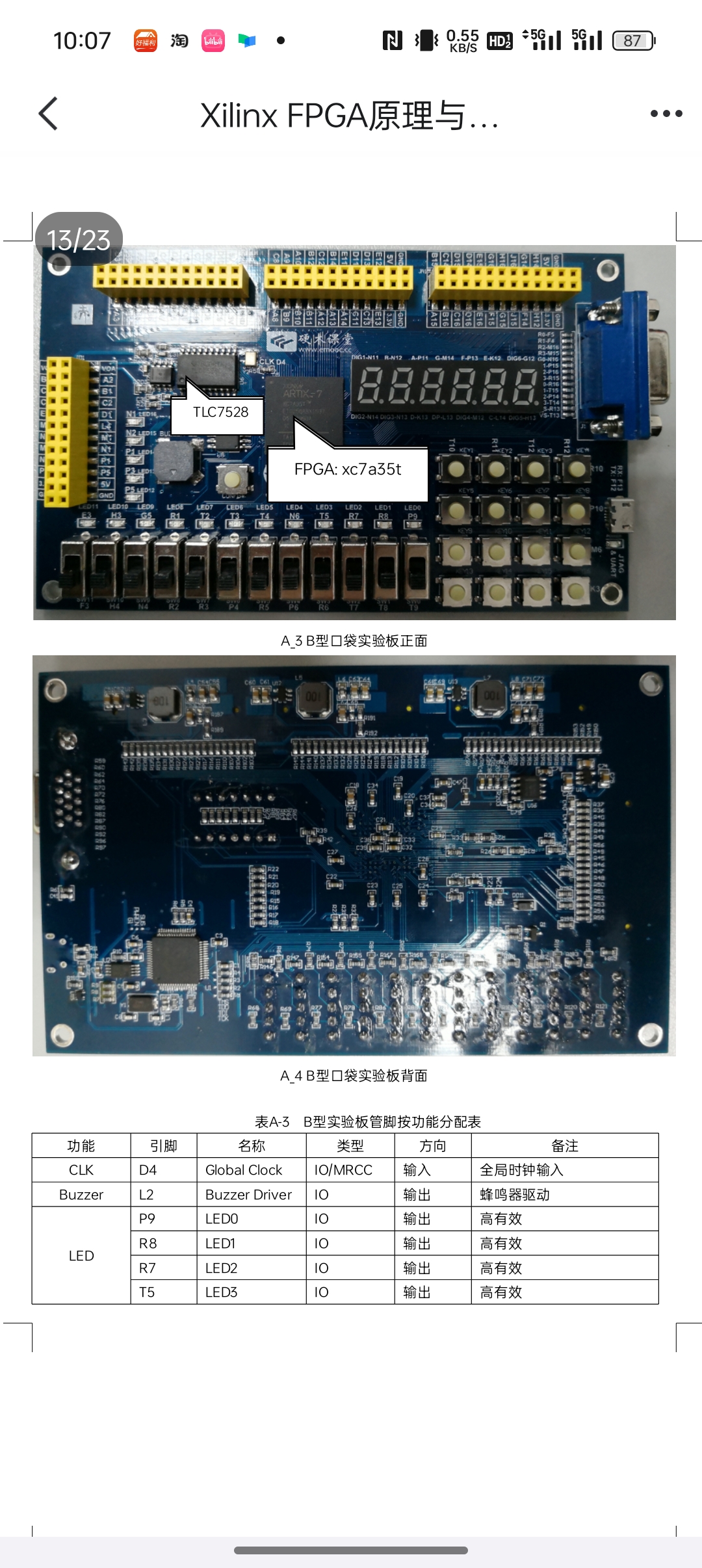

本代码已在硬木课堂开发板验证,硬木课堂开发板如下,其他开发板可以修改管脚适配:

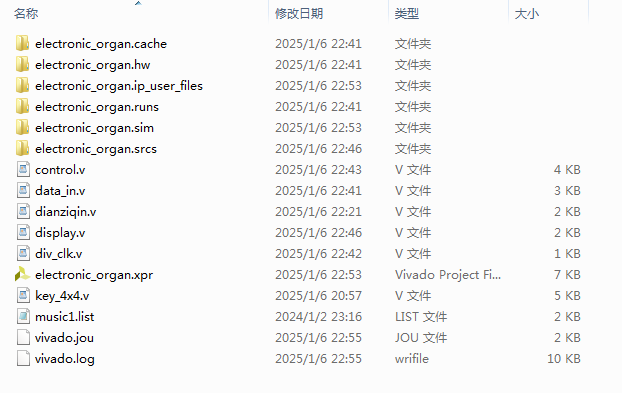

1、工程文件

2、程序文件

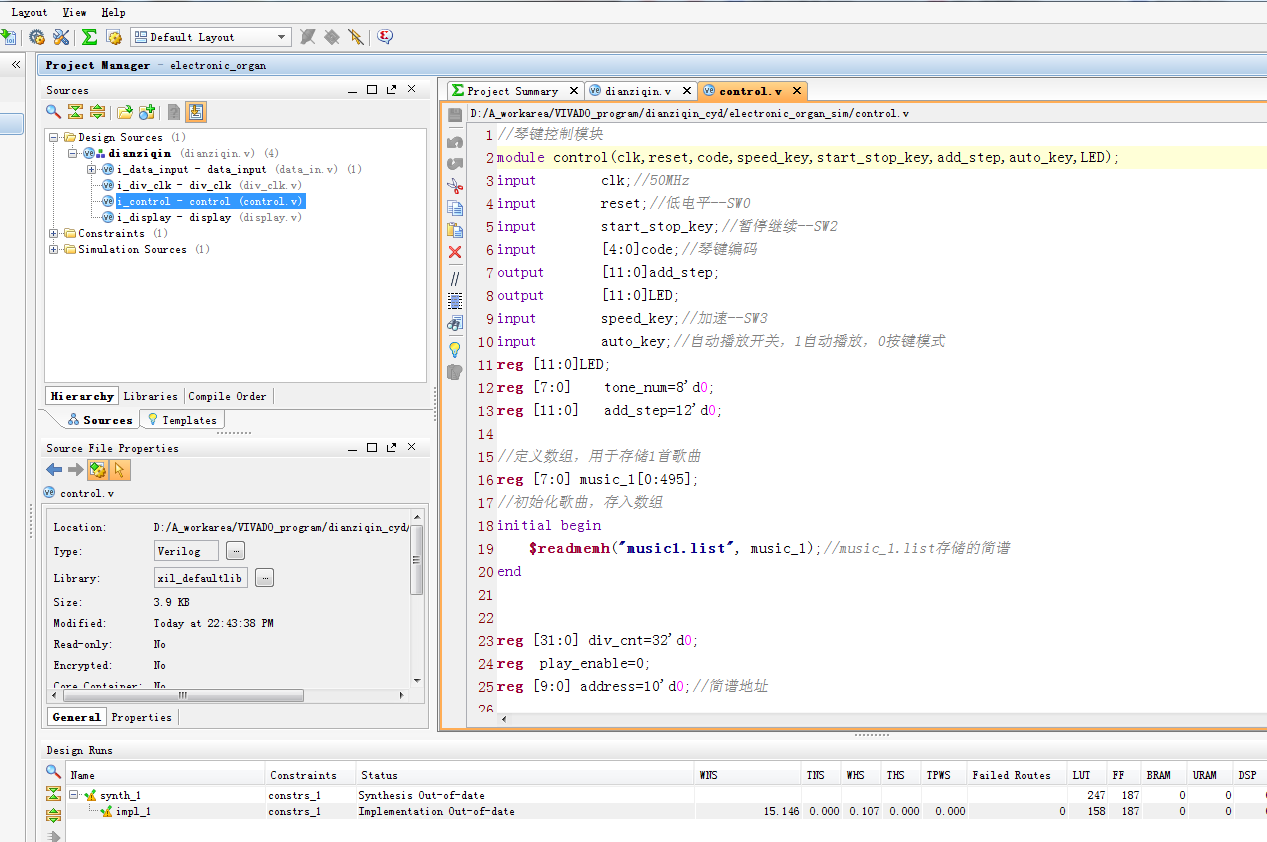

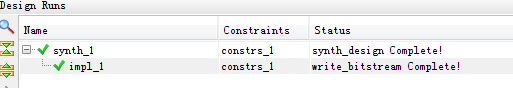

3、程序编译

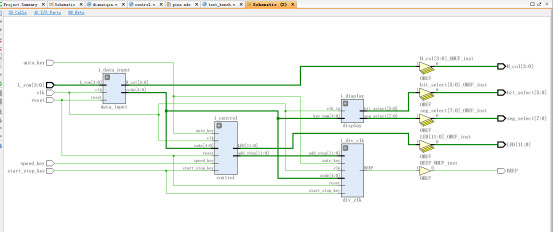

4、RTL图

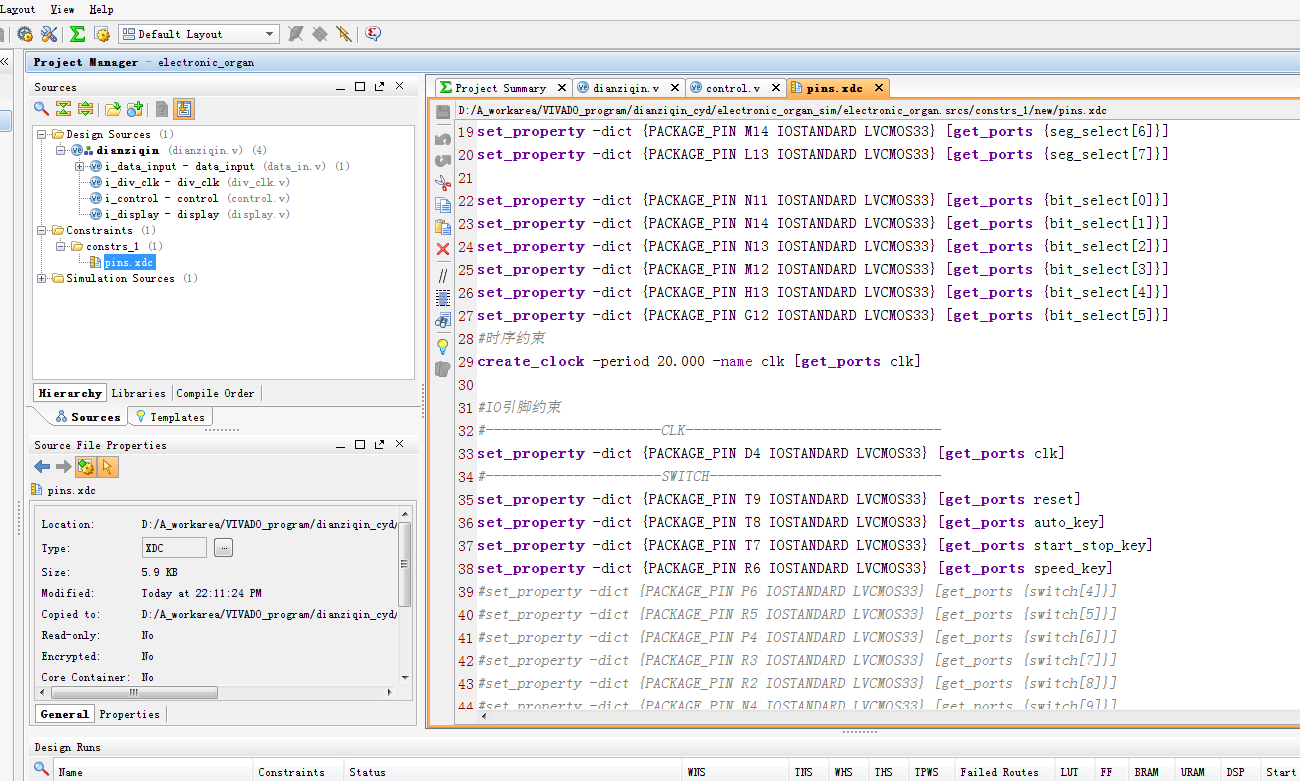

5、管脚分配

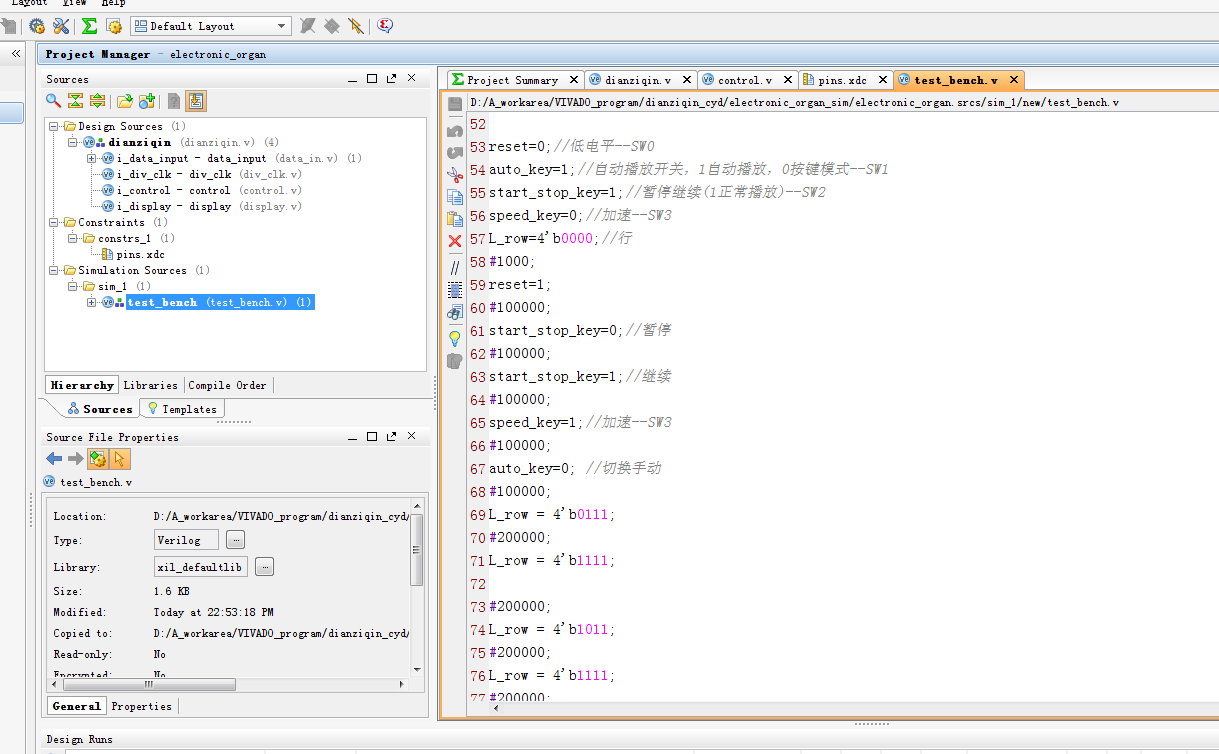

6、Testbench

7、仿真图

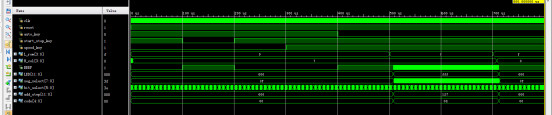

整体仿真图

按键输入模块

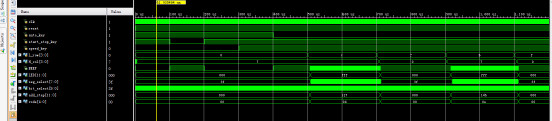

分频模块

琴键控制

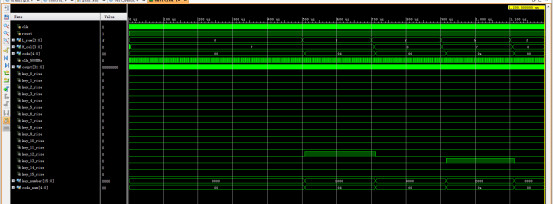

数码管显示

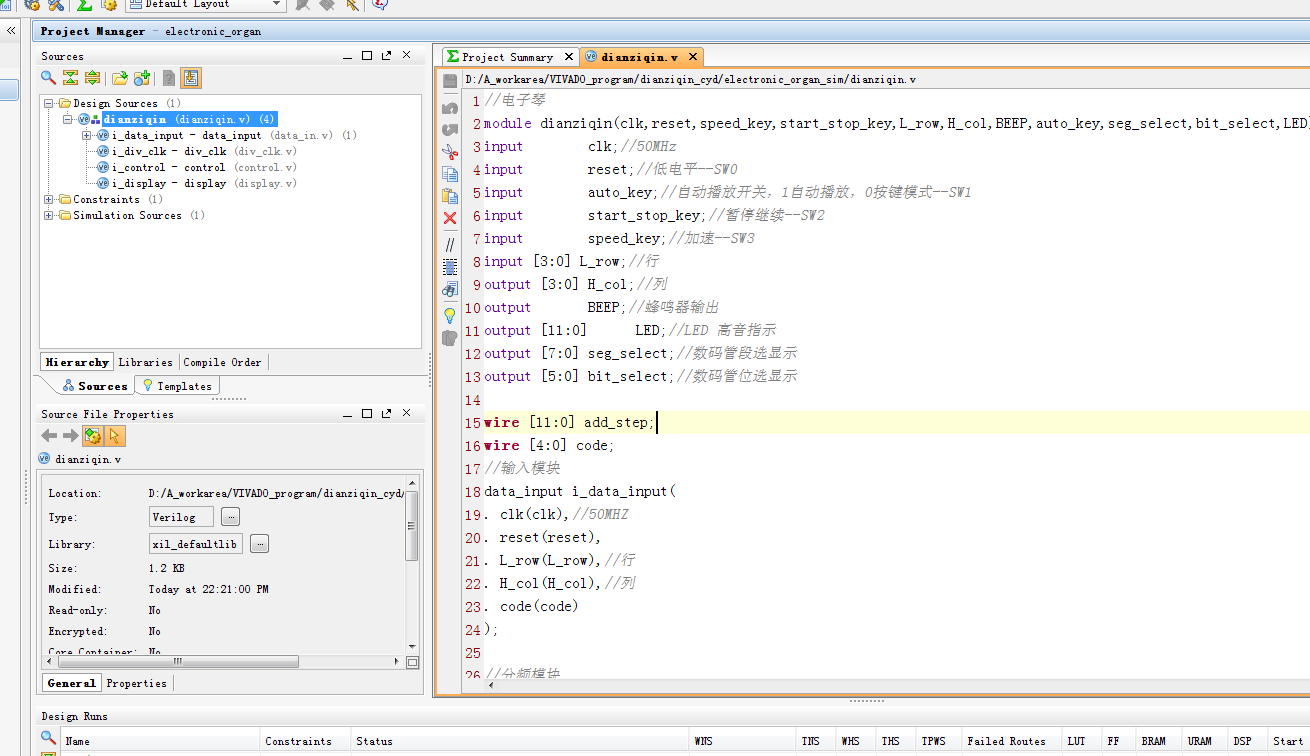

部分代码展示:

//琴键控制模块

module control(clk,reset,code,speed_key,start_stop_key,add_step,auto_key,LED);

input clk;//50MHz

input reset;//低电平--SW0

input start_stop_key;//暂停继续--SW2

input [4:0]code;//琴键编码

output [11:0]add_step;

output [11:0]LED;

input speed_key;//加速--SW3

input auto_key;//自动播放开关,1自动播放,0按键模式

reg [11:0]LED;

reg [7:0] tone_num=8'd0;

reg [11:0] add_step=12'd0;

//定义数组,用于存储1首歌曲

reg [7:0] music_1[0:495];

//初始化歌曲,存入数组

initial begin

$readmemh("music1.list", music_1);//music_1.list存储的简谱

end

reg [31:0] div_cnt=32'd0;

reg play_enable=0;

reg [9:0] address=10'd0;//简谱地址

wire [31:0] speed_para;

assign speed_para= (speed_key==0) ? 32'd3597122 : 32'd1798561;

always @(posedge clk)

begin

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?