名称:自动量程等精度频率计设计Verilog代码Quartus DE2-115开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

自动量程等精度频率计

1、使用等精度测频法设计频率计

2、频率分2档,1Hz和1KHz,当检测到频率大于1MHz时,自动切换到KHz单位

3、闸门信号1秒

4、被测频率超过50M时输出超量程指示

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

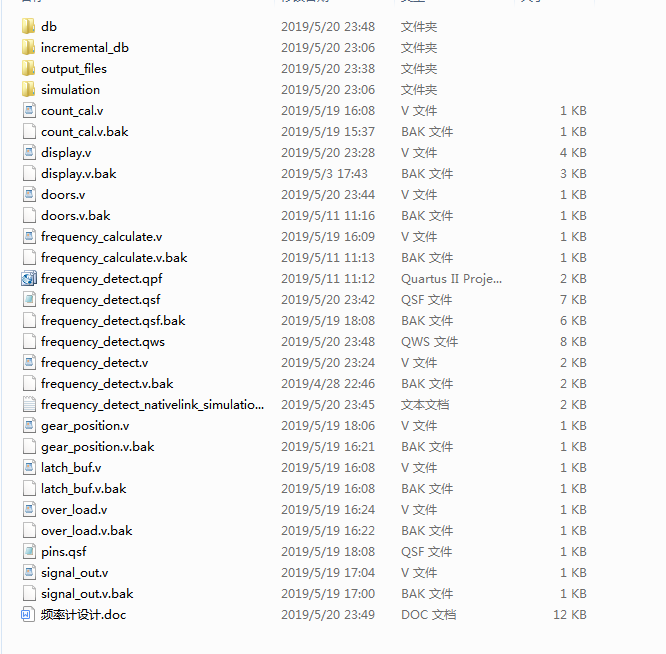

1. 工程文件

2. 程序文件

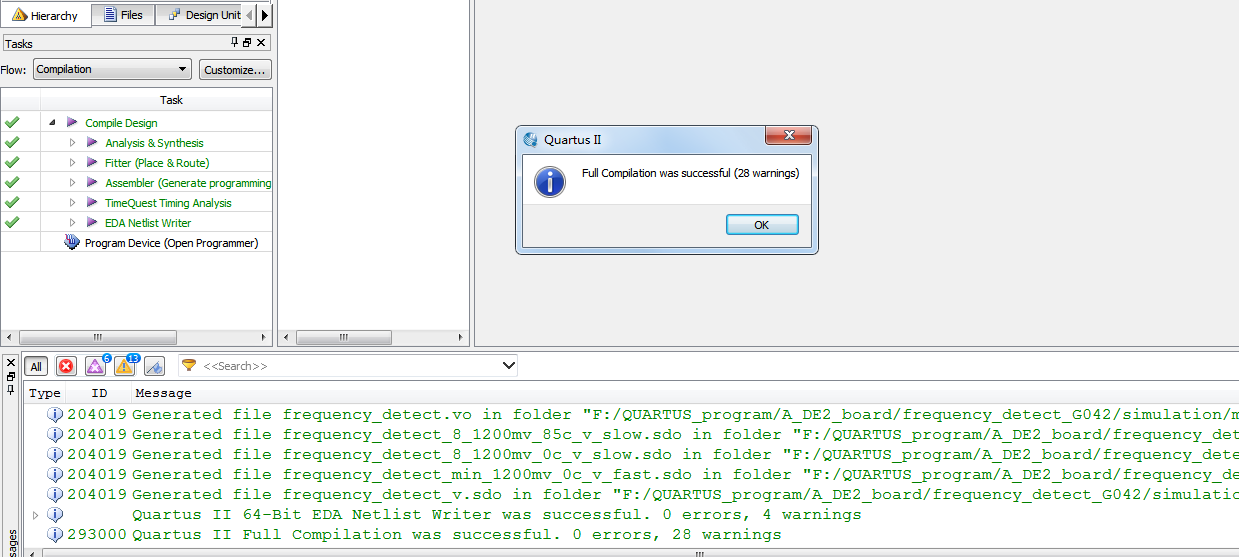

3. 程序编译

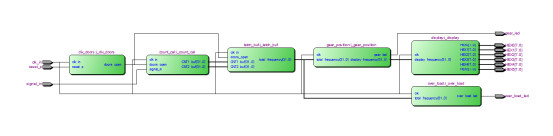

4. 程序RTL图(结构图)

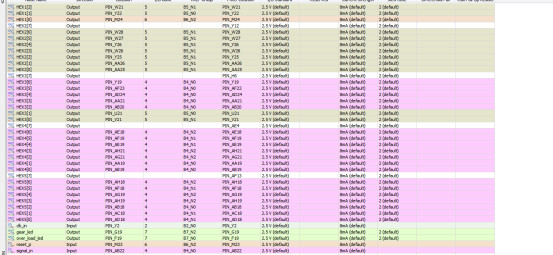

5. 管脚分配

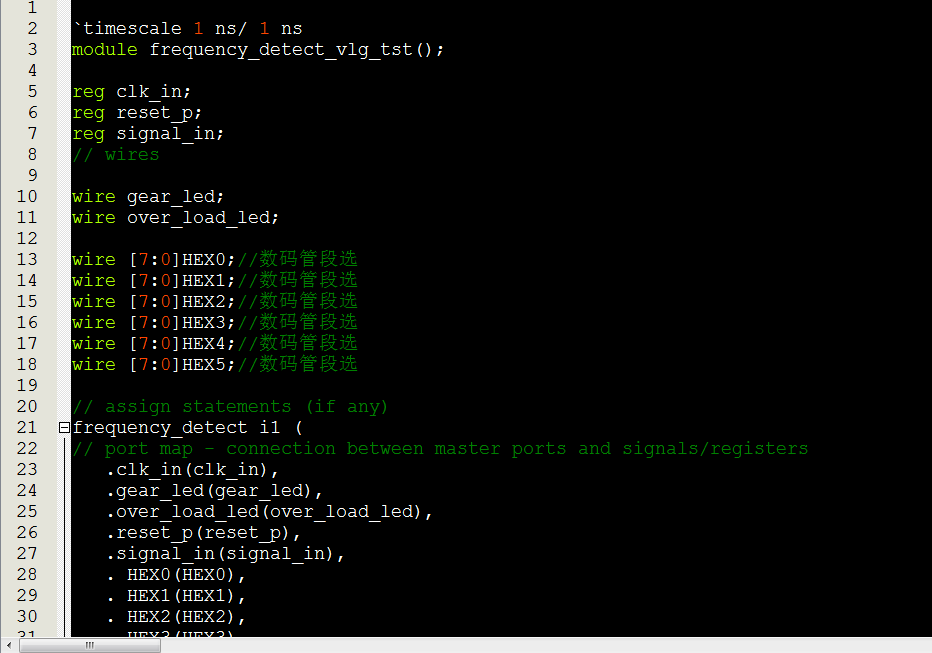

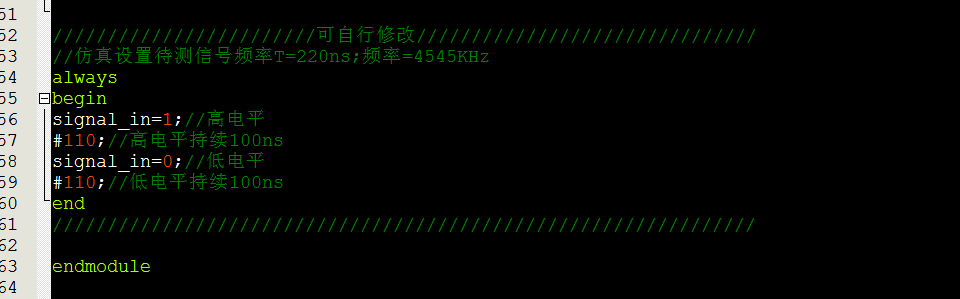

6. Testbench

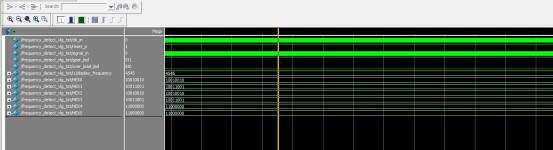

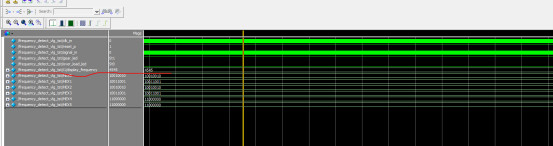

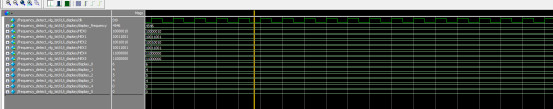

7. 仿真图

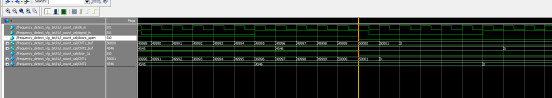

上图可看出测得频率为4545KHz,与testbench设置的待测信号频率一致,仿真正确

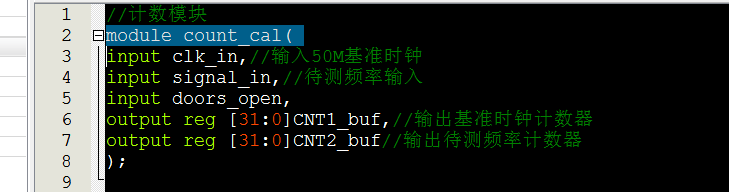

计数模块

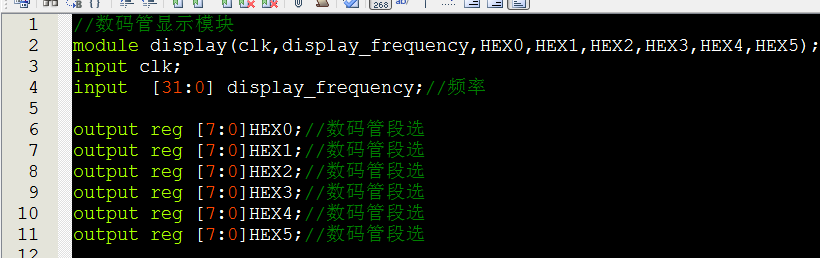

显示模块

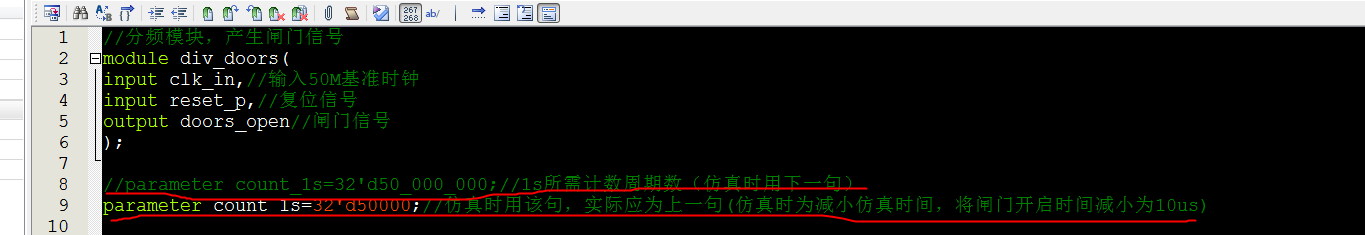

闸门信号产生模块

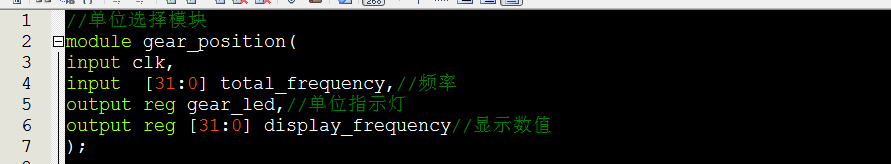

单位选择模块

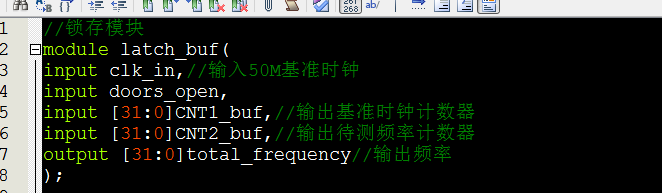

锁存模块

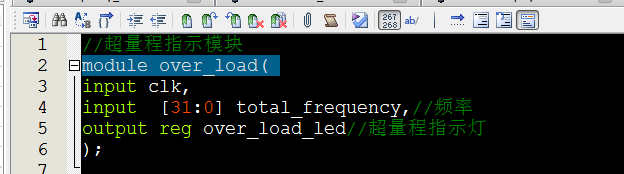

超量程模块

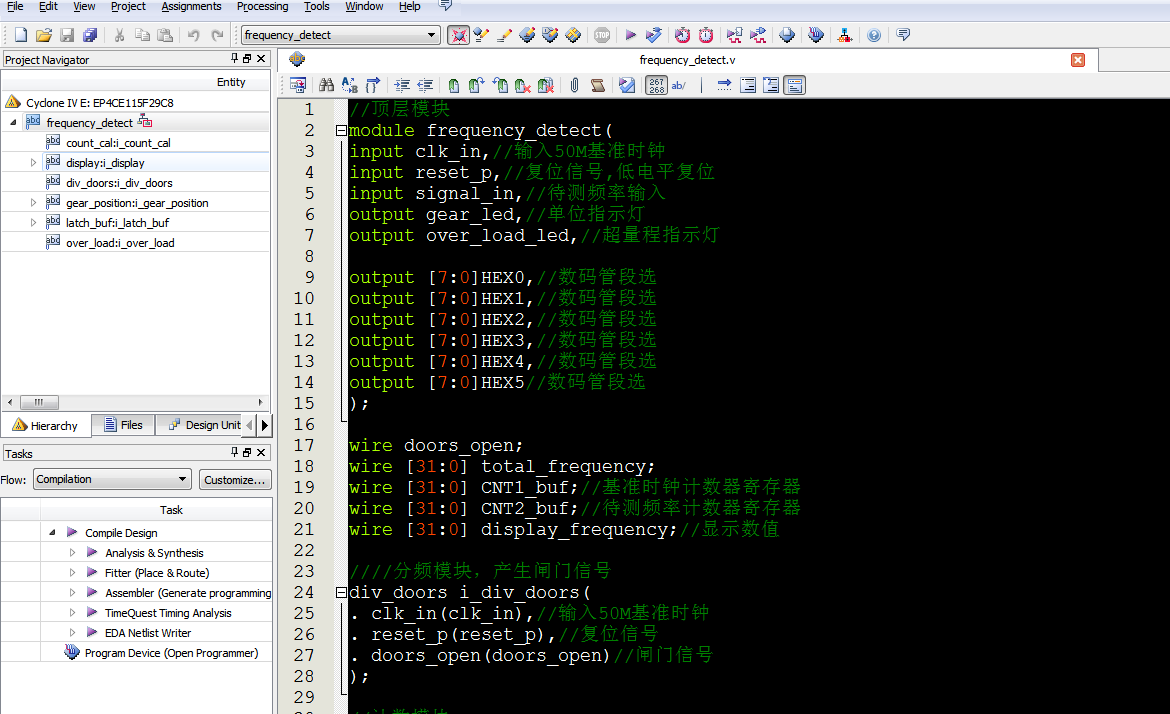

部分代码展示:

//顶层模块 module frequency_detect( input clk_in,//输入50M基准时钟 input reset_p,//复位信号,低电平复位 input signal_in,//待测频率输入 output gear_led,//单位指示灯 output over_load_led,//超量程指示灯 output [7:0]HEX0,//数码管段选 output [7:0]HEX1,//数码管段选 output [7:0]HEX2,//数码管段选 output [7:0]HEX3,//数码管段选 output [7:0]HEX4,//数码管段选 output [7:0]HEX5//数码管段选 ); wire doors_open; wire [31:0] total_frequency; wire [31:0] CNT1_buf;//基准时钟计数器寄存器 wire [31:0] CNT2_buf;//待测频率计数器寄存器 wire [31:0] display_frequency;//显示数值 分频模块,产生闸门信号 div_doors i_div_doors( . clk_in(clk_in),//输入50M基准时钟 . reset_p(reset_p),//复位信号 . doors_open(doors_open)//闸门信号 ); //计数模块 count_cal i_count_cal( . clk_in(clk_in),//输入50M基准时钟 . signal_in(signal_in),//待测频率输入 . doors_open(doors_open), . CNT1_buf(CNT1_buf),//输出基准时钟计数器 . CNT2_buf(CNT2_buf)//输出待测频率计数器 );

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?