名称:可调闹钟数字钟设计Verilog代码Quartus 大西瓜开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

1、可以调节小时、分钟

2、可以调整闹钟时间

3、到设置的时间闹铃响

4、具有模式设置按键

模式,0:计时,1设置时间 ,2显示闹钟时间, 3设置闹钟时间

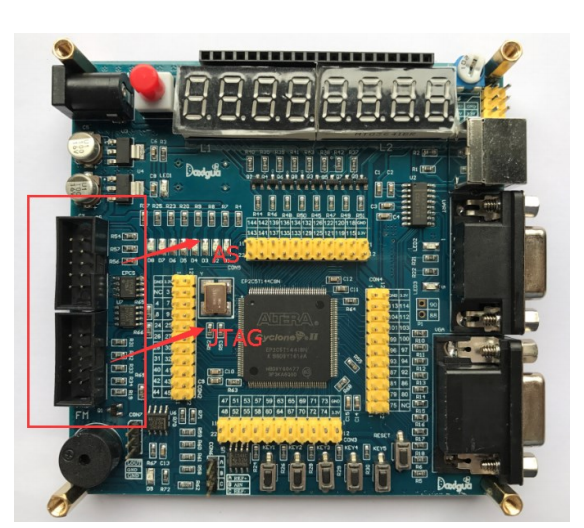

本代码已在大西瓜开发板验证,大西瓜开发板如下,其他开发板可以修改管脚适配:

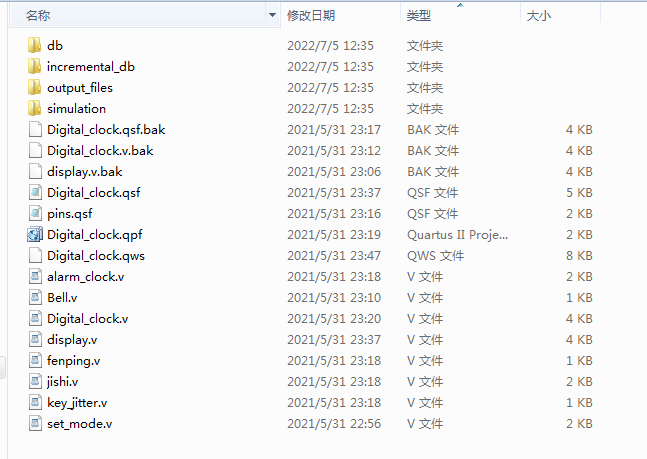

1、工程文件

2、程序文件

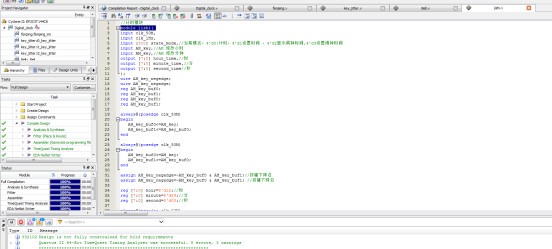

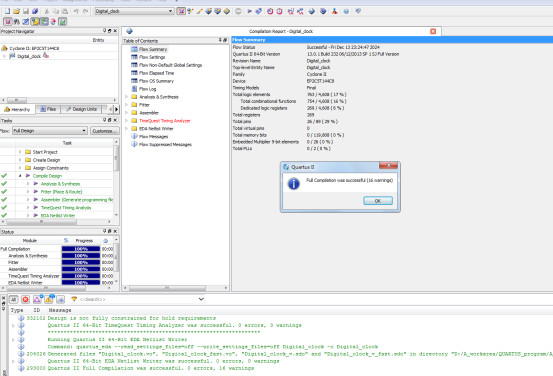

3、程序编译

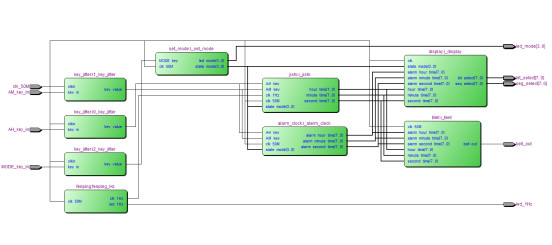

4、RTL图

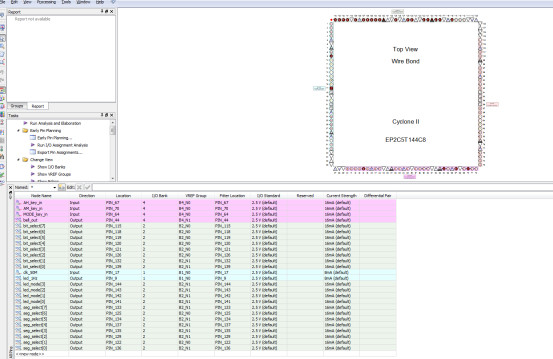

5、管脚分配

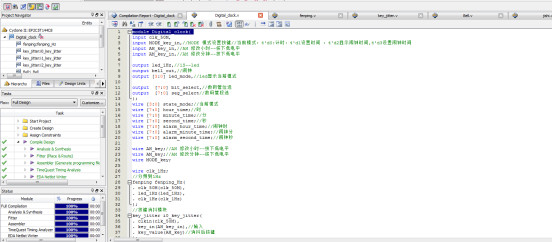

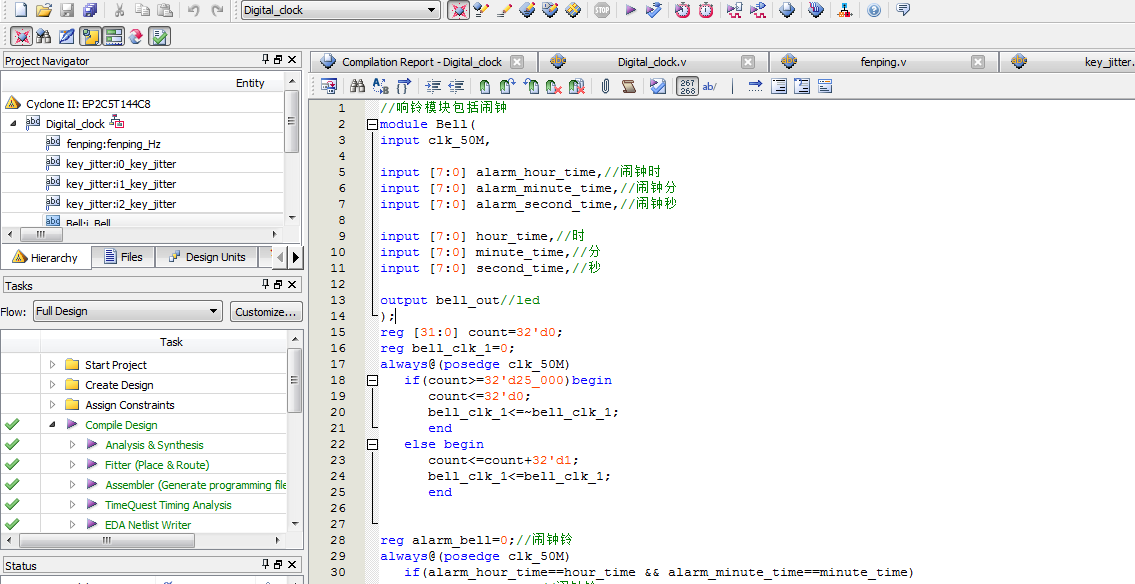

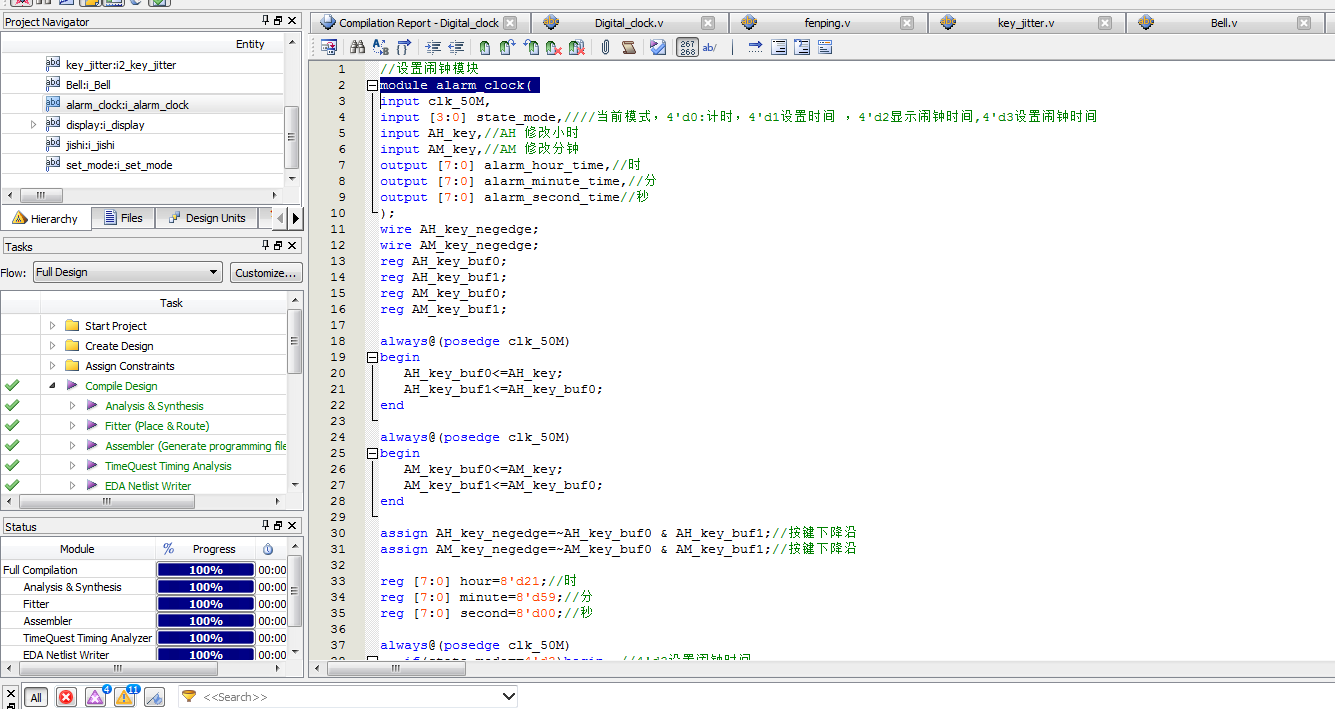

部分代码展示:

//设置闹钟模块 module alarm_clock( input clk_50M, input [3:0] state_mode,当前模式,4'd0:计时,4'd1设置时间 ,4'd2显示闹钟时间,4'd3设置闹钟时间 input AH_key,//AH 修改小时 input AM_key,//AM 修改分钟 output [7:0] alarm_hour_time,//时 output [7:0] alarm_minute_time,//分 output [7:0] alarm_second_time//秒 ); wire AH_key_negedge; wire AM_key_negedge; reg AH_key_buf0; reg AH_key_buf1; reg AM_key_buf0; reg AM_key_buf1; always@(posedge clk_50M) begin AH_key_buf0<=AH_key; AH_key_buf1<=AH_key_buf0; end always@(posedge clk_50M) begin AM_key_buf0<=AM_key; AM_key_buf1<=AM_key_buf0; end assign AH_key_negedge=~AH_key_buf0 & AH_key_buf1;//按键下降沿 assign AM_key_negedge=~AM_key_buf0 & AM_key_buf1;//按键下降沿 reg [7:0] hour=8'd21;//时 reg [7:0] minute=8'd59;//分 reg [7:0] second=8'd00;//秒 always@(posedge clk_50M) if(state_mode==4'd3)begin//4'd3设置闹钟时间 if(AH_key_negedge) if(hour==8'd23) hour<=8'd0; else hour<=hour+8'd1; else hour<=hour; if(AM_key_negedge) if(minute==8'd59) minute<=8'd0; else minute<=minute+8'd1; else minute<=minute; end

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?