名称:基于TLC5510的电压表及LCD1602显示设计Verilog代码Quartus 大西瓜开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基于TLC5510的电压表及LCD1602显示

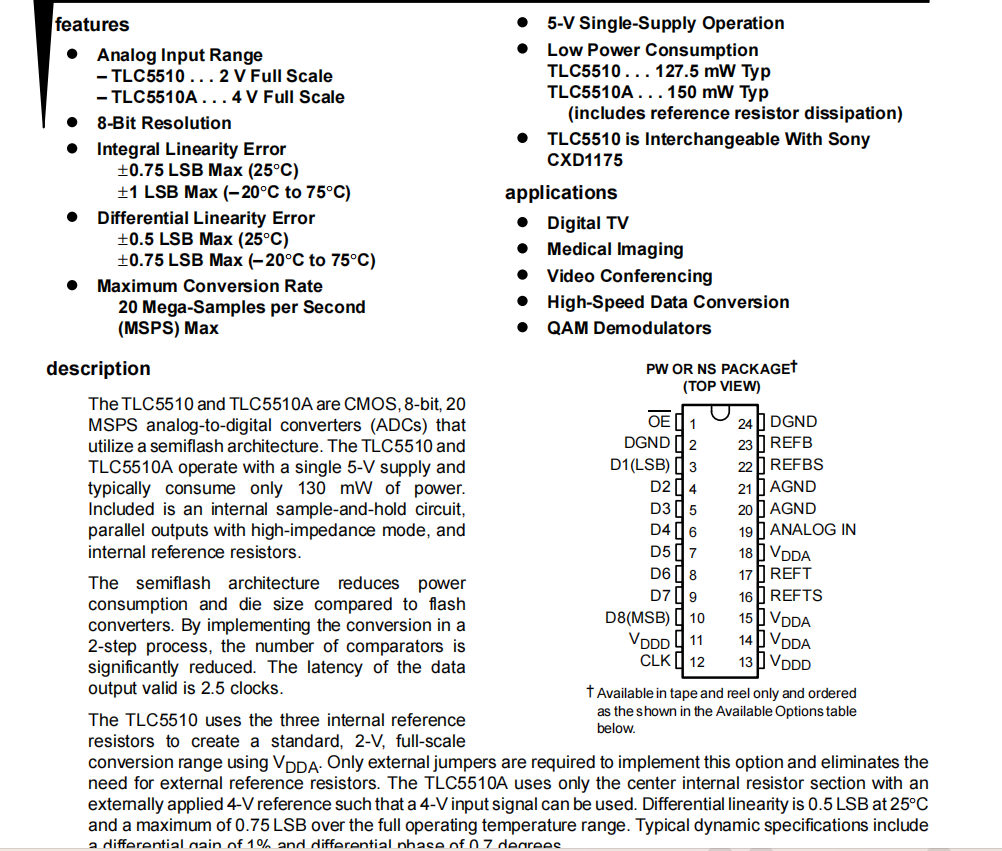

1、设计AD芯片TLC5510的驱动代码

2、通过TLC5510将模拟信号转换成数字信号(AD值)

3、根据基准电压将数字信号(AD值)换算为电压值值

4、将AD值和电压值通过LCD1602显示

5、使用开发板上的IO管脚连接外置的TLC5510芯片模块进行实物验证

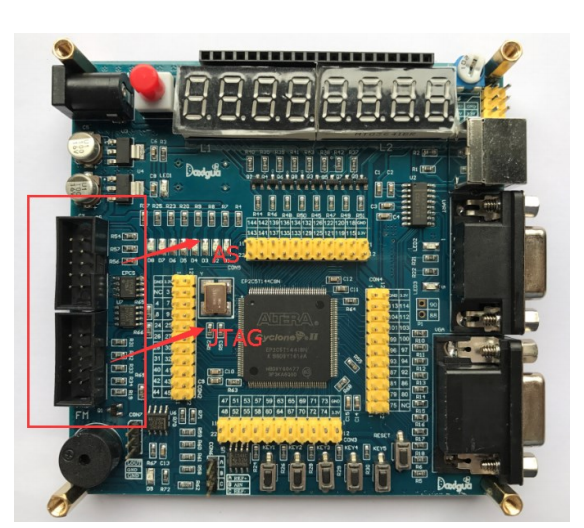

本代码已在大西瓜开发板验证,大西瓜开发板如下,其他开发板可以修改管脚适配:

1、TLC5510

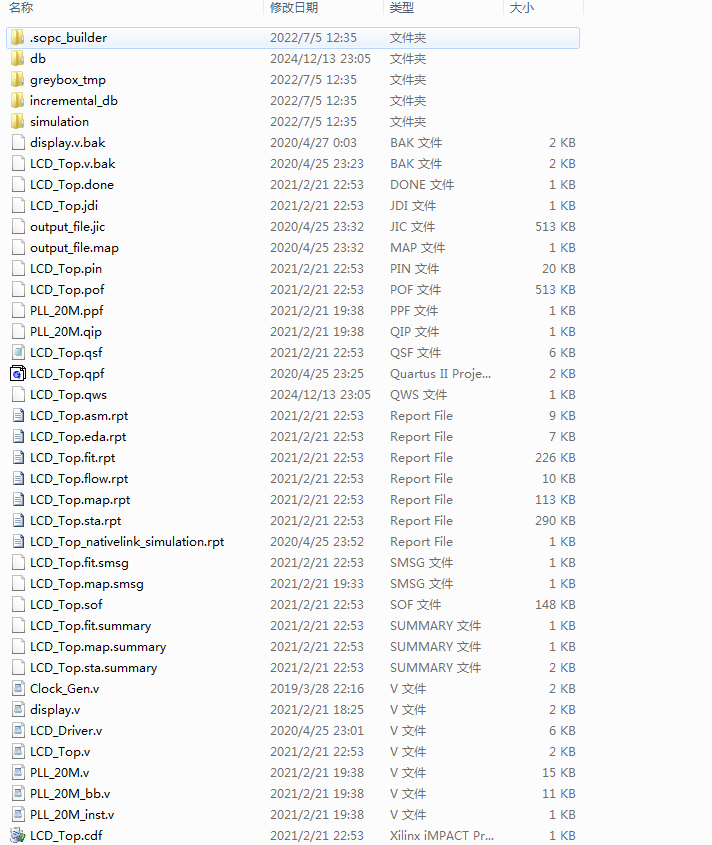

2、工程文件

3、程序文件

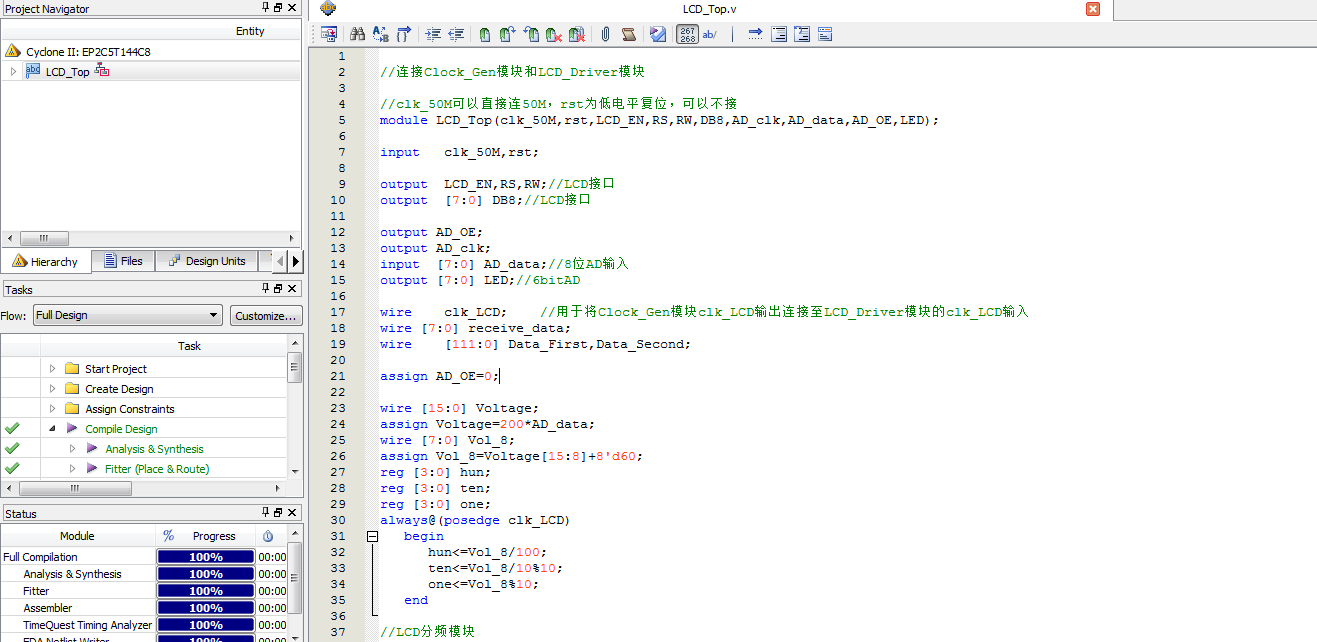

4、程序编译

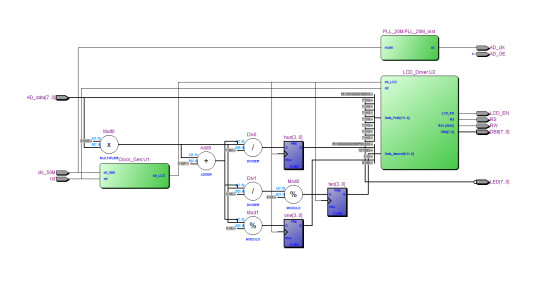

5、RTL图

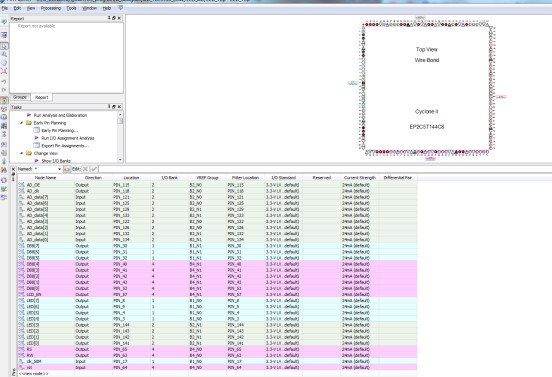

6、管脚分配

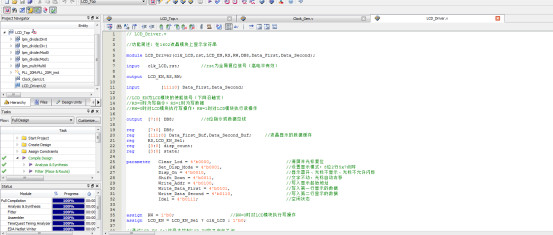

部分代码展示:

/****************为LCD_Drvier模块产生500Hz的时钟信号**************/ module Clock_Gen(clk_50M,rst,clk_LCD); input clk_50M,rst; //rst为全局复位信号(高电平有效) output clk_LCD; wire clk_counter; reg [11:0] cnt; //对时钟进行计数分频 wire clk_equ; reg [9:0] count; reg clk_BUF; parameter counter = 48; //多少分频 /******************************************************************************** ** 模块名称:分频器 ** 功能描述:通过计数器实现分频功能. ********************************************************************************/ always@(posedge clk_50M) begin if(!rst) //低电平复位 cnt <= 12'd0; else if(clk_equ) cnt <= 12'd0; else cnt <= cnt+1'b1; end assign clk_equ = (cnt==counter); assign clk_counter = clk_equ; always @(posedge clk_counter or negedge rst) begin //利用计数器分频产生500Hz时钟 if(!rst) begin clk_BUF <= 1'b0; count <= 10'b0; end

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?