名称:随机数生成器设计Verilog代码Quartus DE2开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

在 Verilog模拟它们并证明它们正常工作

多游戏都需要输入随机数,目标是开发一种可以随机显示在DE2板7段显示屏上的十进制数字。

在此示例中,我们将使用数字作为我们选择的国家彩票的号码,数字的选择从1开始到99

操作如下

1.按KEY0

开始序列

2.然后按KEY3

并且第一个数字显示在HEX3-2上显示4秒

3.然后,系统再次开始计数,重复阶段不能再次选择先前选择的号码

4.重复该过程,直到选了6次

要求:1架构和控制器的描述(用框图表示互连)和所有ASM图表

2七段解码器的每个模块的带注释的 Verilog代码和设计中的所有计数器3七段解码器和设计中的所有计数器的完整仿真,带有注释的仿真表明

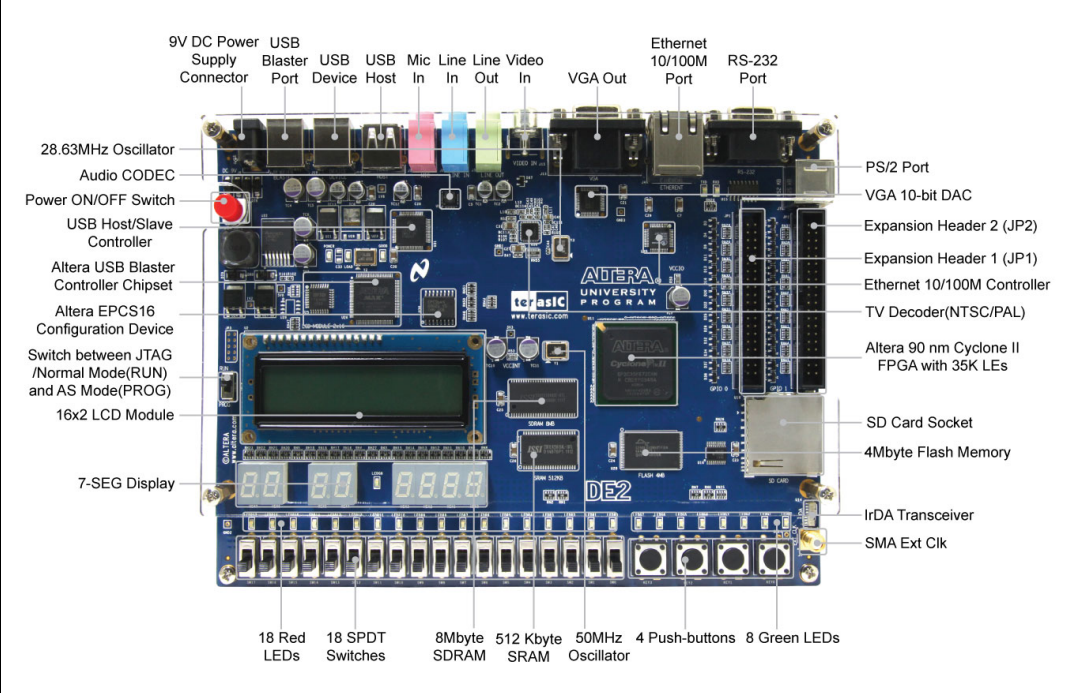

本代码已在DE2开发板验证,DE2开发板如下,其他开发板可以修改管脚适配:

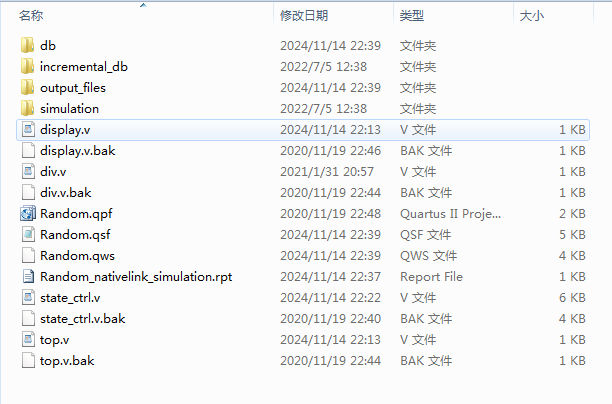

1. 工程文件

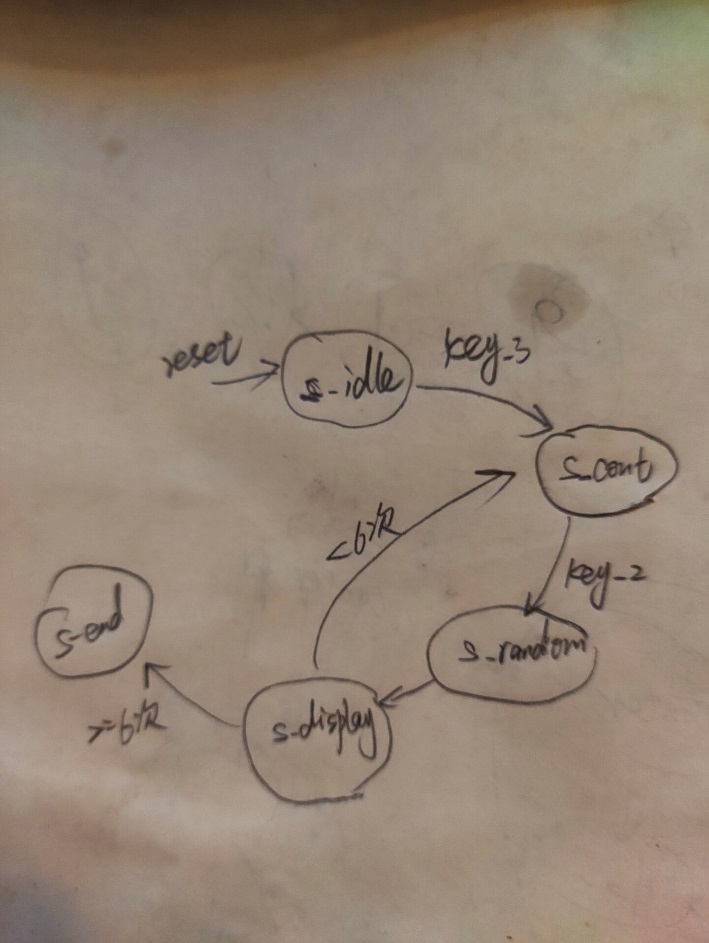

状态机图

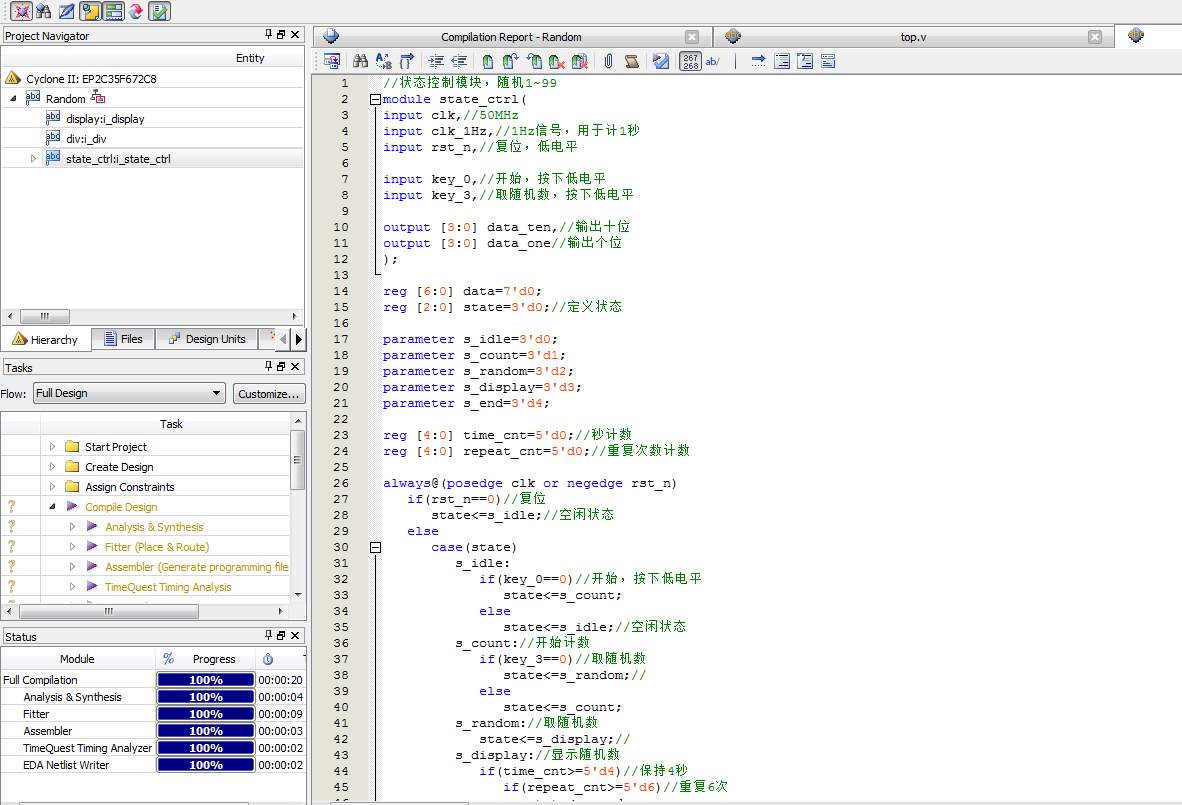

2. 程序文件

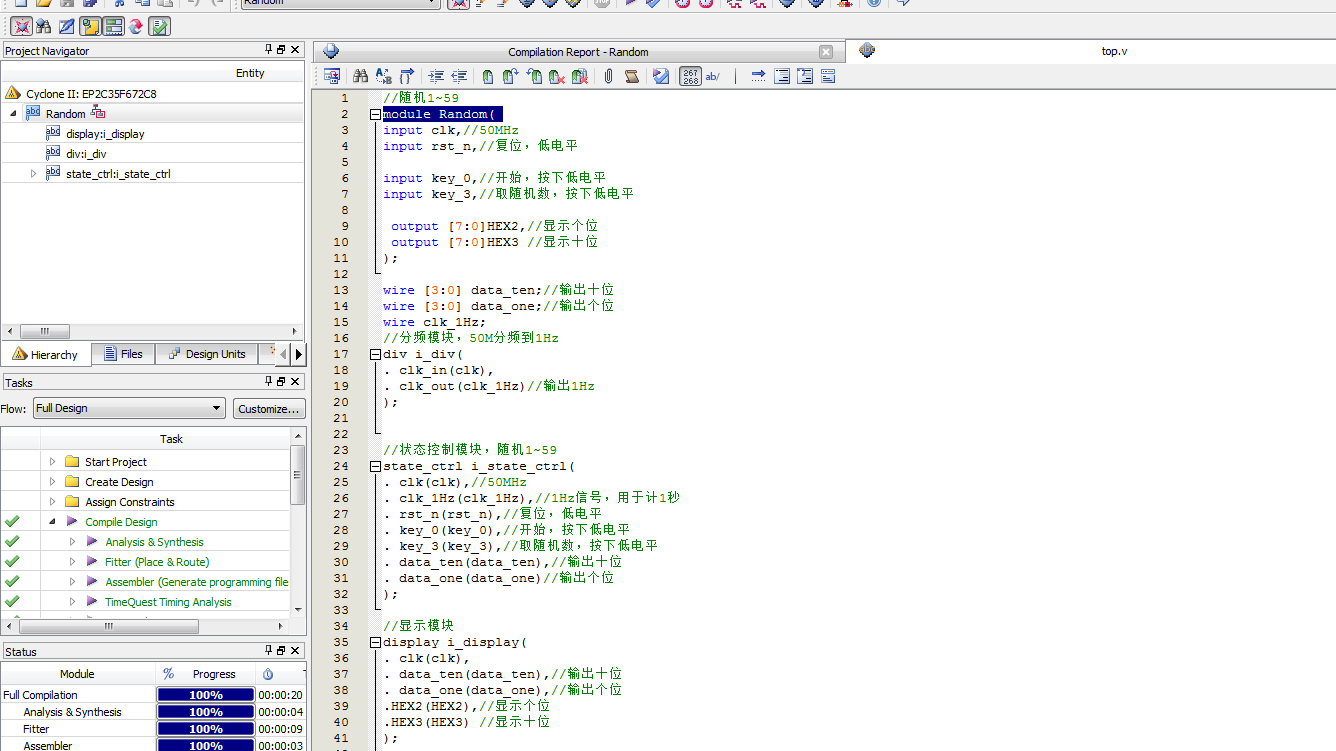

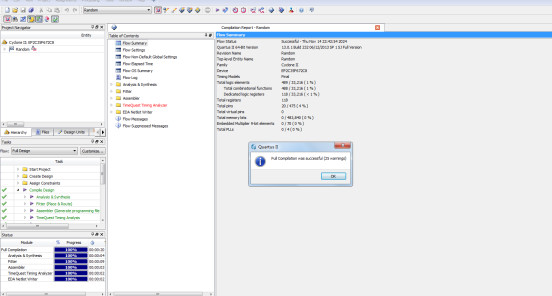

3. 程序编译

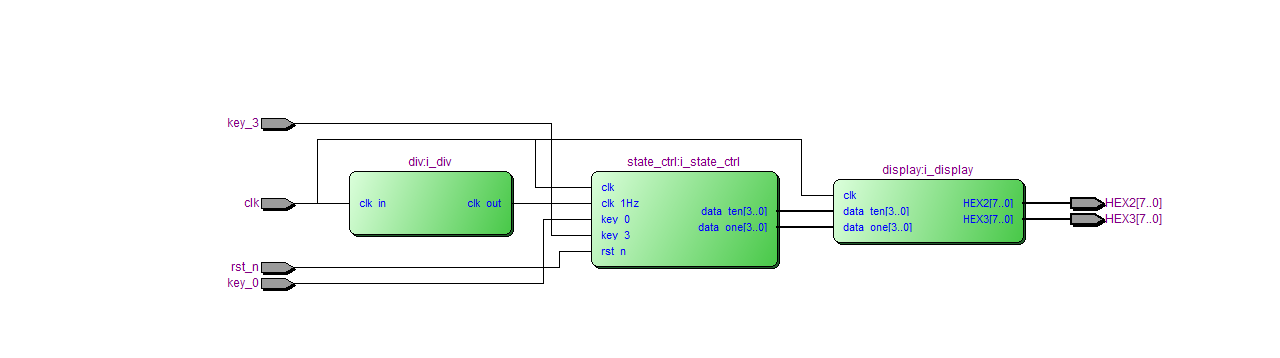

4. RTL图

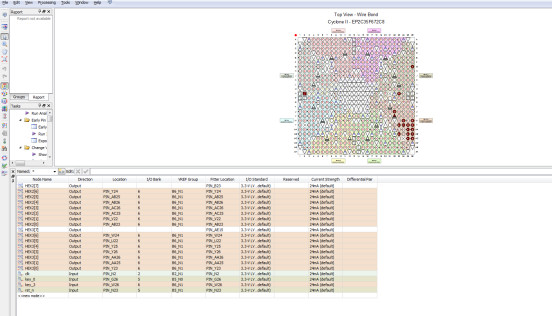

5. 管脚分配

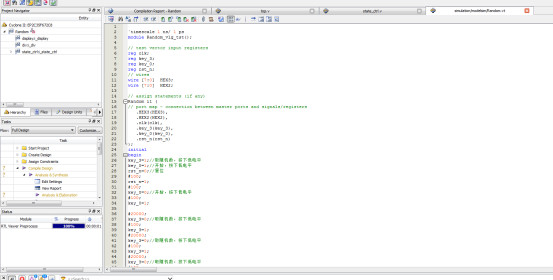

6. Testbench

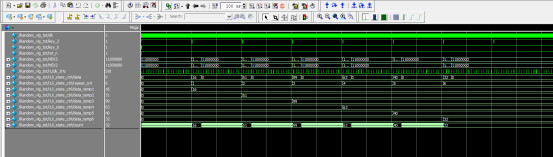

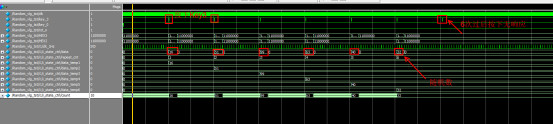

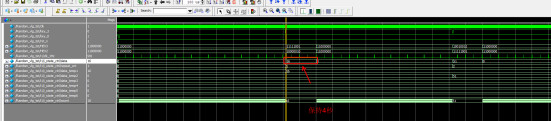

7. 仿真图

部分代码展示:

//显示模块 module display( input clk, input [3:0] data_ten,//输出十位 input [3:0] data_one,//输出个位 output reg [7:0]HEX2,//显示个位 output reg [7:0]HEX3 //显示十位 ); always @(posedge clk) begin case (data_ten) //数字显示码 8'd0: HEX3<= 8'b1100_0000; 8'd1: HEX3<= 8'b1111_1001; 8'd2: HEX3<= 8'b1010_0100; 8'd3: HEX3<= 8'b1011_0000; 8'd4: HEX3<= 8'b1001_1001; 8'd5: HEX3<= 8'b1001_0010; 8'd6: HEX3<= 8'b1000_0010; 8'd7: HEX3<= 8'b1111_1000; 8'd8: HEX3<= 8'b1000_0000; 8'd9: HEX3<= 8'b1001_0000; default:; endcase end

源代码

点击下方的公众号卡片获取

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?