名称:具有状态显示的密码锁设计Verilog代码VIVADO ego1开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

具有状态显示的密码锁设计

实验环境

- 操作系统:Window 10;

- 设计软件:Vivado 2017.4;

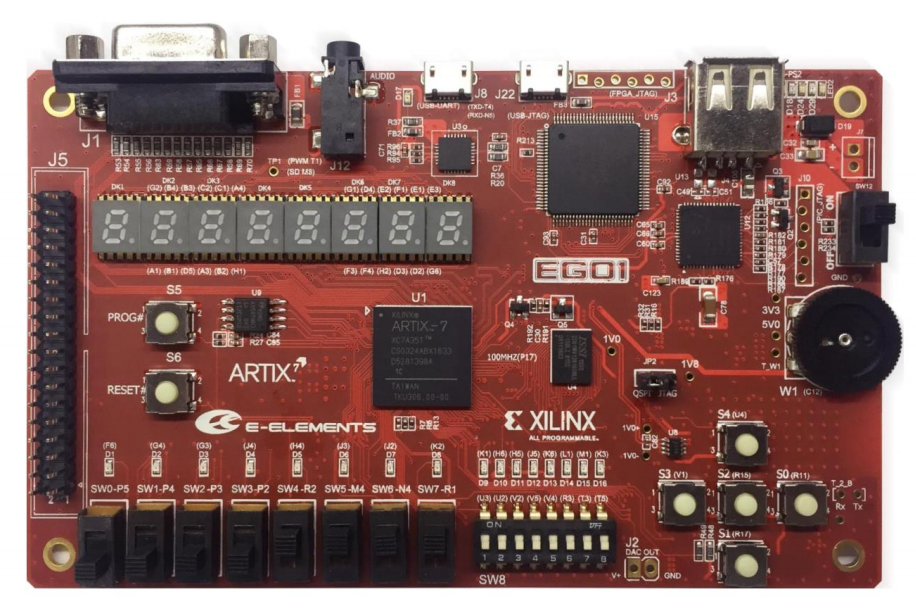

- 硬件平台:Ego1;

实现功能

实现密码锁应用的逻辑,包括输入密码时的 CALL 状态,

正确输入密码-HCC 状态,超时未正确输入密码 FAIL 状态,修改密码切换 MODE 等。

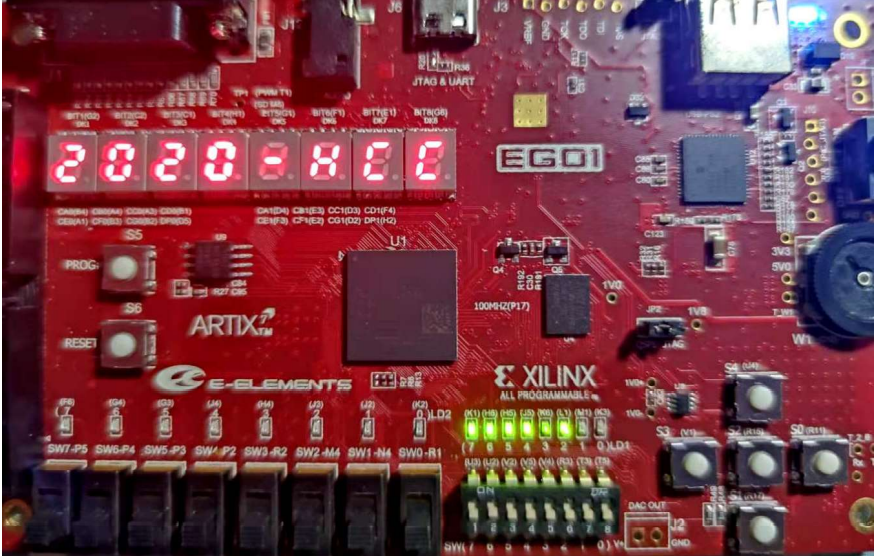

默认密码2020

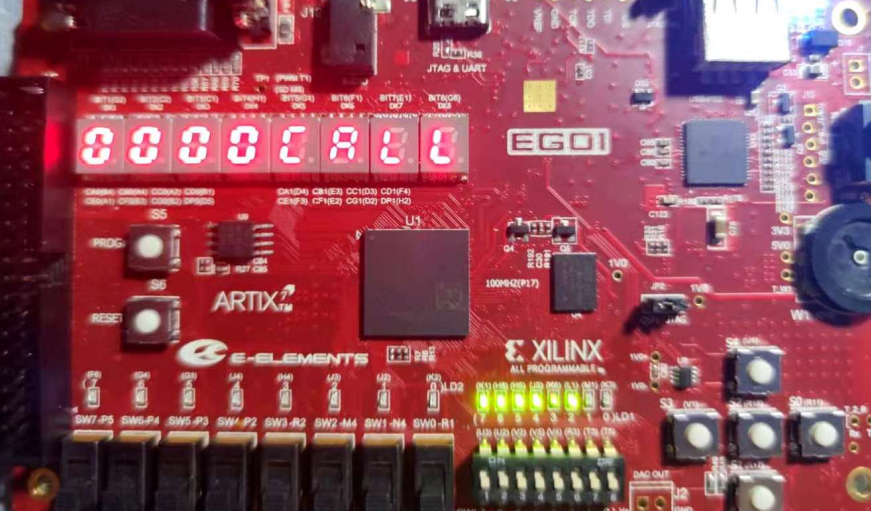

- 准备解锁时,显示 CALL 字符等待输入

- 输入密码,成功解锁

- 调节按钮 SW7(左下角按钮上拉,相应 LED 点亮,流水灯切换为间隔亮灯),

此时调节每位密码数值设置锁的密码

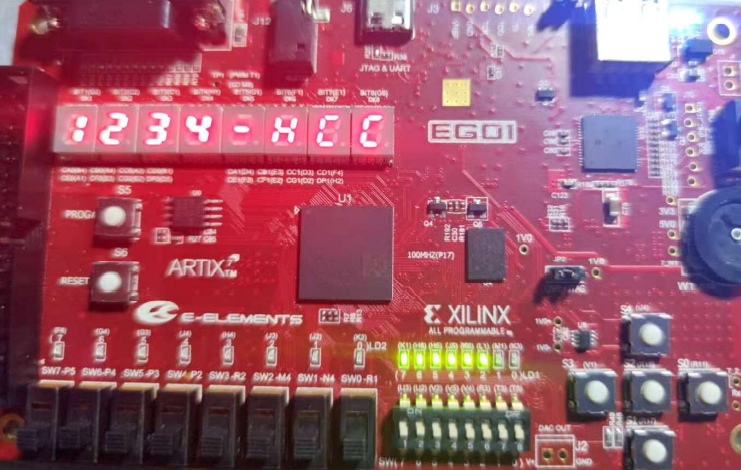

- 设置完后返回正常解锁模式测试,输入正确密码成功解锁,显示-HCC

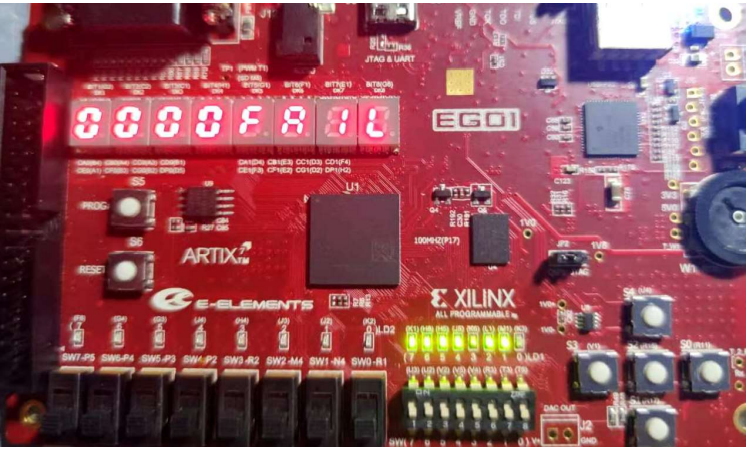

- 超过 20 秒未输入正确密码,密码锁将锁死,返回 FAIL

密码锁开锁倒计时采用流水灯式倒计时,倒计时完毕未成功解锁,密码锁将被锁死,显示 FAIL

密码锁状态分为待解锁,解锁超时失败和解锁成功三个状态,分别用字符

CALL,FAIL 和-HCC 三个字符在数码管上展示

本代码已在ego1开发板验证,ego1开发板如下,其他开发板可以修改管脚适配:

FPGA设计,借助Vivado和Ego1实验平台设计的密码锁

实验环境

- 操作系统:Window 10;

- 设计软件:Vivado 2017.4;

- 硬件平台:Ego1;

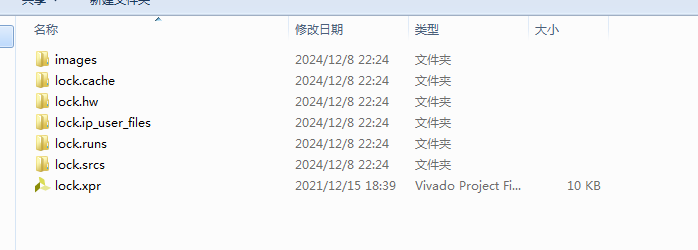

1、工程文件

2、程序文件

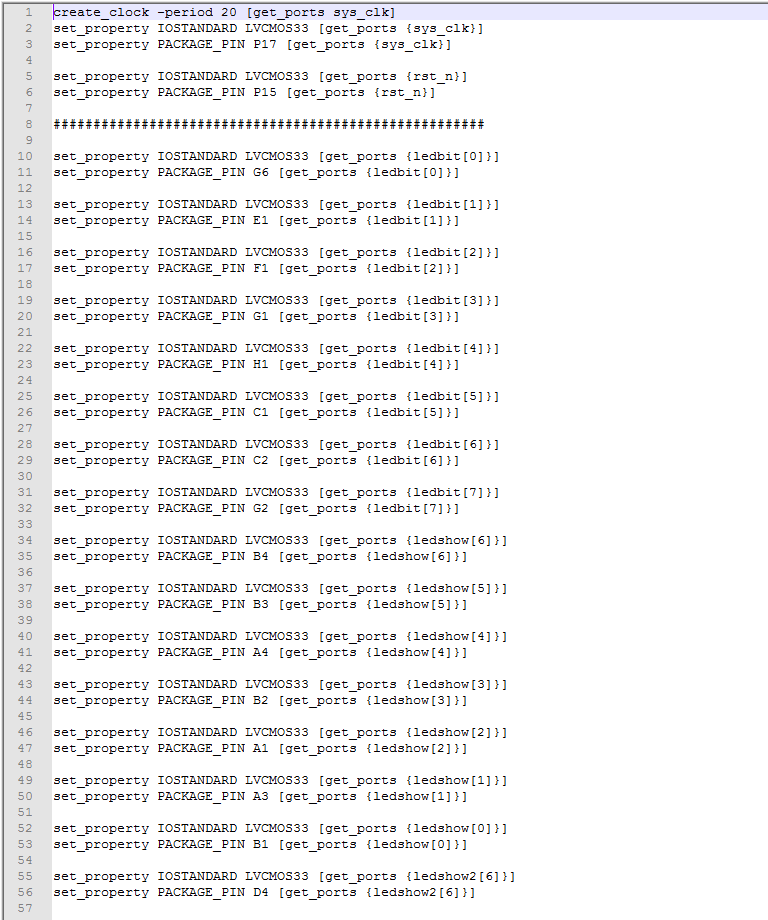

3、管脚约束文件

上板验证

- 准备解锁时,显示 CALL 字符等待输入

成功解锁

调节按钮 SW7(左下角按钮上拉,相应 LED 点亮,流水灯切换为间隔亮灯), 此时调节每位密码数值设置锁的密码

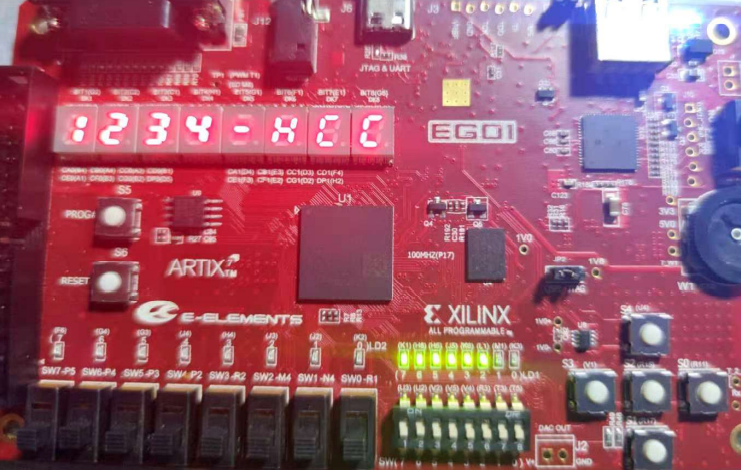

- 设置完后返回正常解锁模式测试,输入 1234 成功解锁,返回-HCC

- 超过 20 秒未输入正确密码,密码锁将锁死,返回 FAIL

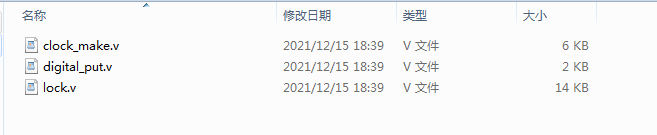

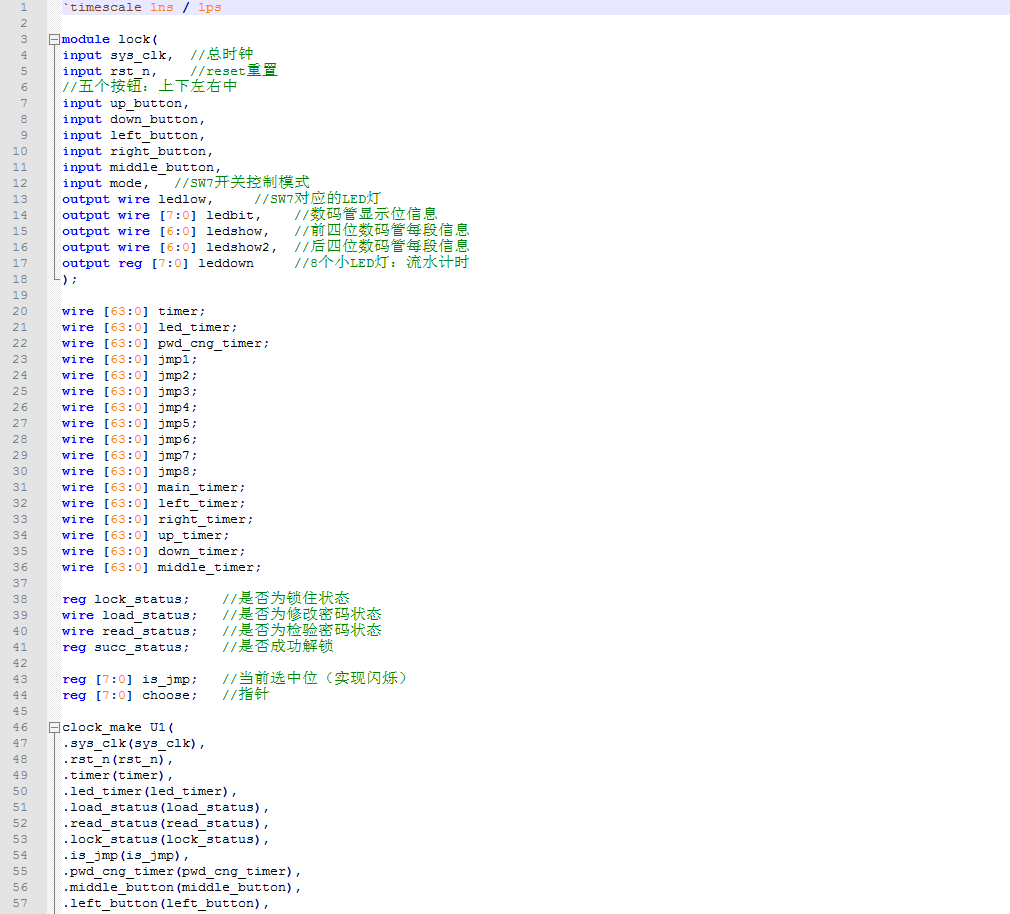

部分代码展示:

`timescale 1ns / 1ps module clock_make( input sys_clk, input rst_n, input [7:0] is_jmp, input left_button, input right_button, input up_button, input down_button, input middle_button, input lock_status, input read_status, input load_status, output reg [63:0] led_timer, output reg [63:0] pwd_cng_timer, output reg [63:0] jmp1, output reg [63:0] jmp2, output reg [63:0] jmp3, output reg [63:0] jmp4, output reg [63:0] jmp5, output reg [63:0] jmp6, output reg [63:0] jmp7, output reg [63:0] jmp8, output reg [63:0] timer, output reg [63:0] main_timer, output reg [63:0] right_timer, output reg [63:0] left_timer, output reg [63:0] up_timer, output reg [63:0] down_timer, output reg [63:0] middle_timer ); always@(posedge sys_clk or negedge rst_n) begin if(~rst_n) begin pwd_cng_timer <= 64'd0; end else begin if(pwd_cng_timer == 64'd99_999_999)pwd_cng_timer <= 0; else begin if(middle_button) begin pwd_cng_timer <= pwd_cng_timer + 1'b1; end else begin pwd_cng_timer <= 0; end end end end always@(posedge sys_clk or negedge rst_n) begin if(~rst_n) begin left_timer <= 64'd0; end else begin if(left_timer == 64'd9_999_999)left_timer <= 0; else begin if(left_button) begin left_timer <= left_timer + 1'b1; end else begin left_timer <= 0; end end end end always@(posedge sys_clk or negedge rst_n) begin if(~rst_n) begin right_timer <= 64'd0; end else begin if(right_timer == 64'd9_999_999)right_timer <= 0; else begin if(right_button) begin right_timer <= right_timer + 1'b1; end else begin right_timer <= 0; end end end end always@(posedge sys_clk or negedge rst_n) begin if(~rst_n) begin up_timer <= 64'd0; end else begin if(up_timer == 64'd9_999_999)up_timer <= 0; else begin if(up_button) begin up_timer <= up_timer + 1'b1; end

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?