名称:贪食蛇VGA游戏设计VHDL代码VIVADO basys3开发板(文末获取)

软件:VIVADO

语言:VHDL

代码功能:贪食蛇VGA游戏设计

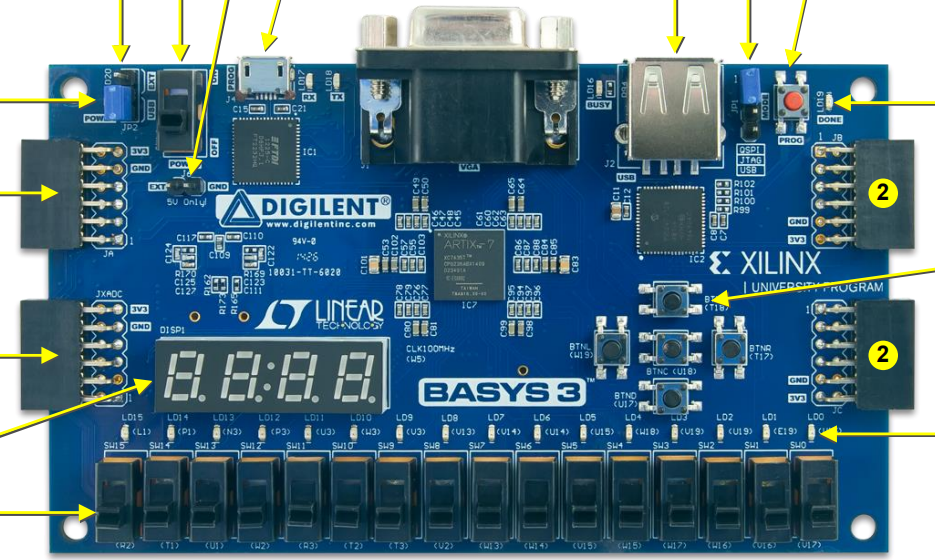

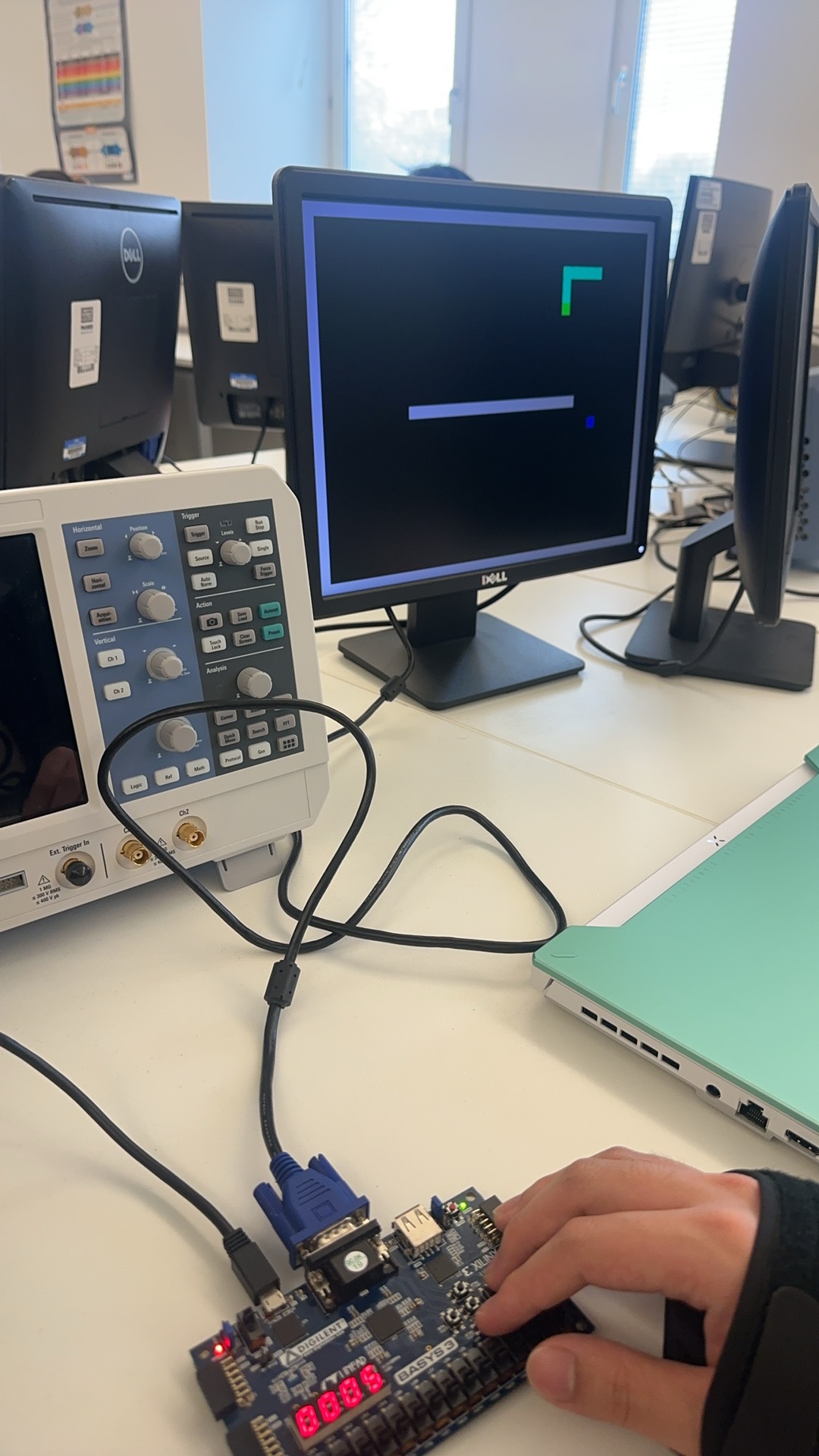

本代码已在basys3开发板验证,basys3开发板如下,其他开发板可以修改管脚适配:

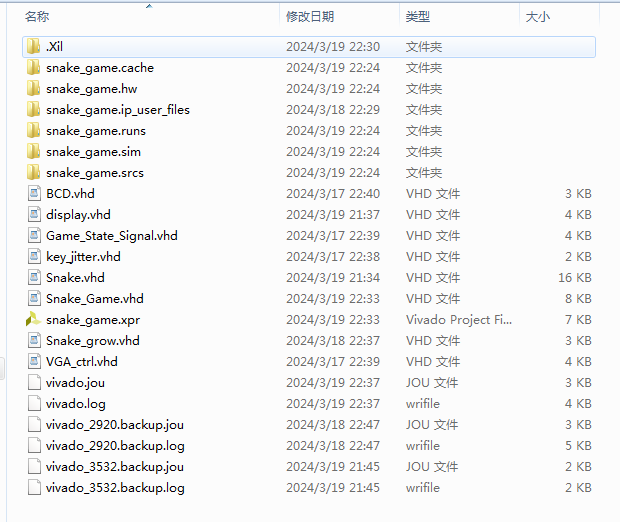

1、工程文件

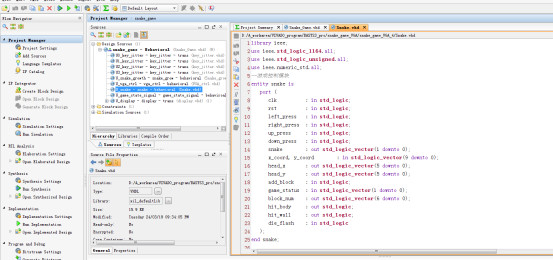

2、程序文件

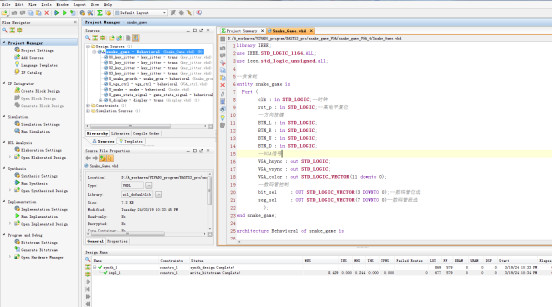

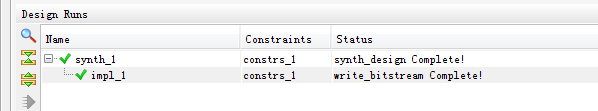

3、程序编译

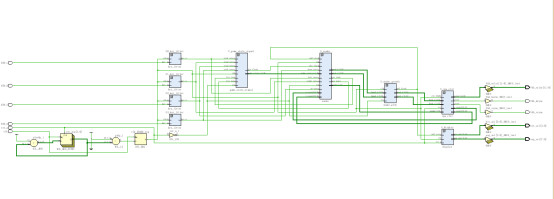

4、RTL图

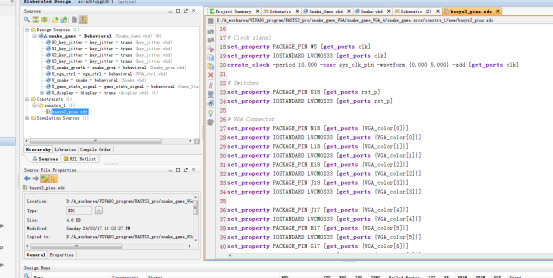

5、管脚分配

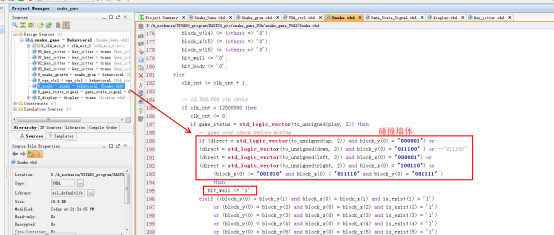

6、关键代码说明

上板演示效果

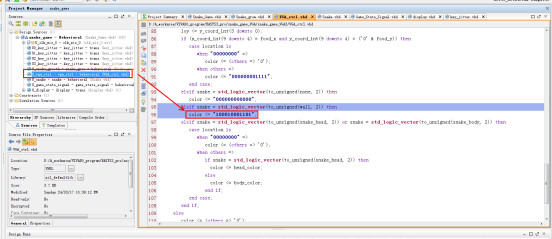

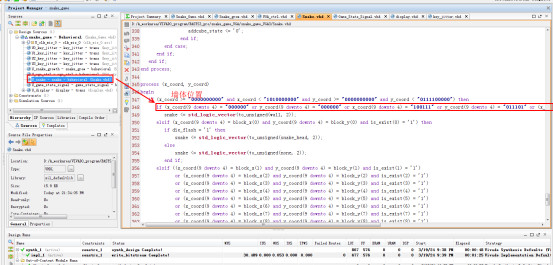

部分代码展示:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.numeric_std.all; --VGA控制模块 entity vga_ctrl is port ( clk_25mHz : in std_logic; rst : in std_logic; snake : in std_logic_vector(1 downto 0); food_x : in std_logic_vector(5 downto 0); food_y : in std_logic_vector(4 downto 0); x_coord, y_coord : out std_logic_vector(9 downto 0); hsync, vsync : out std_logic; color : out std_logic_vector(11 downto 0) ); end vga_ctrl; architecture behavioral of vga_ctrl is constant none : integer := 0; constant snake_head : integer := 1; constant snake_body : integer := 2; constant wall : integer := 3; constant head_color : std_logic_vector(11 downto 0) := "000011110000"; constant body_color : std_logic_vector(11 downto 0) := "000011111111"; signal clk_cnt : std_logic_vector(19 downto 0); signal line_cnt : std_logic_vector(9 downto 0); signal lox : std_logic_vector(3 downto 0); signal loy : std_logic_vector(3 downto 0); signal location : std_logic_vector(7 downto 0); -- declare intermediate signals for referenced outputs signal x_coord_int : std_logic_vector(19 downto 0); signal y_coord_int : std_logic_vector(19 downto 0); begin -- drive referenced outputs x_coord <= x_coord_int(9 downto 0); y_coord <= y_coord_int(9 downto 0); location <= loy & lox; process (clk_25mHz, rst) begin if rst = '1' then clk_cnt '0'); hsync <= '1'; line_cnt '0'); vsync <= '1'; elsif rising_edge(clk_25mHz) then x_coord_int <= clk_cnt - std_logic_vector(to_unsigned(144, 20)); y_coord_int <= line_cnt - std_logic_vector(to_unsigned(33, 20)); if clk_cnt = 0 then hsync <= '0'; clk_cnt <= clk_cnt + 1; elsif clk_cnt = std_logic_vector(to_unsigned(96, 20)) then hsync <= '1'; clk_cnt <= clk_cnt + 1; elsif clk_cnt = std_logic_vector(to_unsigned(799, 20)) then line_cnt <= line_cnt + 1; clk_cnt '0'); else clk_cnt <= clk_cnt + 1; end if;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?