名称:羽毛球记分牌设计VHDL代码VIVADO仿真(文末获取)

软件:VIVADO

语言:VHDL

代码功能:

羽毛球记分牌

为羽毛球比赛设计一个记分牌,记录双方球员的得分,每当一名球员得分时进行加分。只要有一名玩家得21分,游戏就结束。

谁赢得了游戏,对于玩家1和玩家2使用不同led显示。赢得游戏后,计分板应在5秒后复位,除非在此时间之前发出单独的复位信号。

在比赛中,分数可以是

以五种方式评分:

Try — 5 分

Penalty Try — 5 分

Goal-Kick (try-conversion) — 2 分

Field-Goal (drop kick) — 3 分

Penalty goal — 3 分

1. 工程文件

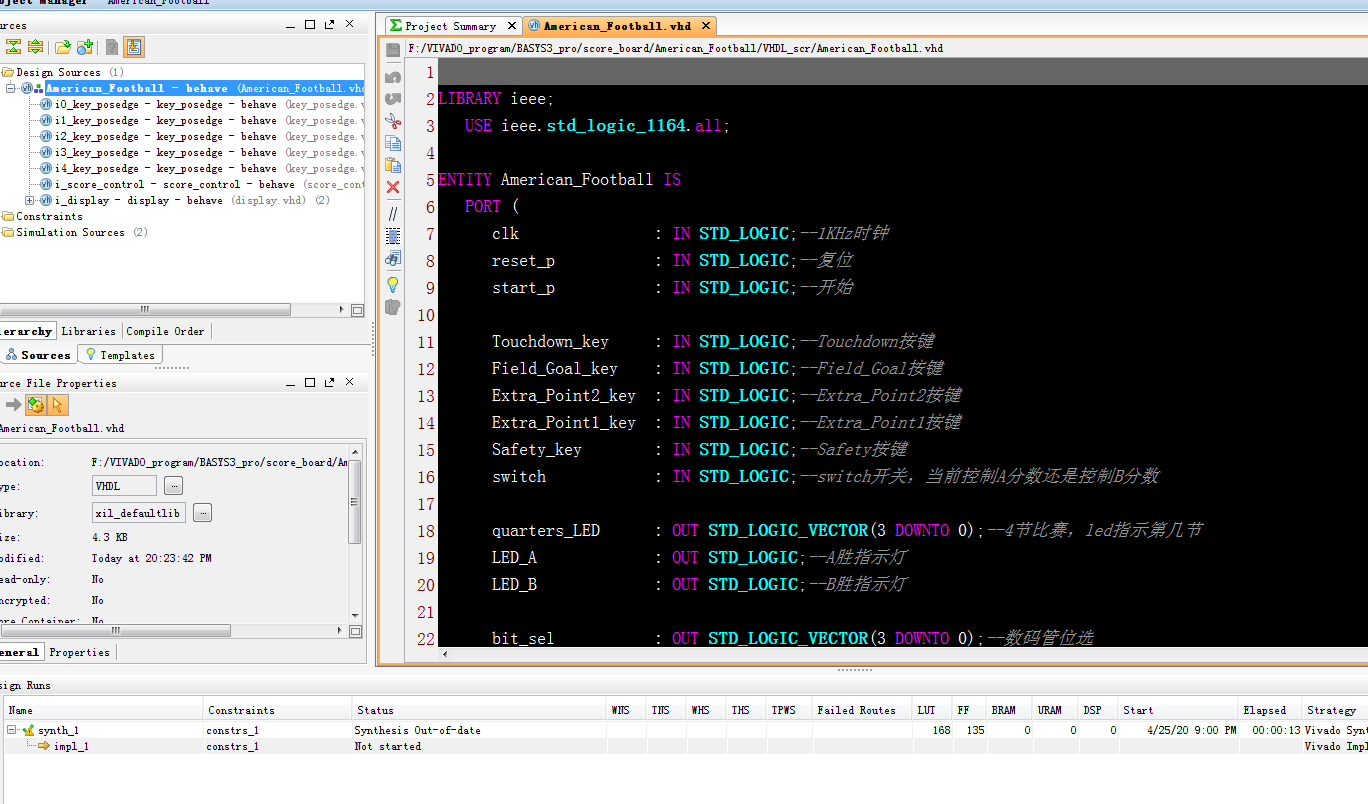

2. 程序文件

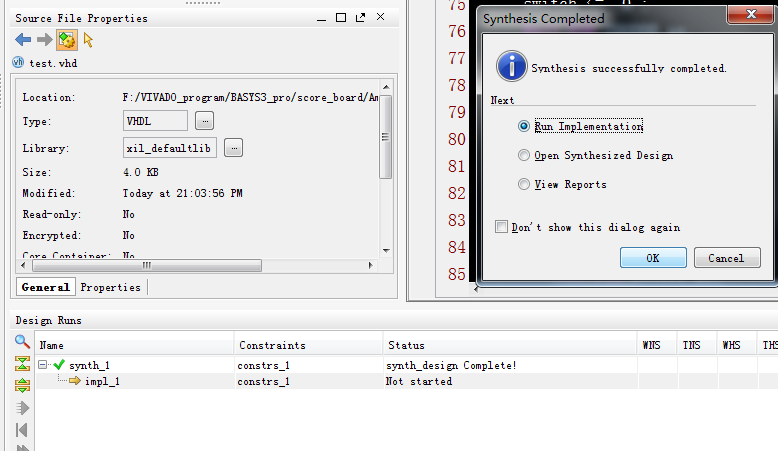

3. 程序编译

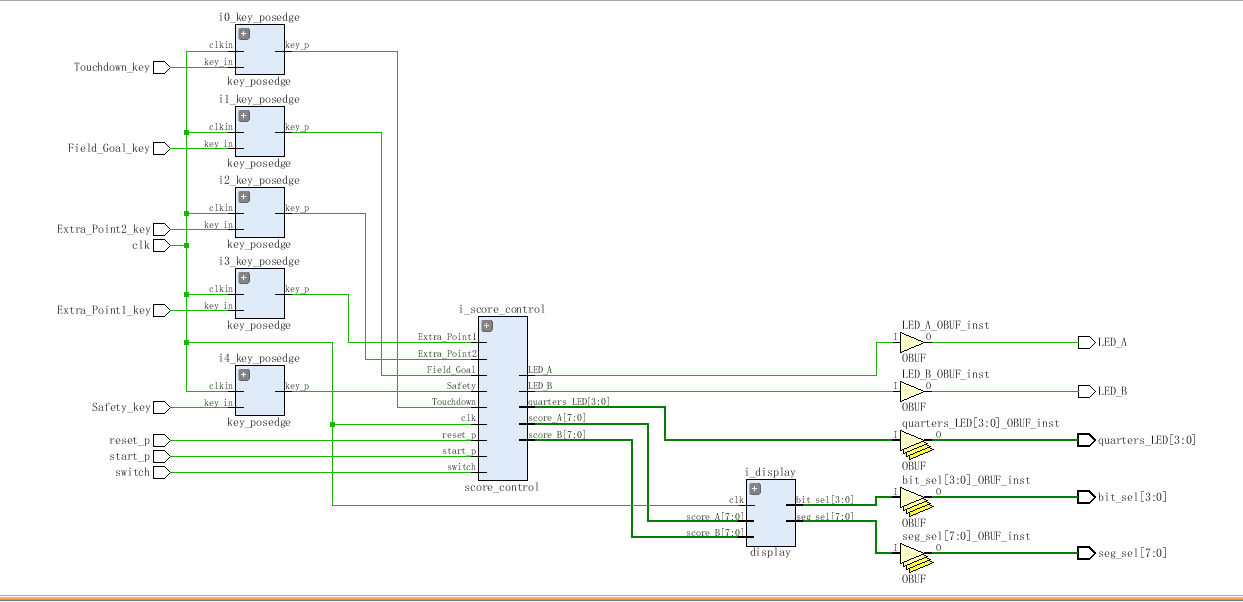

4. RTL图

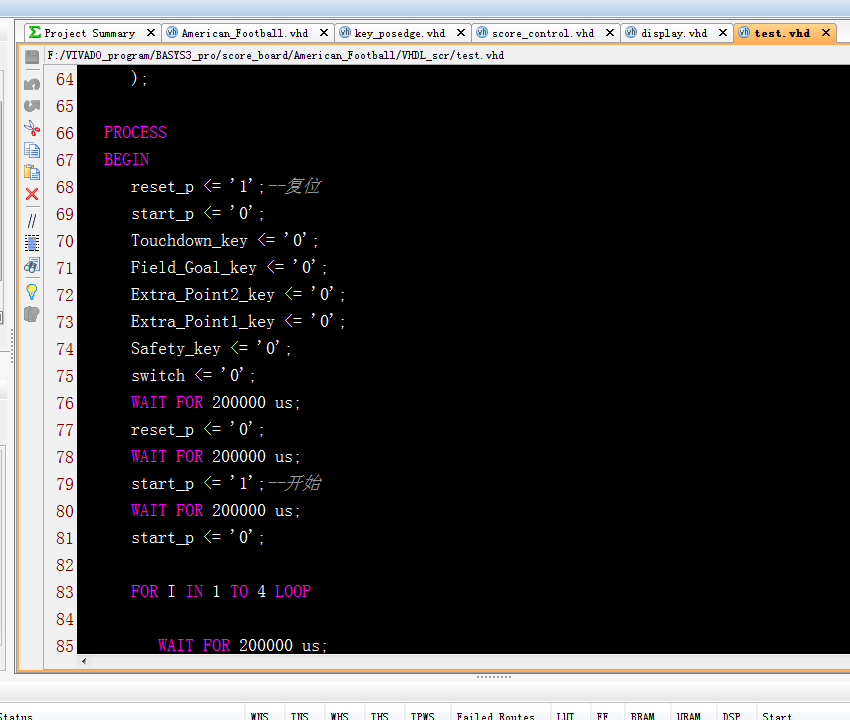

5. Testbench

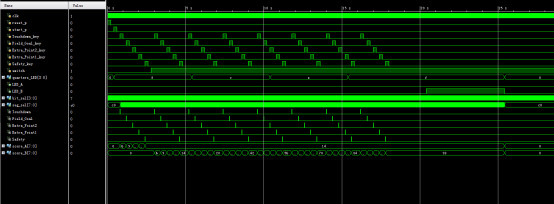

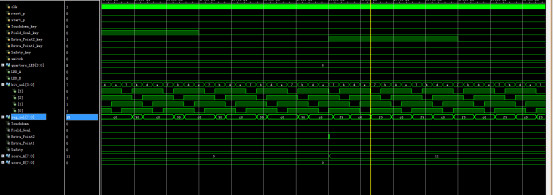

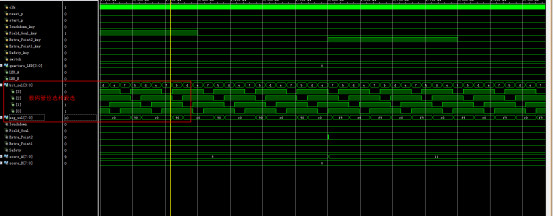

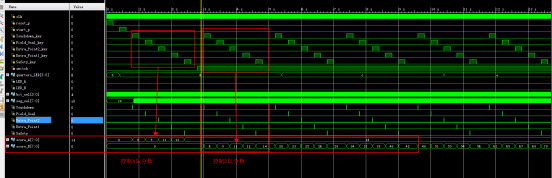

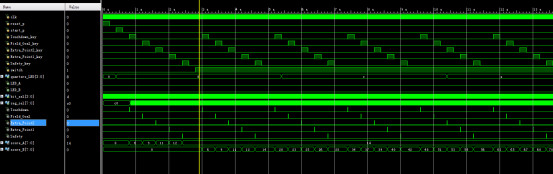

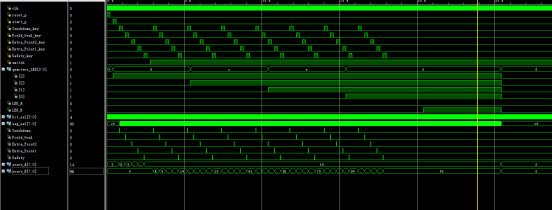

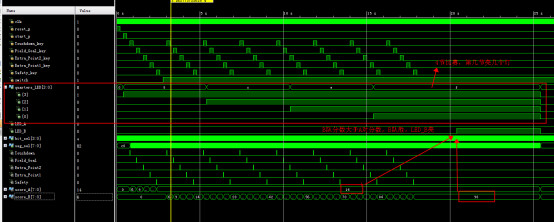

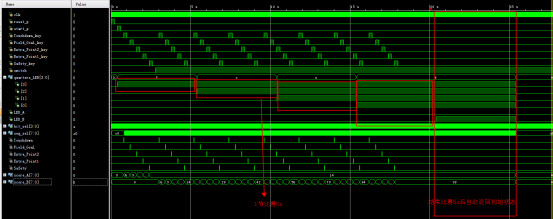

6. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --显示模块 ENTITY display IS PORT ( clk : IN STD_LOGIC; score_A : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--A队得分 score_B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--B队得分 bit_sel : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 seg_sel : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END display; ARCHITECTURE behave OF display IS component BCD IS PORT ( clk : IN STD_LOGIC; binary : IN STD_LOGIC_VECTOR(7 DOWNTO 0); Tens : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); Ones : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END component; SIGNAL score_A_ten : STD_LOGIC_VECTOR(3 DOWNTO 0);--分数十位 SIGNAL score_A_one : STD_LOGIC_VECTOR(3 DOWNTO 0);--分数个位 SIGNAL score_B_ten : STD_LOGIC_VECTOR(3 DOWNTO 0);--分数十位 SIGNAL score_B_one : STD_LOGIC_VECTOR(3 DOWNTO 0);--分数个位 SIGNAL display_num : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL select_bit : STD_LOGIC_VECTOR(15 DOWNTO 0) := "0000000000000000"; SIGNAL geshu : STD_LOGIC_VECTOR(2 DOWNTO 0) := "000"; BEGIN

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?