名称:基于FPGA的加减乘除计算器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

加减乘除计算器设计

模拟实际的计算器输入过程

具有ESC、加减乘除、enter按键

具有0~9数字按键

1. 工程文件

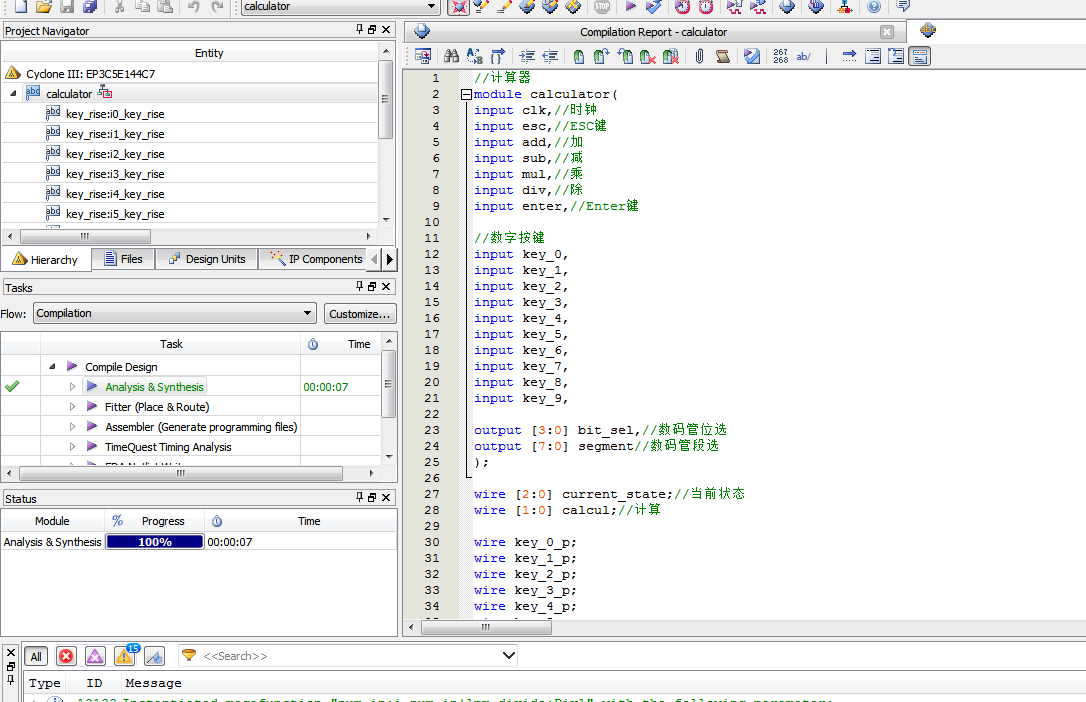

2. 程序文件

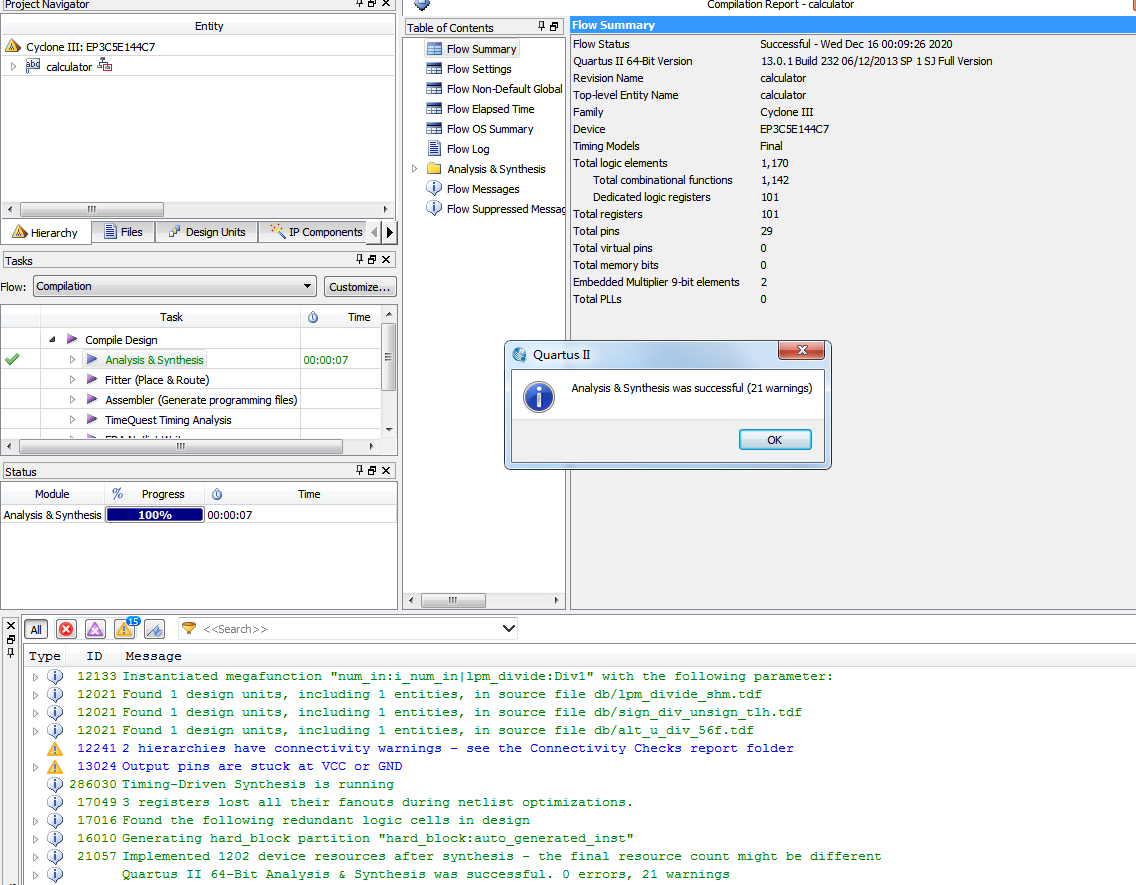

3. 程序编译

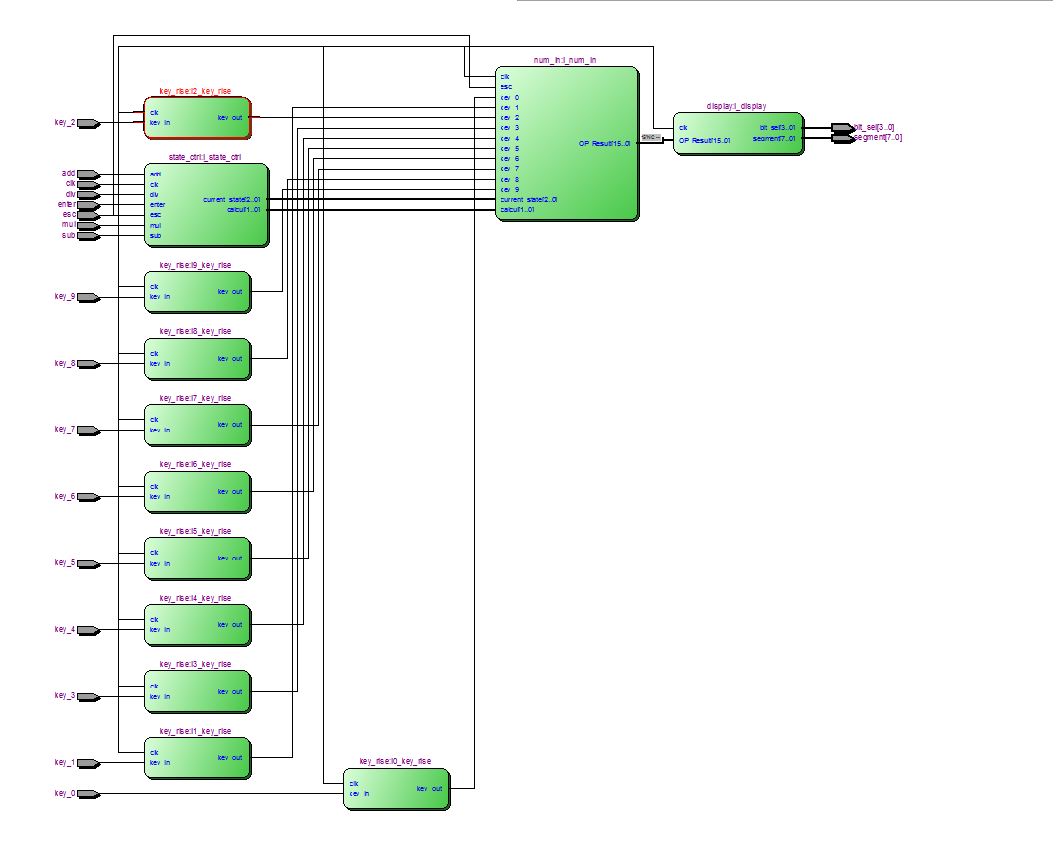

4. RTL图

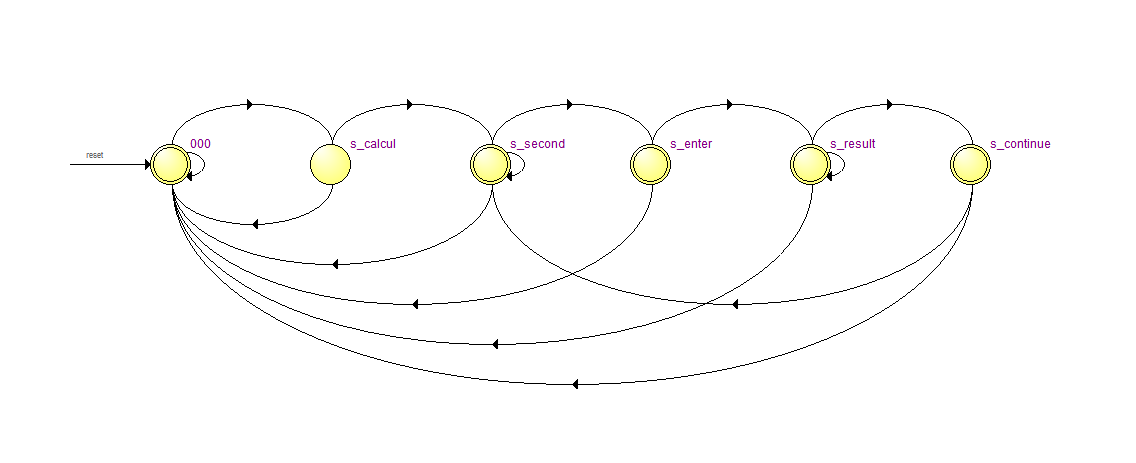

5. 状态图

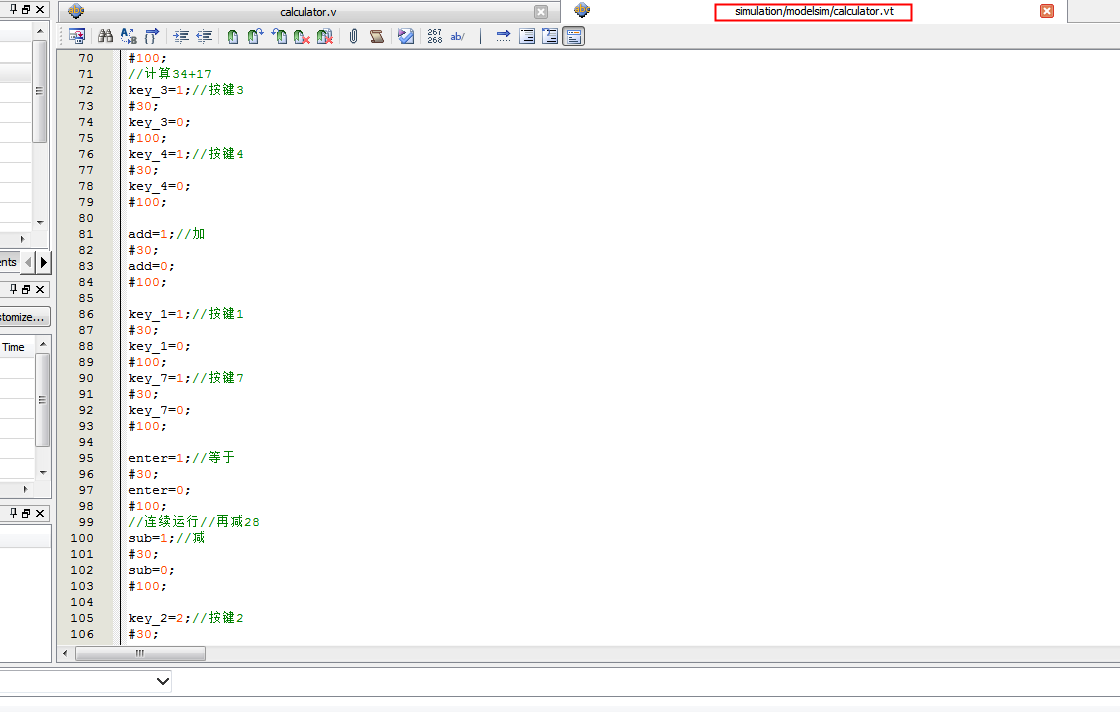

6. 仿真文件

7. 仿真图

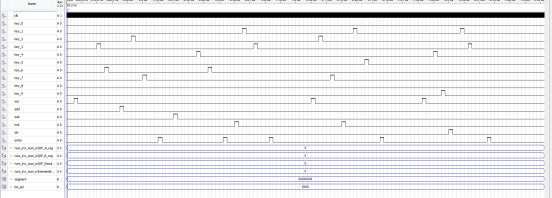

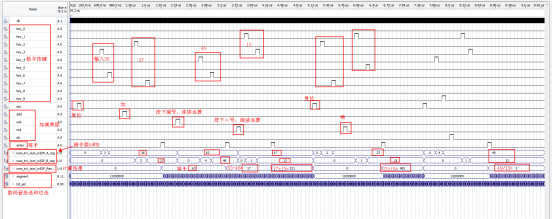

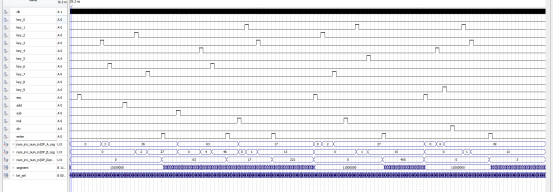

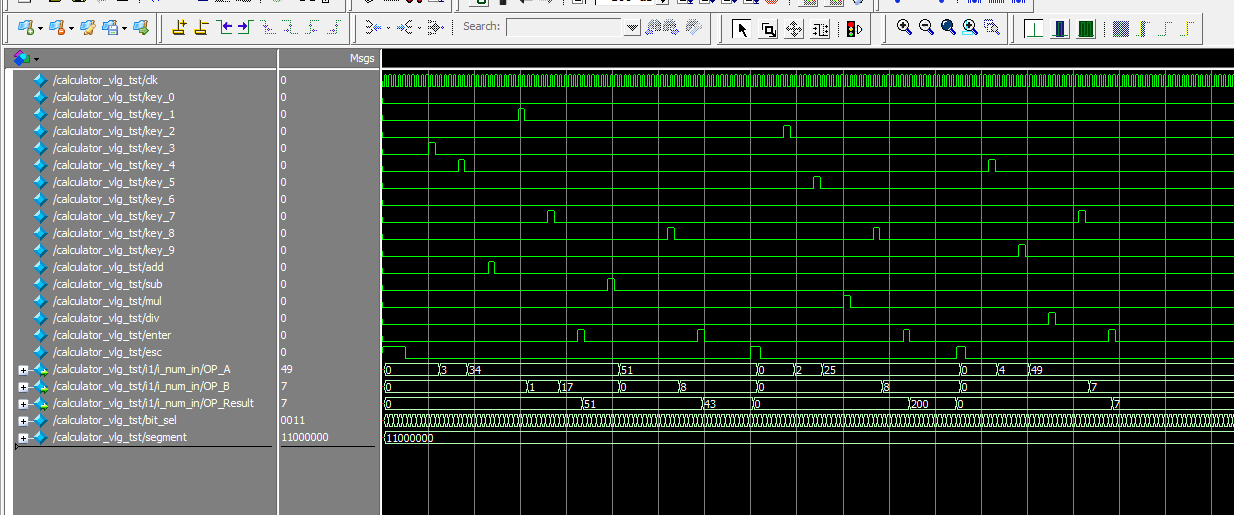

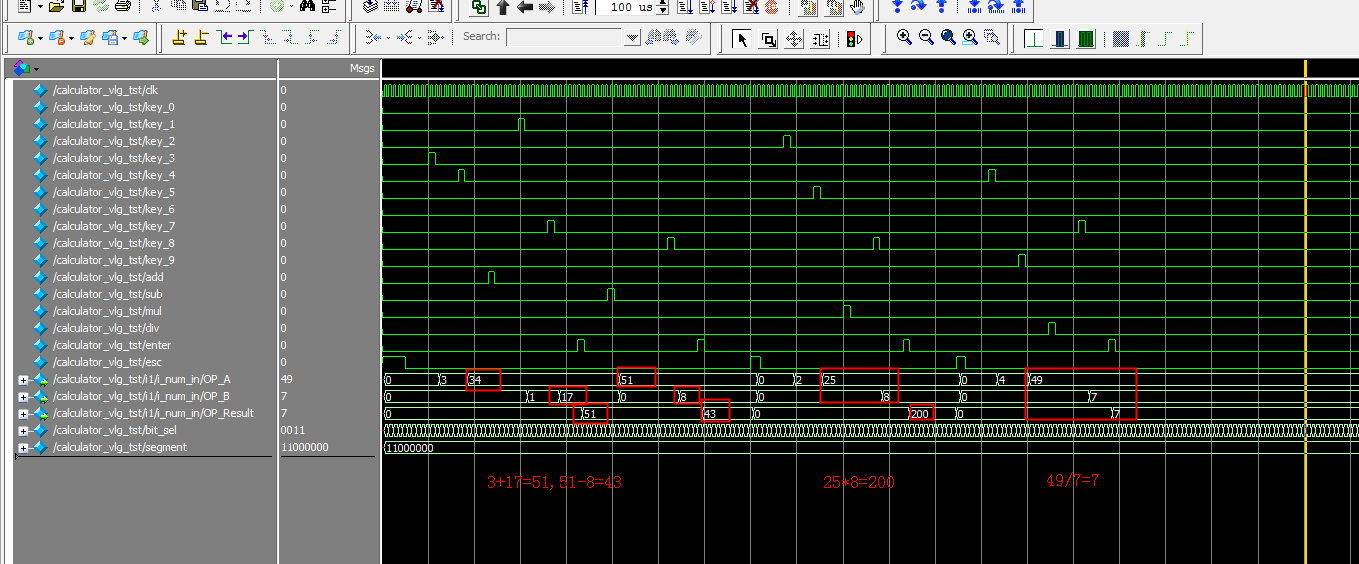

Modulesim仿真

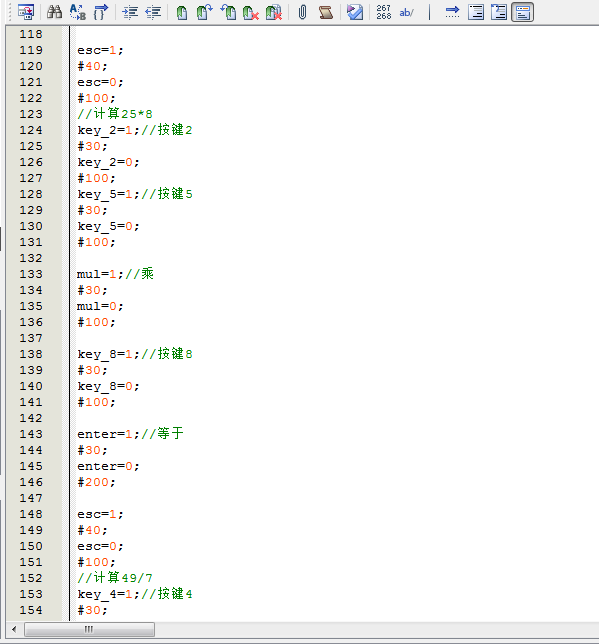

Testbench

仿真图

部分代码展示:

//计算器 module calculator( input clk,//时钟 input esc,//ESC键 input add,//加 input sub,//减 input mul,//乘 input div,//除 input enter,//Enter键 //数字按键 input key_0, input key_1, input key_2, input key_3, input key_4, input key_5, input key_6, input key_7, input key_8, input key_9, output [3:0] bit_sel,//数码管位选 output [7:0] segment//数码管段选 ); wire [2:0] current_state;//当前状态 wire [1:0] calcul;//计算 wire key_0_p; wire key_1_p; wire key_2_p; wire key_3_p; wire key_4_p; wire key_5_p; wire key_6_p; wire key_7_p; wire key_8_p; wire key_9_p; //按键上升沿模块 key_rise i0_key_rise( . clk(clk),//时钟 . key_in(key_0),//按键输入 . key_out(key_0_p)//按键上升沿 ); //按键上升沿模块 key_rise i1_key_rise( . clk(clk),//时钟 . key_in(key_1),//按键输入 . key_out(key_1_p)//按键上升沿 ); //按键上升沿模块 key_rise i2_key_rise( . clk(clk),//时钟 . key_in(key_2),//按键输入 . key_out(key_2_p)//按键上升沿 ); //按键上升沿模块 key_rise i3_key_rise( . clk(clk),//时钟 . key_in(key_3),//按键输入 . key_out(key_3_p)//按键上升沿 );

源代码

扫描文章末尾的公众号二维码

1697

1697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?