名称:基于FPGA的并串转换控制模块Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

并串转换控制模块

输入4bit并进数据,串行输出

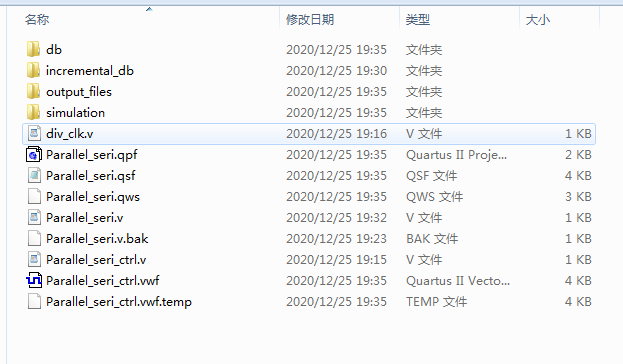

1. 工程文件

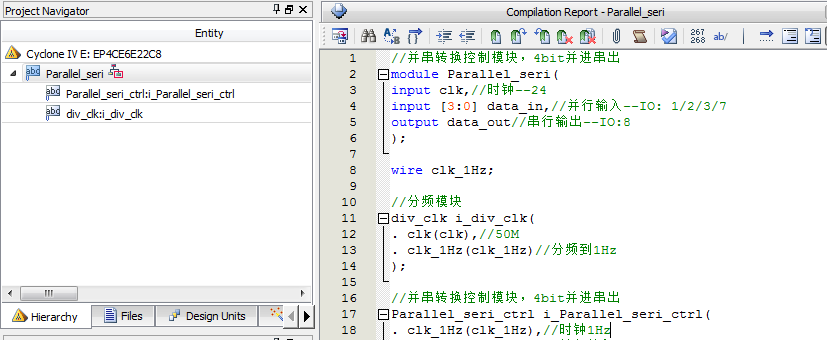

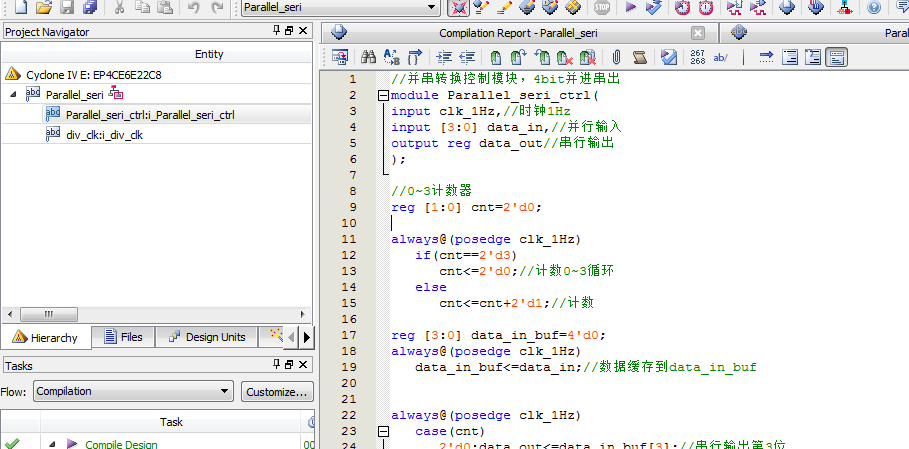

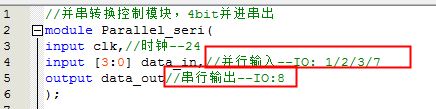

2. 程序文件

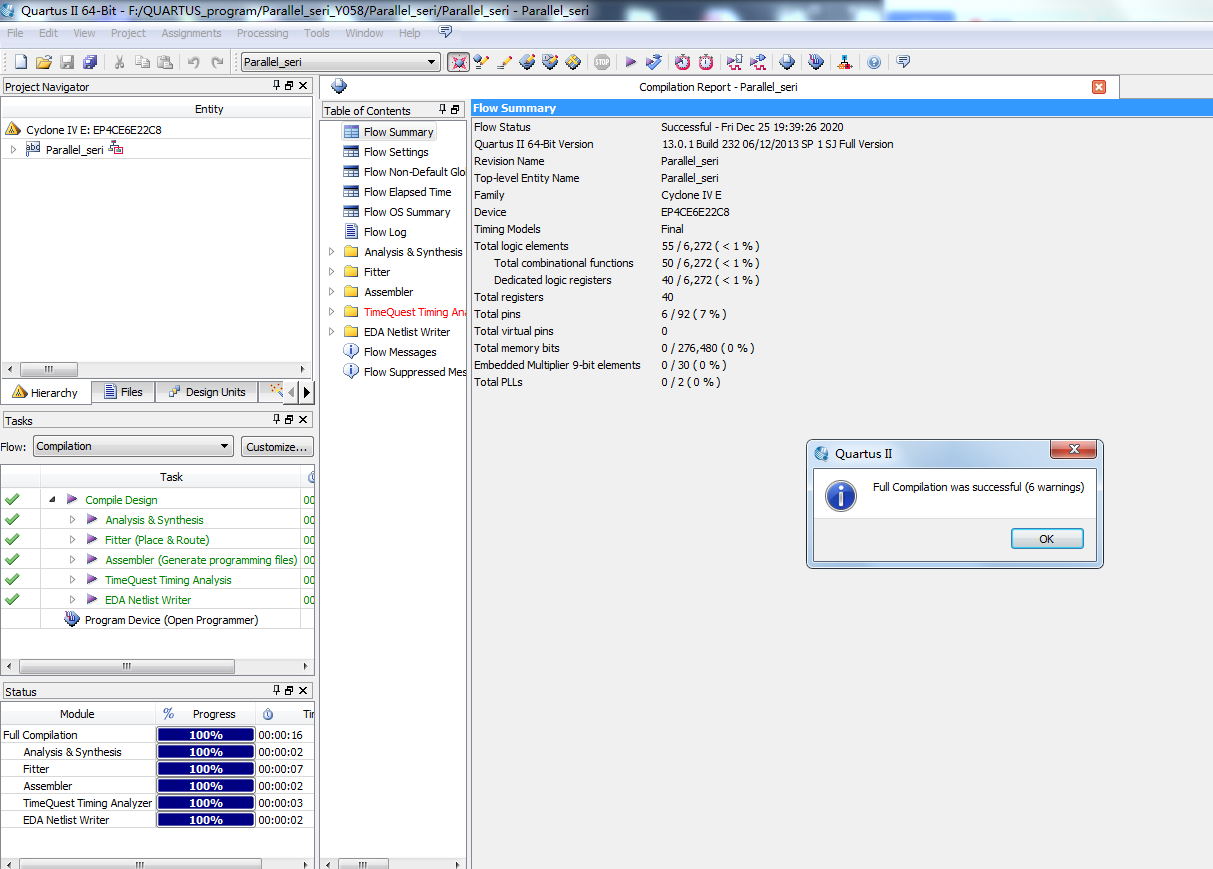

3. 程序编译

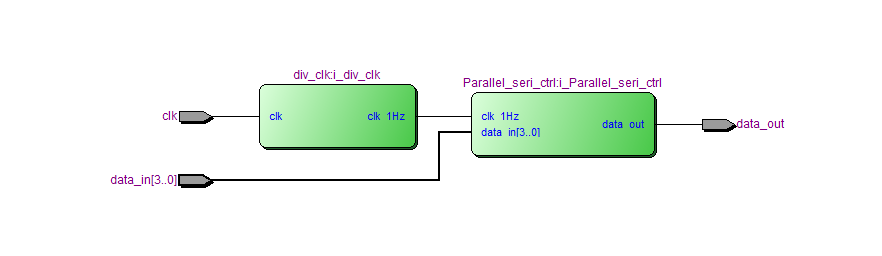

4. RTL图

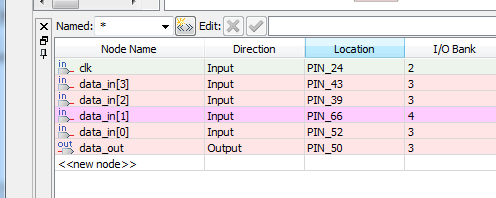

5. 管脚分配

6. Vwf文件

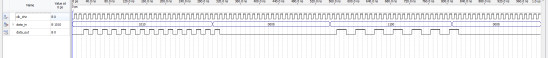

7. 仿真图

部分代码展示:

//并串转换控制模块,4bit并进串出 module Parallel_seri( input clk,//时钟--24 input [3:0] data_in,//并行输入--IO: 1/2/3/7 output data_out//串行输出--IO:8 ); wire clk_1Hz; //分频模块 div_clk i_div_clk( . clk(clk),//50M . clk_1Hz(clk_1Hz)//分频到1Hz ); //并串转换控制模块,4bit并进串出 Parallel_seri_ctrl i_Parallel_seri_ctrl( . clk_1Hz(clk_1Hz),//时钟1Hz . data_in(data_in),//并行输入 . data_out(data_out)//串行输出 ); endmodule

源代码

扫描文章末尾的公众号二维码

本文详细介绍了使用Verilog语言在Quartus平台上实现的4bit并串转换控制模块的代码,包括模块结构、输入输出信号、分频电路以及管脚分配,还展示了关键部分的代码和模拟仿真结果。

本文详细介绍了使用Verilog语言在Quartus平台上实现的4bit并串转换控制模块的代码,包括模块结构、输入输出信号、分频电路以及管脚分配,还展示了关键部分的代码和模拟仿真结果。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?