名称:秒表计时器Verilog代码Quartus 小脚丫开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基本要求:设计0.0秒至9.9秒(小数点需显示)的秒表计时器,计时精度为0.1秒,具备复位清零和暂停功能。

一个可以计时9.9秒的计时器实际上就是一个99进制的计数器,它意味着两个数码管需要以循环的方式将0.0,

0.1.9.9等数字依次显示,且间隔时间为0.1秒,如下图所示。

扩展要求:(1)计时到9.9秒时,秒表自动暂停,并在数码管上显示9.9。

(2)自行设计的其他功能,如发光二极管闪烁、可通过按键设定暂停时间等。

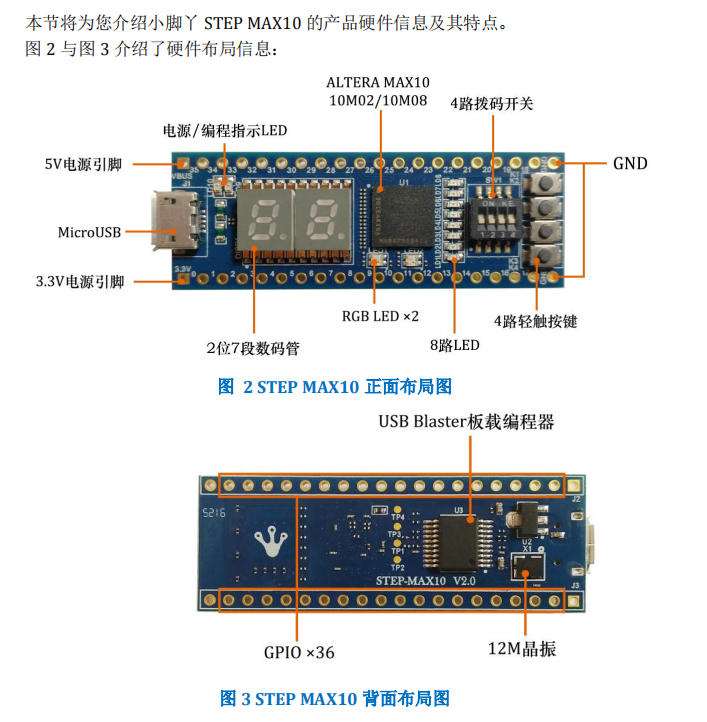

本代码已在小脚丫开发板验证,小脚丫开发板如下,其他开发板可以修改管脚适配:

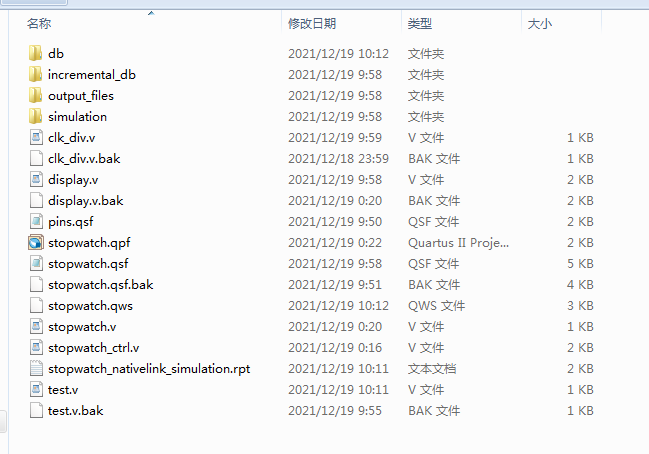

1. 工程文件

2. 程序文件

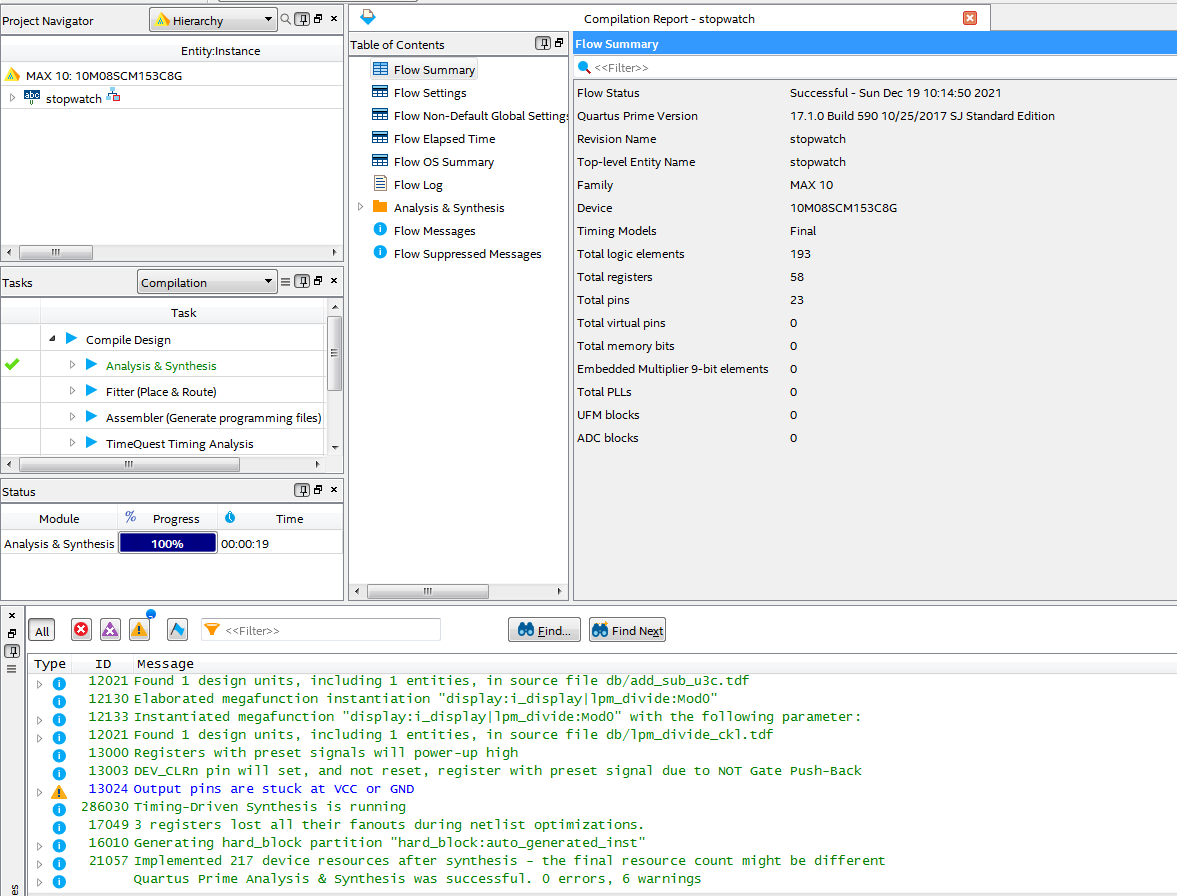

3. 程序编译

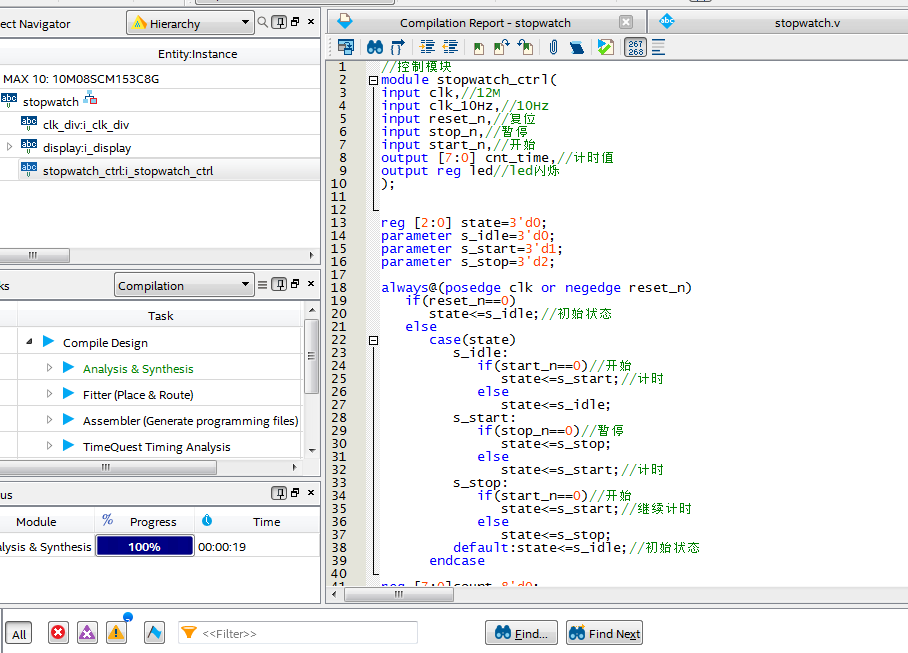

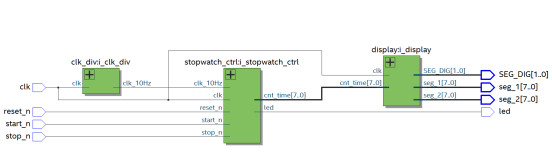

4. RTL图

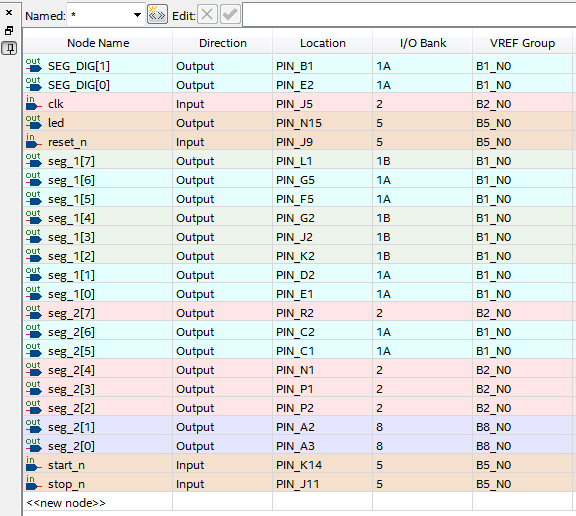

5. 管脚分配

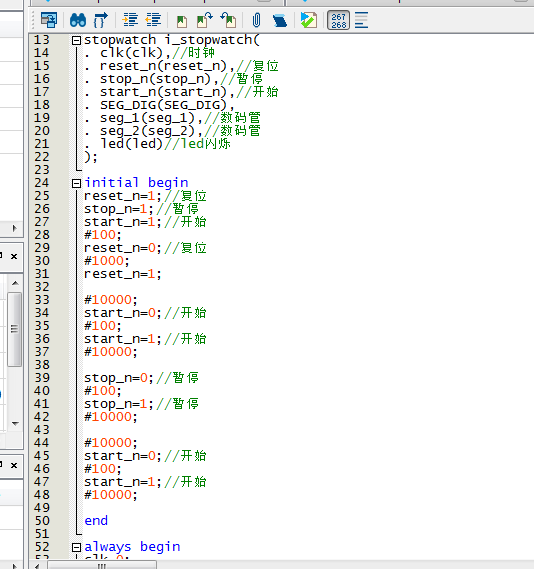

6. Testbench

7. 仿真图

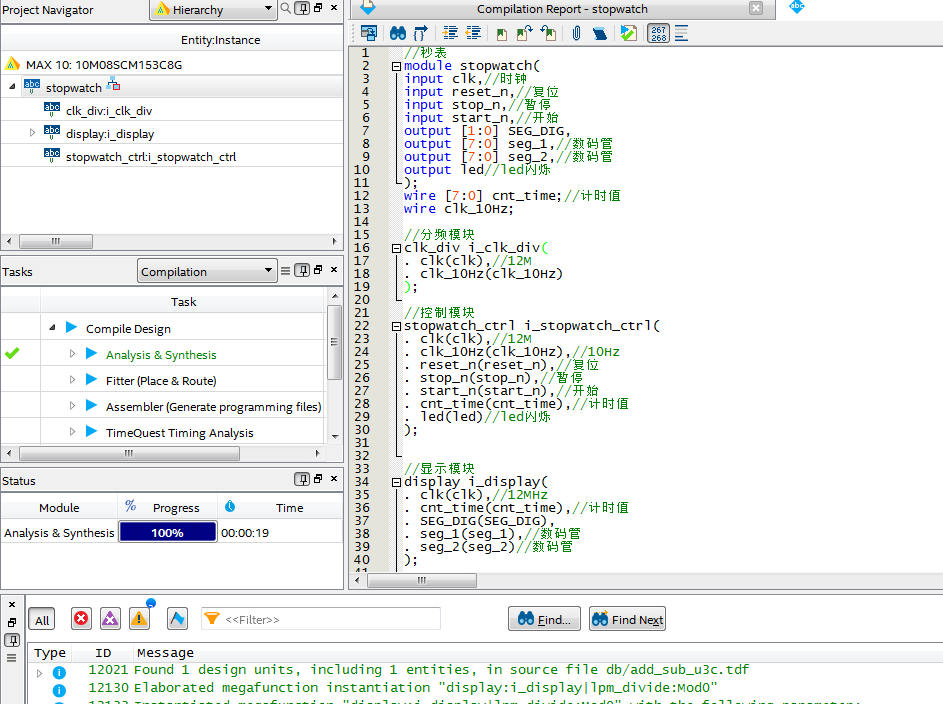

部分代码展示:

//秒表 module stopwatch( input clk,//时钟 input reset_n,//复位 input stop_n,//暂停 input start_n,//开始 output [1:0] SEG_DIG, output [7:0] seg_1,//数码管 output [7:0] seg_2,//数码管 output led//led闪烁 ); wire [7:0] cnt_time;//计时值 wire clk_10Hz; //分频模块 clk_div i_clk_div( . clk(clk),//12M . clk_10Hz(clk_10Hz) ); //控制模块 stopwatch_ctrl i_stopwatch_ctrl( . clk(clk),//12M . clk_10Hz(clk_10Hz),//10Hz . reset_n(reset_n),//复位 . stop_n(stop_n),//暂停 . start_n(start_n),//开始 . cnt_time(cnt_time),//计时值 . led(led)//led闪烁 ); //显示模块 display i_display( . clk(clk),//12MHz . cnt_time(cnt_time),//计时值 . SEG_DIG(SEG_DIG), . seg_1(seg_1),//数码管 . seg_2(seg_2)//数码管 ); endmodule

完整代码

扫描文章末尾的公众号二维码

本文介绍了如何使用Verilog语言在Quartus环境下设计一个0.1秒精度的秒表计时器,具备复位、暂停和9.9秒自动暂停功能。代码展示了秒表模块、分频控制、显示模块及LED管理,适用于小脚丫开发板,可根据其他开发板调整管脚。

本文介绍了如何使用Verilog语言在Quartus环境下设计一个0.1秒精度的秒表计时器,具备复位、暂停和9.9秒自动暂停功能。代码展示了秒表模块、分频控制、显示模块及LED管理,适用于小脚丫开发板,可根据其他开发板调整管脚。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?