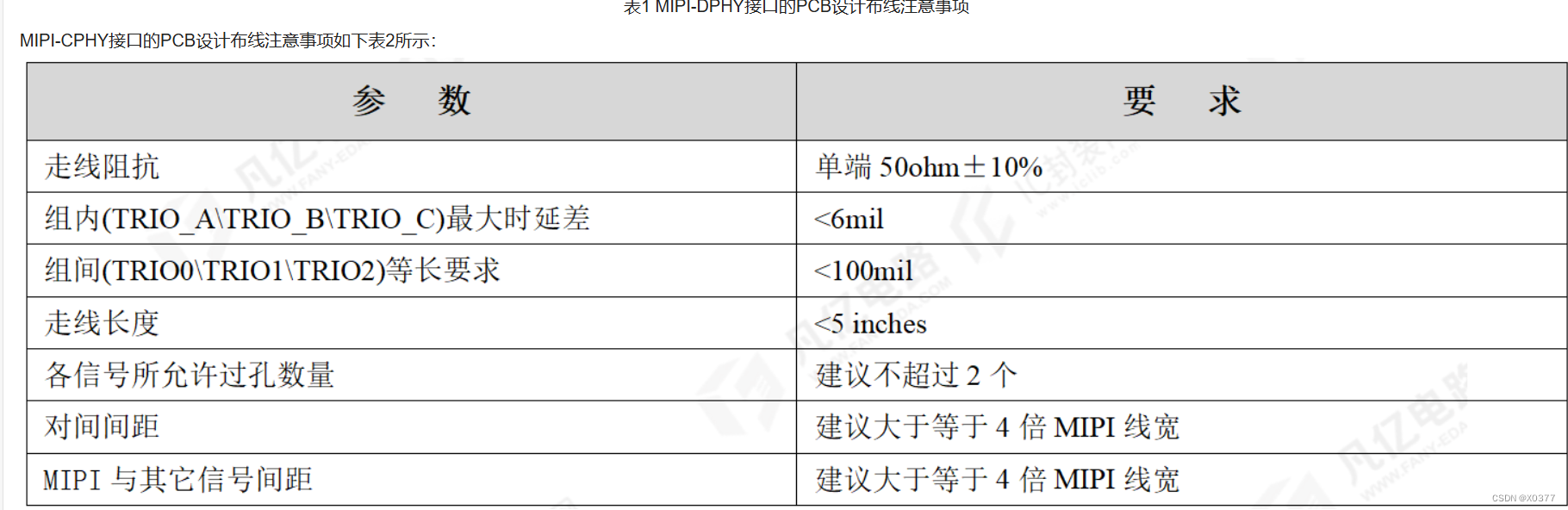

CPHY PCB设计,MIPI走线约束

- 阻抗50,等长。

DPHY基本知识

DPHY布局布线

1,100欧姆匹配。如果使用LP单端信号,建议松耦合。

- 建议使用背钻,如果有过孔。

- CLK与数据等长控制±50mil。

- 对内3H,对外5h。

- 原理干扰信号,或者电源。

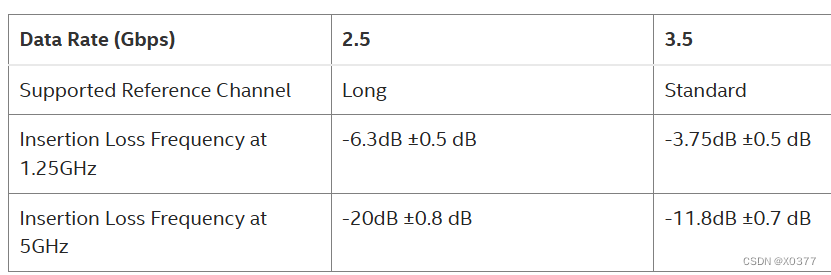

| Parameter | Specification |

| Trace type | Stripline |

| Differential impedance | 95±10% W |

| Trace length | |

| Spacing in pair | 2X trace width |

| Spacing to other MIPI pairs | 5X trace width |

| Spacing to other non-MIPI pairs | 6X trace width |

| Skew between P/N per pair | ±2 ps |

| Skew between clock and data | ±8 ps |

| Skew between data and data | ±8 ps |

| Termination at receiver | 100Wdifferential(3) |

| Notes: 1.For distances greater than 4 inches, receiver equalization must be used (CTLE). It is strongly recommended that the PCB (data-to-data and data-to-clock) be deskewed even if the deskew feature in the IP is used. 2.A reference stackup used for the longer trace lengths (4 to 10 inches) can be provided upon request. Operation at 2.5 Gb/s is supported as long as the channel loss is kept under 9 dB. | |

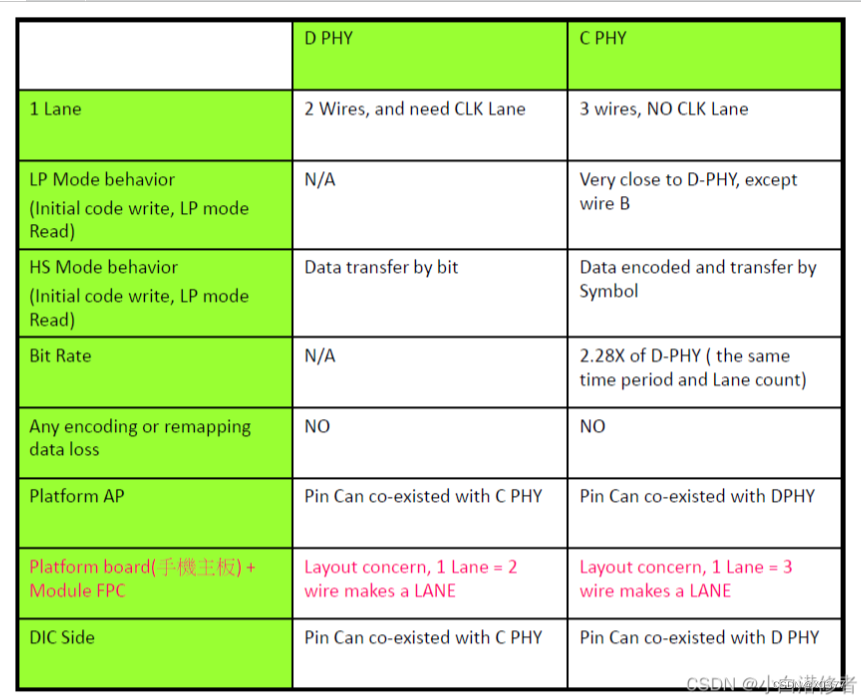

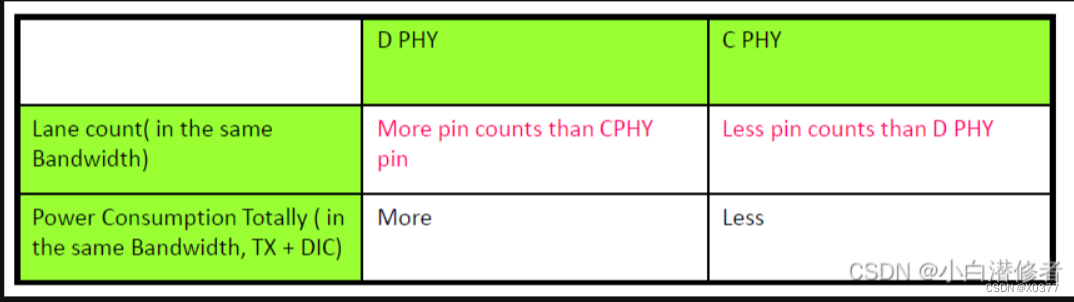

CPHY DPHY区别

1,

2,

1666

1666

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?