目录

(4)IDELAY_TYPE = VAR_LOAD_PIPE

总目录点这里:《FPGA接口与协议》专栏的说明与导航

1、IDELAYE2是什么?

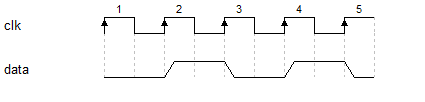

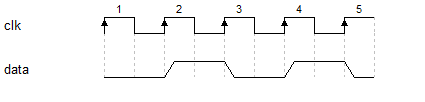

IDELAYE2是FPGA的一个底层原语,它的功能主要是给输入的信号添加延迟。那为什么要给输入信号添加延迟呢?假如输入的数据分别为信号和时钟,由于这两个信号传输的频率可能都特别快,再加上它们的走线存在差别,所以它们进入FPGA时可能存在相位上的差别,如下所示:

data信号在时钟的上升沿变化,此时的采样就很可能导致建立时间违例,

目录

(4)IDELAY_TYPE = VAR_LOAD_PIPE

总目录点这里:《FPGA接口与协议》专栏的说明与导航

IDELAYE2是FPGA的一个底层原语,它的功能主要是给输入的信号添加延迟。那为什么要给输入信号添加延迟呢?假如输入的数据分别为信号和时钟,由于这两个信号传输的频率可能都特别快,再加上它们的走线存在差别,所以它们进入FPGA时可能存在相位上的差别,如下所示:

data信号在时钟的上升沿变化,此时的采样就很可能导致建立时间违例,

1万+

1万+

1957

1957

4933

4933

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?