利用FIFO封装SRIO接口

用FIFO封装Xilinx官方SRIO IP核有两点好处:

-

解决跨时钟域传输问题,方便用户直接使用;

-

解决位宽匹配问题;

这里计划FIFO封装完成后仿真NWRITE和SWRITE两种事务类型。

分为以下几个步骤:

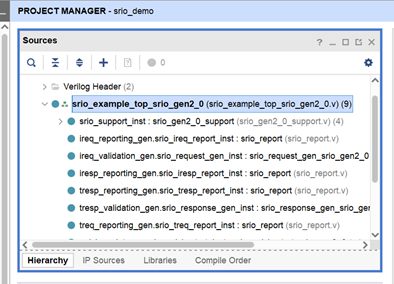

将srio_example示例程序移植到自己的工程中来

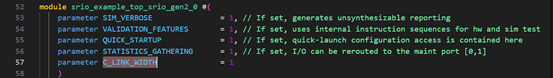

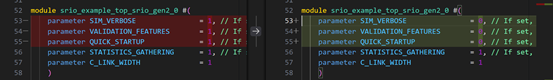

在srio_example顶层文件开头有5个可配置的参数:

在Xilinx SRIO示例程序的顶层文件(srio_example)中,以下参数用于配置SRIO IP核的功能和行为:

SIM_VERBOSE:控制仿真时的日志输出详细程度。

-

设置为1:启用详细仿真模式,输出更多调试信息

-

设置为0:仅输出关键信息

VALIDATION_FEATURES:启用或禁用验证相关的附加功能

-

设置为1:启用验证功能

-

设置为0:仅保留基本功能

QUICK_STARTUP:控制SRIO链路的快速启动模式

-

设置为1:跳过部分初始化步骤,加速链路建立

-

设置为0:执行完整的初始化流程

STATISTICS_GATHERING:启用或禁用统计信息收集功能

-

设置为1:启用统计模块

-

设置为0:关闭统计功能

C_LINK_WIDTH:配置SRIO物理链路的通道宽度

-

可选值:1x(单通道)、4x(四通道)

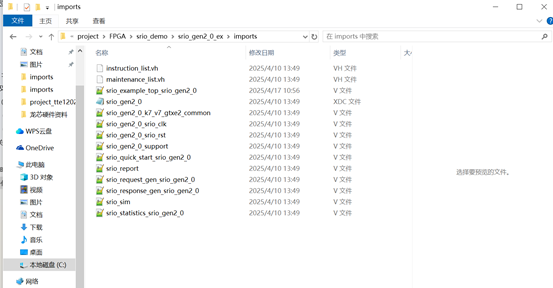

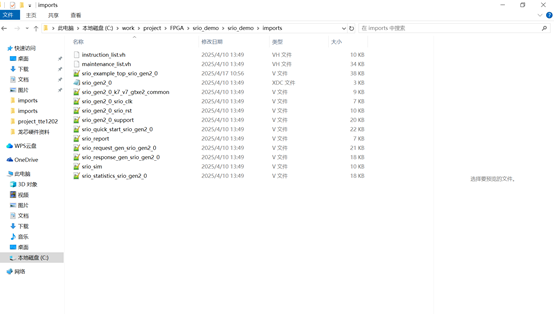

首先将示例工程文件夹中import文件拷贝到自己工程文件中:

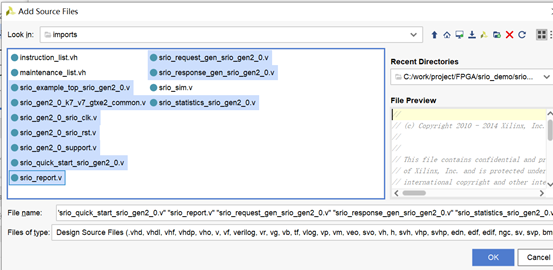

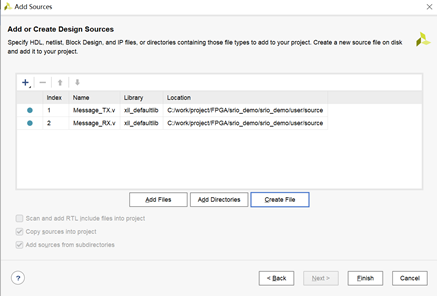

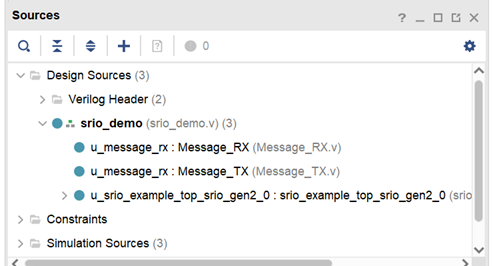

然后在vivado里添加文件,除了仿真文件其余都加进去:

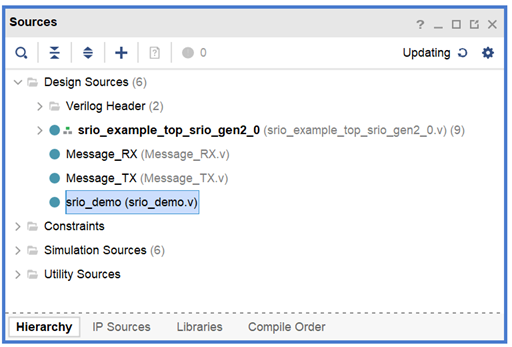

等待一段时间就显示添加好了:

搭建好总的框架,并对SRIO官方案例工程进行一些修改

首先创建好两个模块,分别是Message_TX数据发送模块和Message_RX数据接收模块:

再创建一个顶层模块srio_demo:

对srio_example模块进行修改:

-

屏蔽不必要的报告和附加功能

-

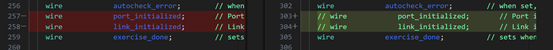

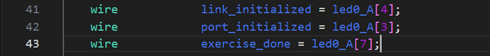

引出port_initialized和link_initialized信号

![]()

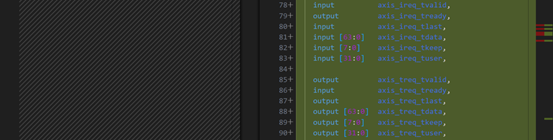

3. 引出log_clk用户时钟

![]()

![]()

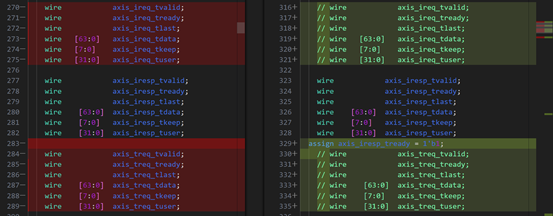

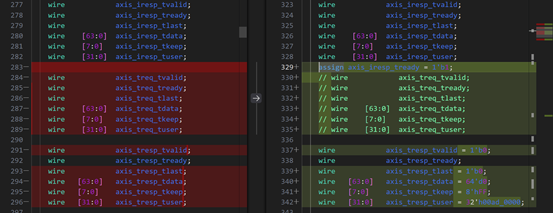

4. 引出ireq和treq相关AXI总线信号

-

给IP核的其他输入信号赋初始值

最终修改后整体框架:

加上FIFO IP核,并配置好相应参数,编写好发送模块

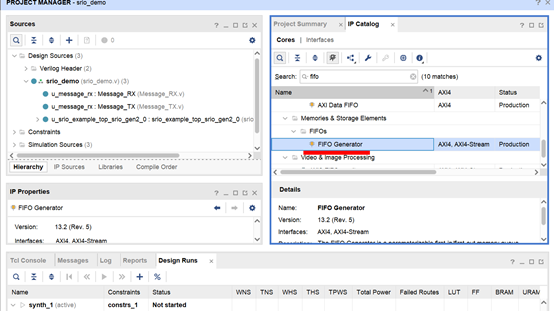

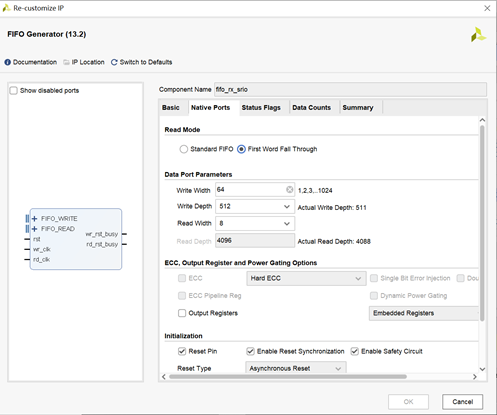

创建FIFO Generator IP核:

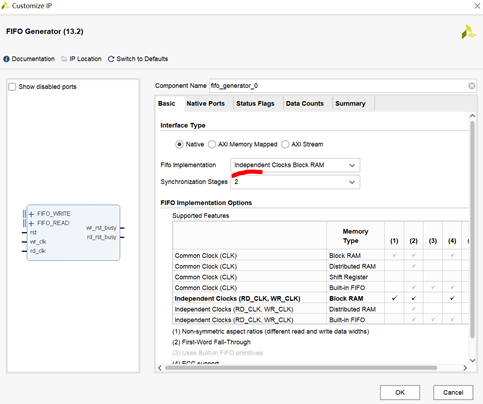

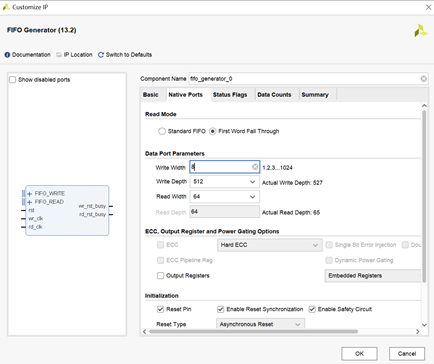

配置参数:

-

选择独立异步时钟

-

设置同步级数(Synchronization stages)

-

选择FWFT读模式(读延迟为0)

-

设置读写的位宽和深度

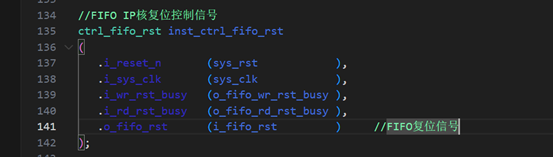

添加FIFO复位控制模块ctrl_fifo_rst:

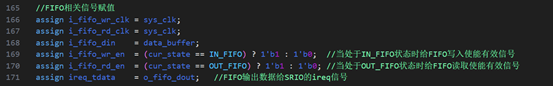

给FIFO相关信号赋值:

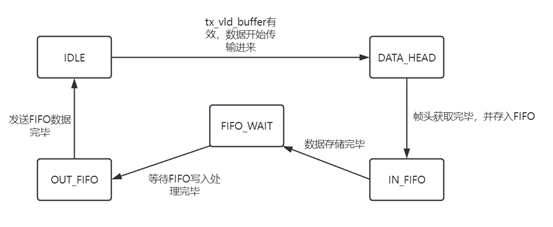

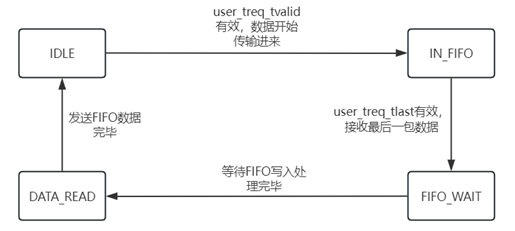

发送模块状态转换图:

加上FIFO IP核,并配置好相应参数,编写好接收模块

创建接收FIFO(位宽与发送相反):

接收模块状态转换图:

编写仿真程序,仿真调试两种事务类型

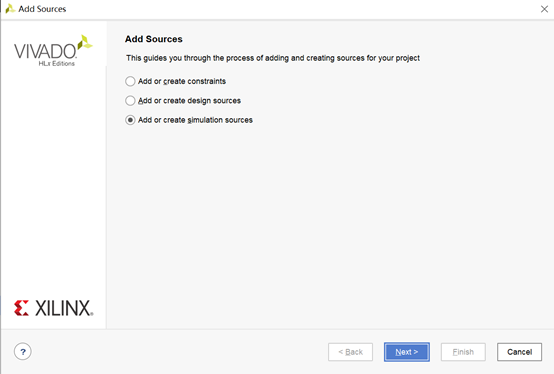

创建仿真文件:

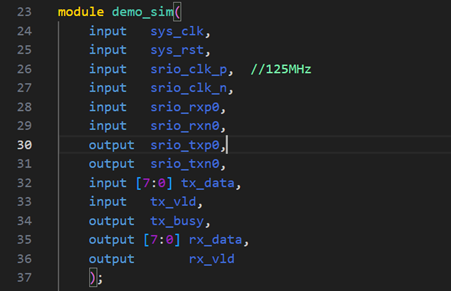

添加顶层文件端口到仿真文件:

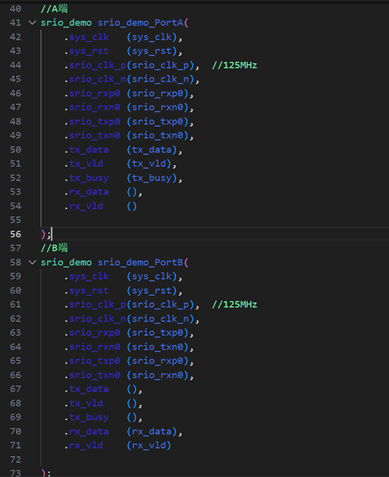

例化PORTA和PORTB端(TX/RX反接):

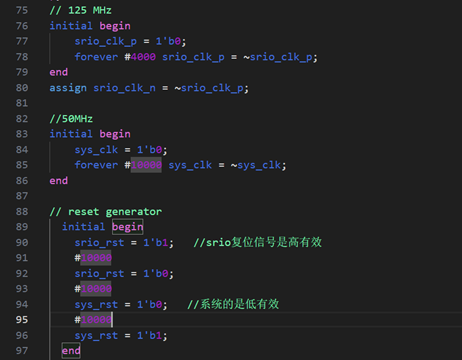

产生时钟和复位信号:

添加监测信号:

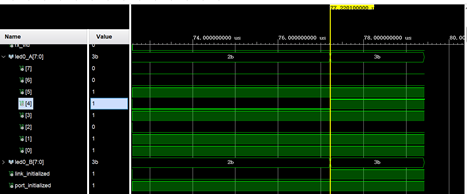

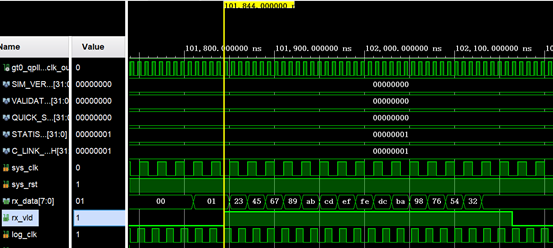

仿真结果:

-

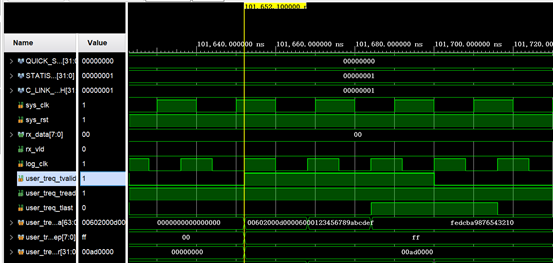

建链成功(port_initialized & link_initialized)

-

初始状态无数据传输

-

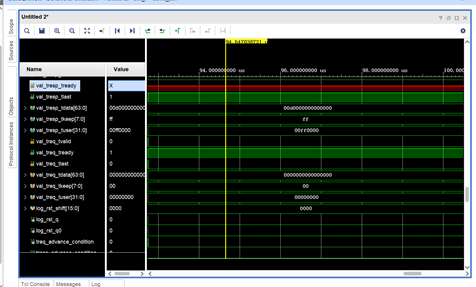

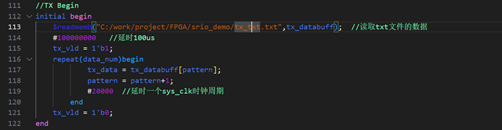

编写传输数据流程

-

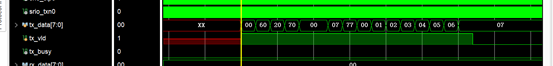

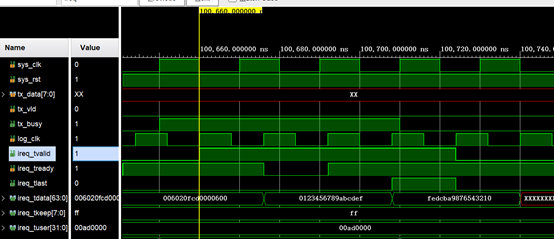

发送端(Message_TX)正常传输,tx_vld发送有效位置1

-

SWRITE事务发送(帧头:0x006020fcd0000600)

-

接收端响应

-

接收模块(Message_RX)输出数据

仿真验证结束,结果符合预期。

本期分享结束,如需源码,进交流群获取。关注公众号,获取免费学习资料!

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?