用于汽车雷达的77吉赫频率倍增双路相控阵FMCW收发器

摘要

本文提出了一种用于汽车雷达应用的全集成77 GHz频率倍增双路相控阵调频连续波(FMCW)收发器。通过采用频率倍增方案,提高了啁啾带宽,同时降低了频率合成器的复杂度以及本振(LO)分配网络的插入损耗。在倍频器中提出了基于顶部注入耦合谐振器的宽锁定范围技术,以最小化覆盖啁啾带宽及足够工艺电压温度变化裕度所需的注入功率,从而降低本振分配网络的功耗。采用电流复用耦合谐振器技术实现每条接收链路中的本振相位偏移。在低噪声放大器中插入基于数字控制人工介质的传输线,以提供工作频率校准能力。接收双路信号由低闪烁噪声电流模式无源混频器转换为中频,随后在跨阻放大器中合并,再经过可重构模拟基带处理。该FMCW收发器采用65 nm CMOS工艺制造,实现了1.93 GHz最大啁啾带宽、12.9 ∼ 13.2 dBm最大发射功率和 47.8 ∼ 100.7 dB可编程接收转换增益。该收发器功耗为343毫瓦,芯片面积为4.64 mm²(包含所有焊盘)。

索引术语

互补金属氧化物半导体,调频连续波,频率倍增,注入锁定倍频器,相控阵。

一、引言

现代社会对驾驶安全的需求正在快速增长。汽车雷达在避免交通事故中发挥着重要作用。基于激光、红外线、超声波和毫米波(mm‐wave)的不同感知技术已被提出用于汽车雷达。在这些技术中,毫米波由于在极端温度、雨、雾或雪等各种环境下的优异鲁棒性而受到广泛关注[1]。毫米波汽车雷达的工作频率主要位于24 GHz或77 GHz附近。近年来,由于77 GHz具有更小的波长、更小的天线尺寸,从而实现更紧凑的尺寸,因此正逐渐从24 GHz转向77 GHz[2]–[4]。

随着CMOS工艺的快速发展,其在低成本毫米波汽车雷达芯片领域展现出广阔前景[5]–[12]。在[6]中提出了一种调频连续波(FMCW)雷达收发器,其中FMCW信号首先由低频直接数字频率合成器(DDFS)生成,然后混频至中频(IF),最后通过整数‐N锁相环(PLL)频率合成器倍频至毫米波频段。该FMCW信号发生器由于DDFS中高分辨率数模转换和大容量只读存储器的存在,导致功耗和芯片面积较高。该收发器的发射功率仅为–2.8 dBm,限制了检测范围。在[5]中提出了另一种FMCW雷达收发器,其中FMCW信号通过数字控制分数‐N PLL频率合成器的分频比来生成,通过去除功耗较高的DDFS,节省了功耗和芯片面积。该收发器工作频率为75.6至76.3 GHz,仅有0.7 GHz啁啾带宽,且未集成模拟基带以提供可编程增益和信号滤波功能。在[7]–[8]中提出了具有可重构啁啾的FMCW信号发生器,以解决多目标检测问题。此外还提出了基于混合信号[11]或全数字[12]频率合成器的FMCW信号发生器。然而,这些工作中均未集成功率放大器(PA)和接收链路。在[9]中提出了一种基于77 GHz次谐波混频技术的雷达接收机,以降低本振(LO)频率并避免推挽效应,但仅集成了接收链路。这些已报道的FMCW雷达收发器存在的另一个主要问题是啁啾带宽受限,在[5]–[8]中仅为数百兆赫兹,在[11]–[12]中为1.5 GHz。本文提出了一款基于频率倍增方案的全集成77 GHz双路相控阵FMCW雷达收发器[13]。该FMCW收发器实现了1.93吉赫兹最大啁啾带宽、12.9 ∼ 13.2 dBm最大发射功率以及47.8 ∼ 100.7 dB可编程接收转换增益。

本文组织如下。第二节介绍了雷达收发器的系统架构。第三节详细描述了收发器的电路实现。第四节讨论了收发器的测量结果,第五节给出了一些结论。

二、系统架构

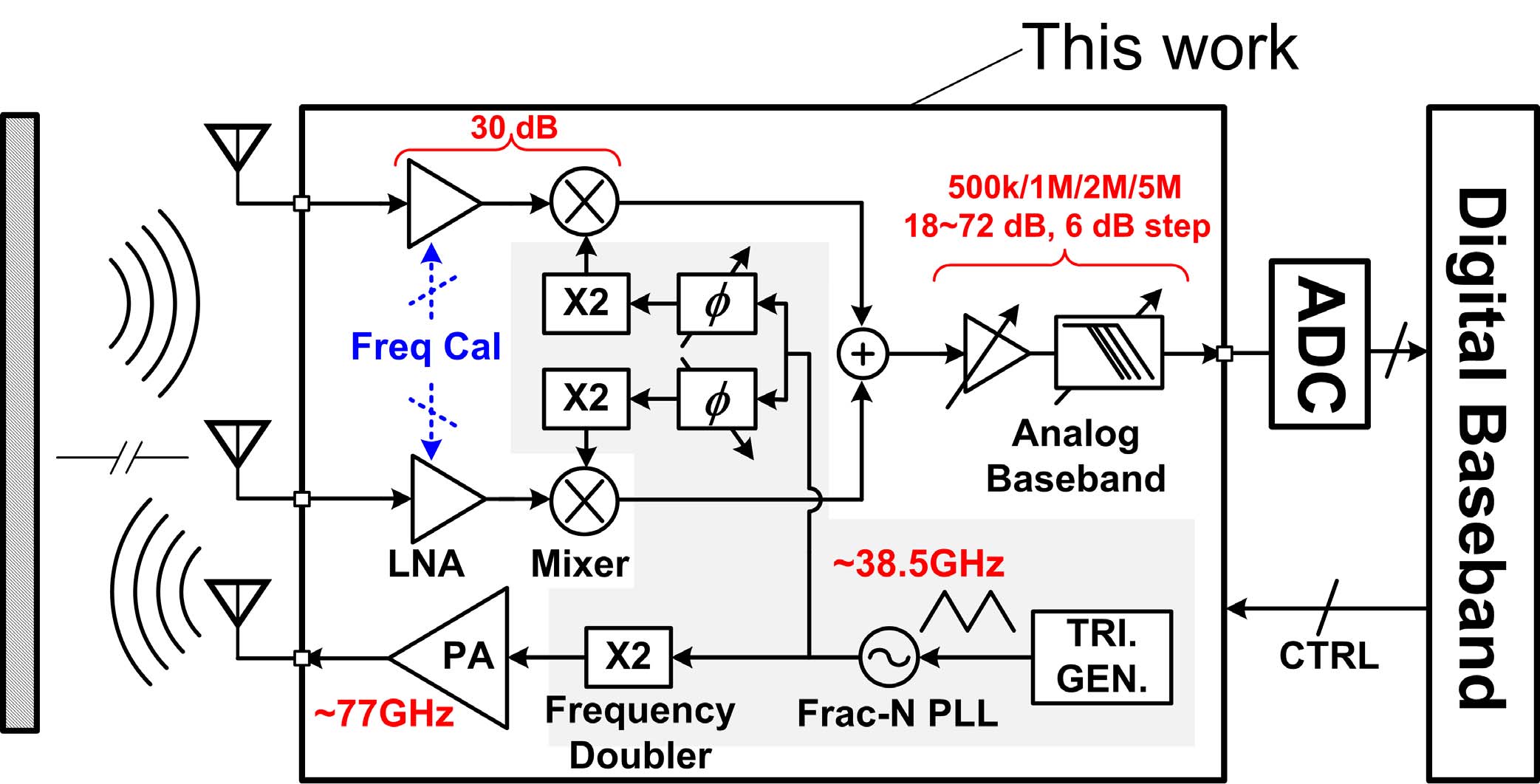

双通道相控阵FMCW雷达收发器的系统架构如图1所示。该系统采用频率倍增方案。FMCW信号发生器首先产生一个约38.5 GHz的FMCW信号,然后通过注入锁定倍频器将该信号倍频至77 GHz。在每条接收本振路径中的倍频器之前插入了移相器。FMCW信号发生器基于分数‐N PLL频率合成器,因其结构简单且功耗低。发射路径中集成了功率放大器。接收路径由两个接收前端和一个模拟基带组成。每个接收前端包含一个低噪声放大器和一个电流模式无源混频器。来自两条接收路径的中频信号在跨阻放大器中合并,随后由后续的模拟基带进行放大和滤波。模拟基带提供54 dB可编程增益以及带宽可在500千赫至5兆赫之间可重构的五阶低通滤波。此外,还集成了基于带隙的偏置电路和串行外设接口(SPI),分别用于提供所需的所有偏置电流/电压和数字控制信号。

该收发器采用了双通道相控阵架构。当收发器用于需要窄波束宽度天线且无需波束转向的长距离应用时,两条接收路径以相同的相位偏移设置同时工作,理论上可使接收机灵敏度提高3 dB。当收发器用于需要宽波束宽度天线的短距离应用时,双路相控阵架构可提供波束转向能力,以实现对目标的跟踪或在空间上分离多个目标。本设计采用本振移相方案实现双路相控阵,以避免在信号路径[15]中引入额外的插入损耗。

雷达收发器的规格可以通过著名的雷达方程[16]计算得出

$$ P_R = \frac{\sigma G_T G_R \lambda^2}{(4\pi)^3 L_{ATM} R^4} \cdot P_T $$

其中,$G_T$和$G_R$分别为发射天线增益和接收天线的增益,$P_T$和$P_R$分别为发射功率和接收功率,$\lambda$为波长,$R$为目标距离,$L_{ATM}$为大气损耗,$\sigma$为目标的雷达散射截面。

在77 GHz时,大气损耗约为0.3 ∼ 0.5 dB/km[17]。普通汽车的雷达散射截面已在[4]中研究,并在此假设为10 m²。假设接收天线和发射天线的增益均为20分贝各向同性,发射功率为10分贝毫瓦。则接收功率为

$$ P_{R,\text{dBm}} \approx -21 - 40 \log_{10}(R) $$

当雷达的检测范围为10 ∼ 250米时,接收功率为−61 ∼ –117 dBm。接收机中的模拟基带具有18至72 dB的可编程增益,步进为6 dB,提供了大部分动态范围,从而降低了对外部ADC动态范围的要求。包括低噪声放大器和混频器在内的接收前端还提供30 dB增益。当FMCW啁啾带宽为2 GHz、周期为2毫秒时,对应10 ∼ 250米目标距离的检测到的中频频率计算为0.133 ∼ 3.33 MHz。在本设计中,模拟基带的带宽可重构为500千赫、1 MHz、2 MHz或5兆赫,以支持多种检测范围。

接收机的噪声系数(NF)要求根据最小接收功率、雷达数字基带所需的信噪比(SNR)以及快速傅里叶变换(FFT)处理的分辨率,通过以下方程[6]计算得出:

$$ NF = 174 - SNR| {\text{dB}} + S {\text{min}}| {\text{dBm}} - 10 \cdot \lg(f {\text{FFT}} p_{\text{FFT}}) $$

在白噪声中以99%检测概率和10⁻¹⁰虚警率[16]检测单频信号所需的信噪比为16 dB。假设FFT采样频率为10 MHz,FFT点数为5120,则计算得到所需噪声系数为8 dB,因此每条接收链路的噪声系数应小于11 dB。

本文讨论了多目标检测问题。当检测区域内存在多个运动目标时,可以检测到两个以上的中频频率。FMCW雷达可能无法为每个目标找到正确的中频频率组合,从而导致鬼影目标检测。该问题可通过重新配置FMCW啁啾信号的斜率[7]–[8],[14]来解决。假设发射一个斜率为$s$的线性频率斜坡,用于探测距离为$R$、瞬时速度为$v$的一个目标。则由于发射信号与回波信号之间的时间差以及多普勒效应所得到的中频频率可计算如下

$$ f_{IF} = \frac{2f_c}{c} v + \frac{2s}{c} R $$

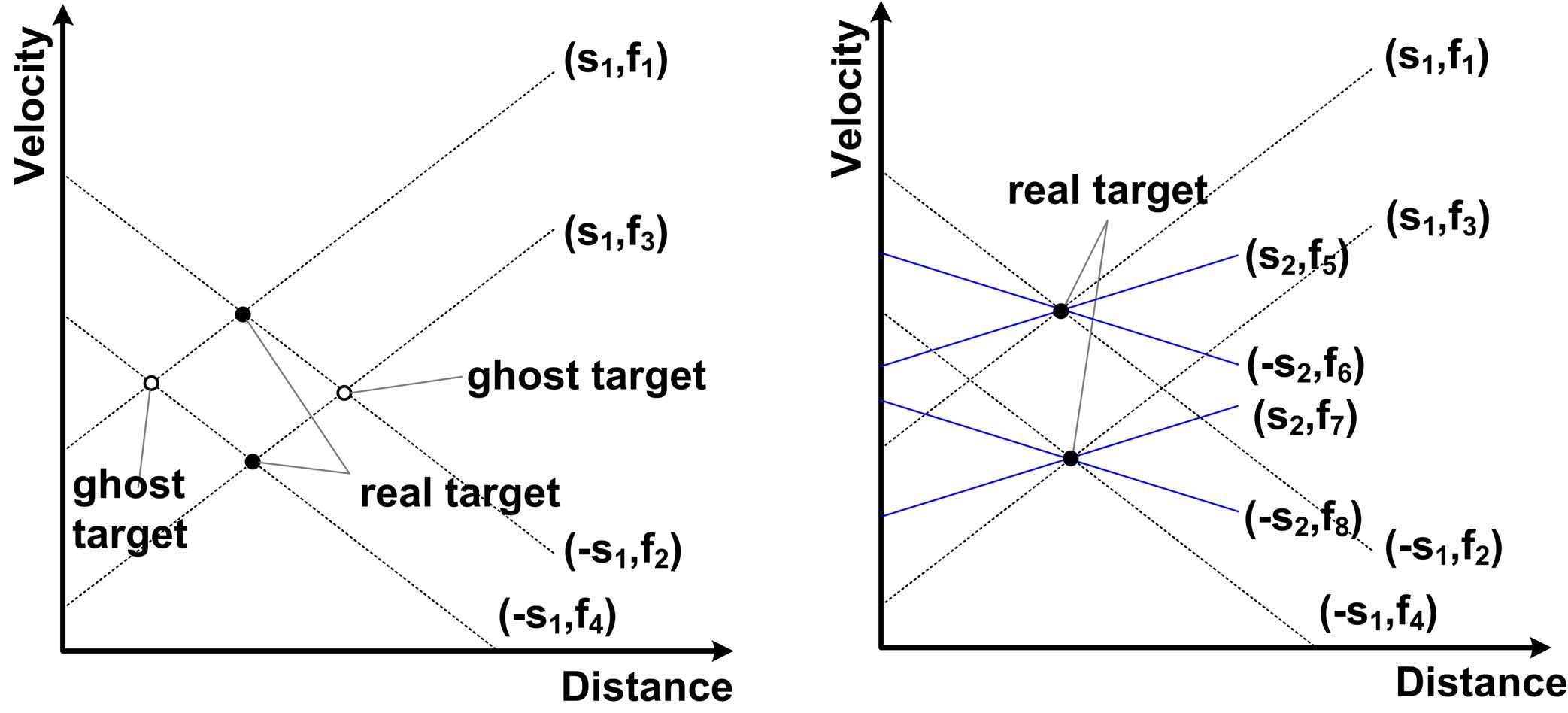

公式(4)可以在速度‐距离平面上绘制成一条直线。图2(a)显示了使用固定斜率FMCW啁啾信号检测两个运动目标的情况。在速度‐距离平面上有四个交点,其中两个对应于鬼影目标。另一方面,

当使用具有两个不同斜率的FMCW啁啾信号时(如图2(b)所示),可以得到八个不同的中频频率。这样,两个真实目标的位置就可以无混淆地确定。在此工作中,FMCW啁啾信号也具有可重构斜率。双路相控阵还通过在空间上分离多个目标来帮助消除鬼影目标检测问题。

III. 电路实现

A. FMCW信号发生器

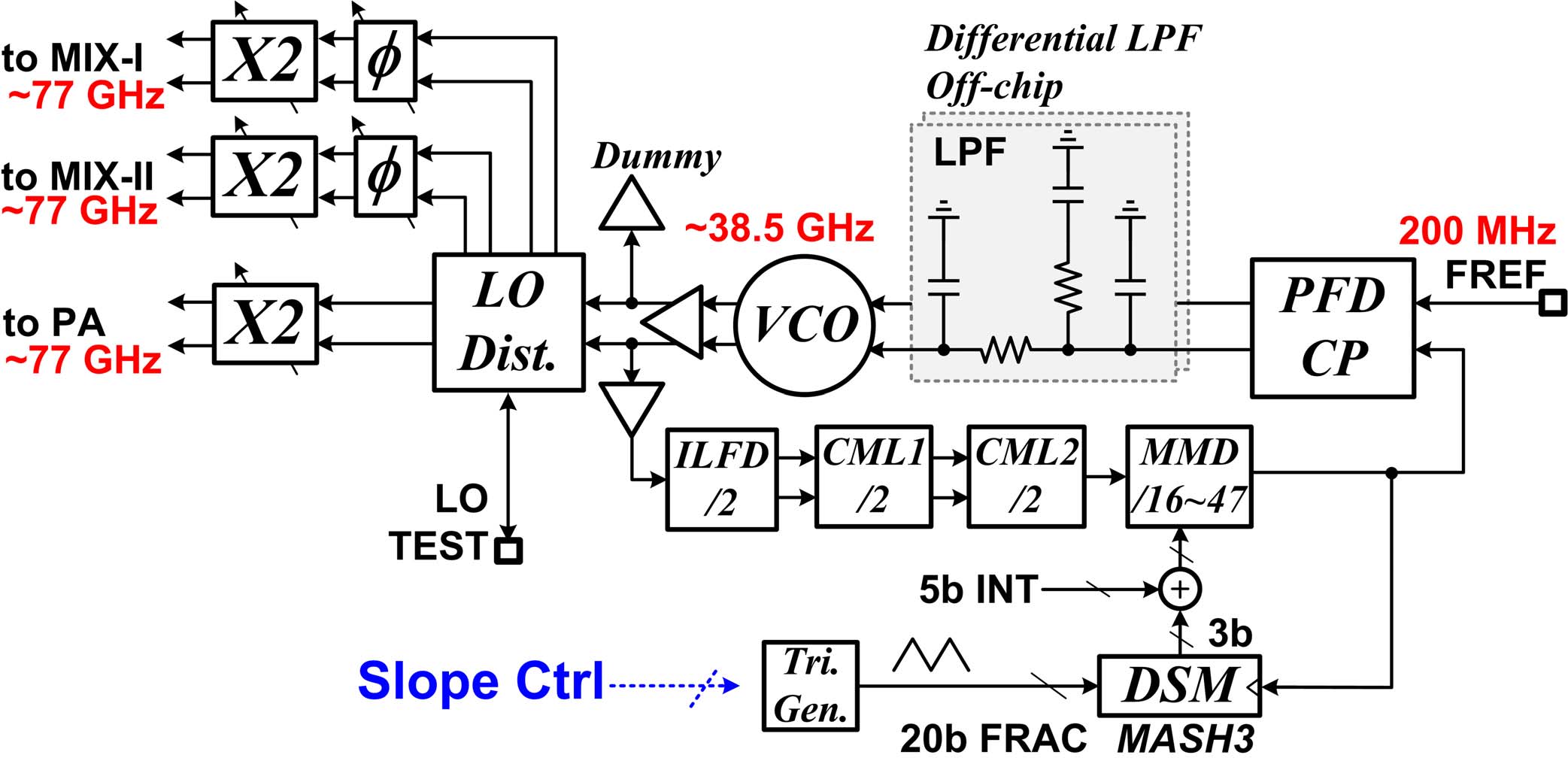

图3展示了所提出的FMCW信号发生器的框图。详细内容将在以下小节中介绍。

1) 倍频方案:

与基频方案相比,倍频方案具有多个优势。首先,基本FMCW信号发生器的输出频率从约77 GHz降低至约38.5 GHz,从而降低了FMCW信号发生器中频率合成器[特别是压控振荡器(VCO)]的复杂性。由于变容二极管在半频处具有更高的品质因数(Q),VCO性能得以提升。更重要的是,当信号频率加倍时,啁啾带宽也会加倍。在相同的VCO增益和调谐电压范围内,倍频方案可使啁啾带宽提高一倍。其次,相移值也随频率加倍而加倍,因此移相器的相移覆盖范围可减少一半。第三,基本FMCW信号发生器的输出功率要求得以放宽。倍频器同时充当功率中继器,并被放置在PA或天线附近,混频器以最小化布线损耗。基本FMCW信号发生器无需直接驱动功率放大器和混频器,其输出功率仅需保持倍频器锁定即可。本振分配网络在半频处的损耗更小,进一步降低了对输出功率的要求。该收发器通过减少高功耗本振缓冲器的数量来降低功耗。当阵列数量较大时,这一优势尤为显著。然而,倍频方案中需要额外增加三个倍频器,这将在一定程度上抵消功耗上的优势。

2) 分数-N PLL频率合成器:

分数‐N PLL频率合成器工作在约38.5 GHz。多模分频器(MMD)由一个20位三阶1‐1‐1 MASH ΔΣ调制器(DSM)控制,分频比范围为16至47。参考频率为200 MHz,通过降低分频比来减小电荷泵(CP)、环路滤波器、分频器和参考源的噪声贡献,并有助于将DSM的噪声推至高频。分频比的小数部分由数字三角波发生器控制。三角波的谷值/峰值以及周期是可重构的,因此FMCW啁啾信号的带宽和斜率也是可重构的。本设计中,三角波发生器的时间步长为50 μs。斜坡精度与DSM的噪声贡献之间存在折衷。对于给定的FMCW啁啾信号斜坡速率(斜率),较大的时间步长会导致较大的分频比步长,从而产生较大的频率步长,这会降低斜坡精度。另一方面,为了将DSM噪声推向高频,希望采用较大的时间步长。当斜坡速率为1 GHz/s时,对应50 μs时间步长的频率步长为50 kHz。如[7]所述,分数‐N PLL的环路带宽也需要仔细设计。一方面,PLL的稳定时间大约与环路带宽成反比,应大于DSM的时间步长;否则,PLL输出的瞬时频率将呈现阶梯状波形而非线性斜坡。另一方面,环路带宽不能太小;否则,FMCW啁啾信号的高次谐波将被合成器滤除,输出的瞬时频率将呈现正弦波形而非三角波形。本设计中,DSM的时间步长为50 μs,FMCW啁啾信号的周期约为1 ∼ 2 ms。环路带宽设计为100 kHz,因此PLL的稳定时间大于DSM的时间步长,并且至少允许100阶的三角波啁啾谐波通过合成器。

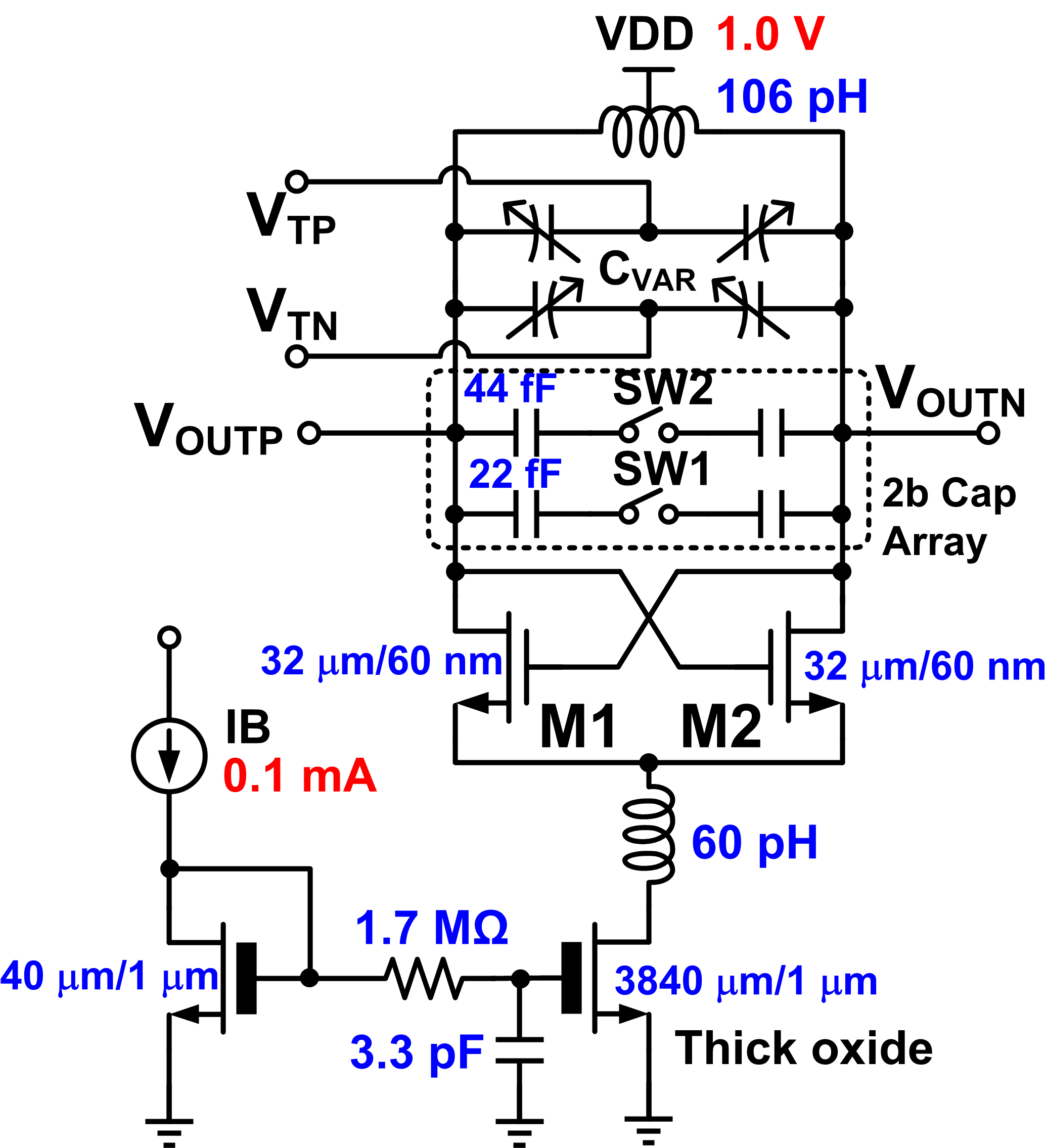

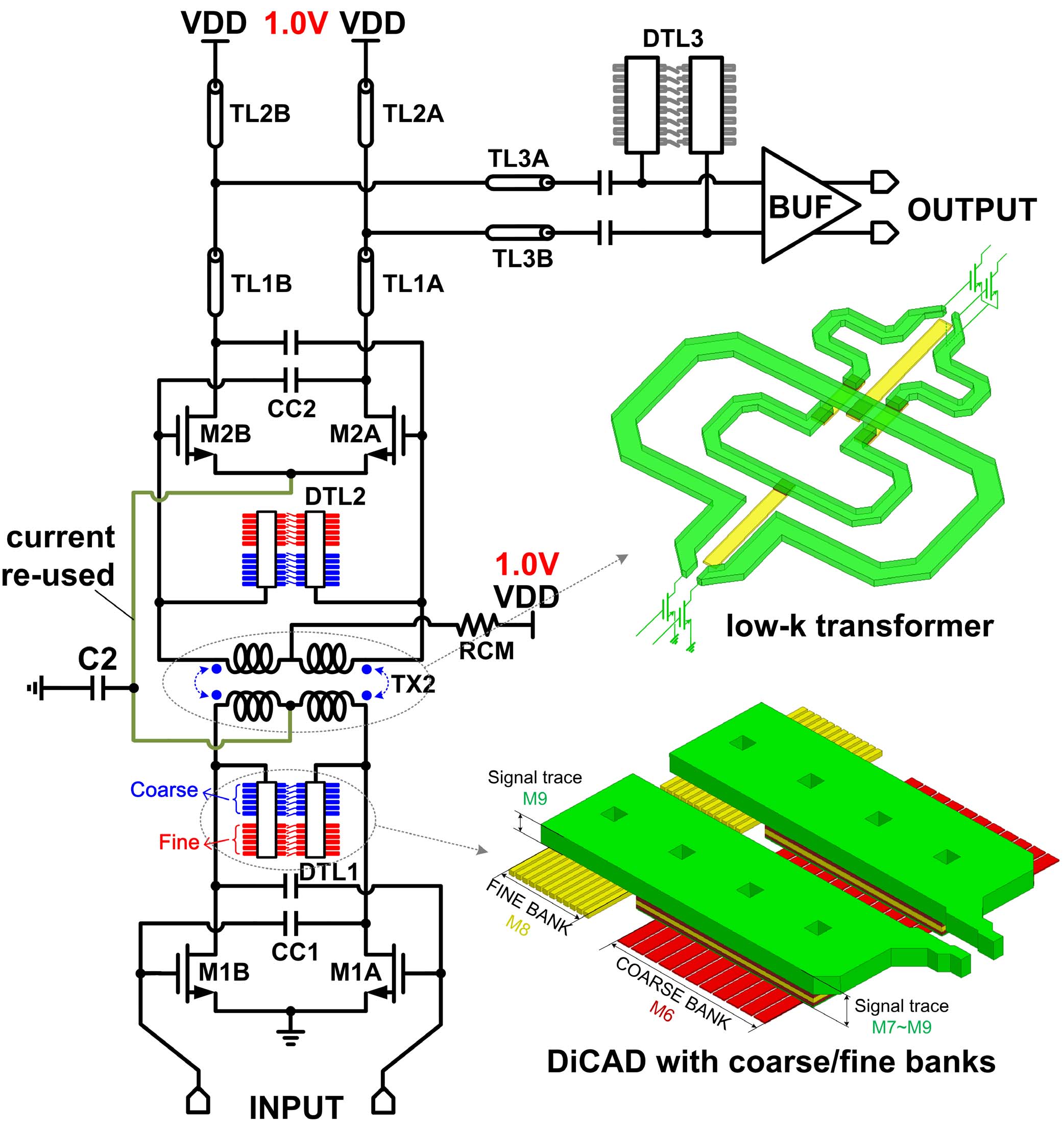

VCO(图4)采用全差分调谐,使用两对反向连接的变容二极管以抑制共模干扰并改善相位噪声性能[18]。使用了两位开关电容阵列。每个频率调谐曲线覆盖的频率范围至少为啁啾带宽,因为在单个线性调频周期内不允许切换调谐曲线。采用了尾电流滤波技术[17]以进一步提升相位噪声性能。

3) 注入锁定倍频器和移相器:

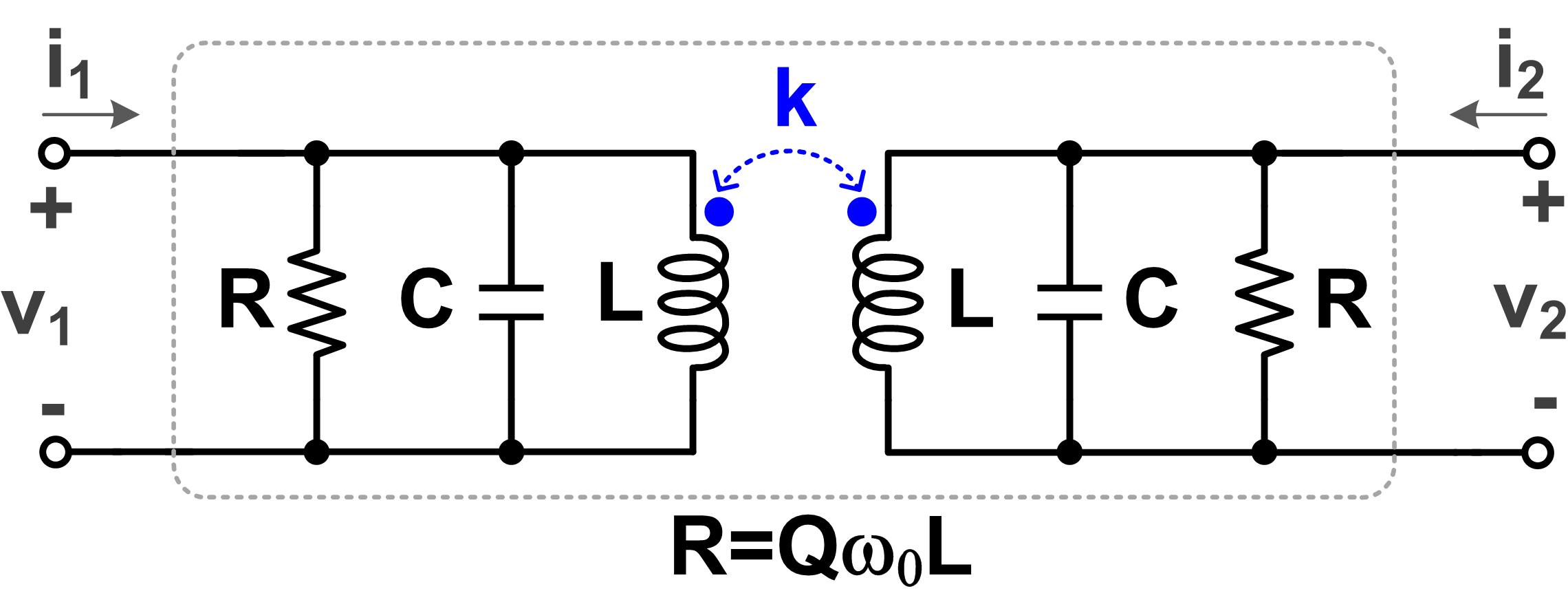

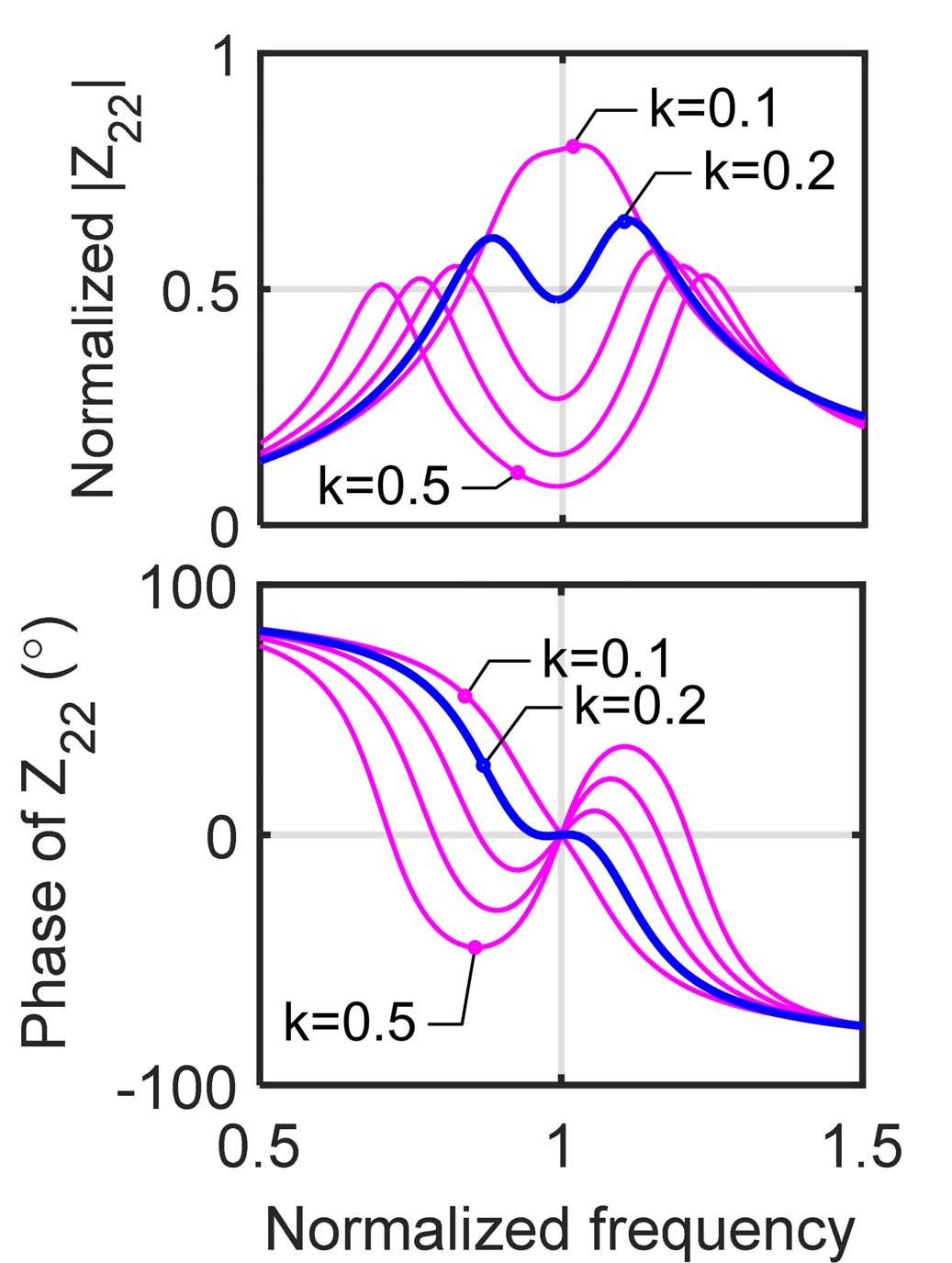

在介绍倍频器和移相器的细节之前,首先讨论用于倍频器和移相器中的耦合谐振器。图5(a)显示了耦合谐振器的原理图。假设两个谐振罐是对称的,并且$R = Q\omega_0 L$,其中$\omega_0 = 1/\sqrt{LC(1 - k^2)}$为简化起见。图5(b)显示了归一化到$Q\omega_0 L$的仿真阻抗$Z_{22}$以及不同$k$和$Q = 5$下的阻抗$Z_{22}$的相位。当$k = 0.2$时,$Z_{22}$的相位响应曲线在过零点附近是平坦的,这在[31]中被称为“相位平台”。在“相位平台”区域,归一化的$|Z_{22}|$约为0.5。假设$\omega = \omega_0 + \Delta\omega$且$\Delta\omega \ll \omega_0$,不难计算出

$$ |Z_{22}(\omega)| \approx Q\omega_0 L \left| \frac{(2Q - 2j - 2j k^2)\Delta\omega/\omega_0 - j(1 - k^2)}{-(4Q - 2j + 2j k^2)\Delta\omega/\omega_0 + j(1 - k^2)^2 + k^2 Q^2} \right| $$

$$ \tan\angle Z_{22}(\omega) \approx \frac{2Q k^2}{Q^2 - (1 - k^2)^2} \cdot \frac{(1 - k^2)(k^2 Q^2 + (1 - k^2)^2)}{} \cdot \frac{\Delta\omega}{\omega_0} $$

对于传统RLC网络,我们有[20]

$$ \tan\angle Z(\omega) \approx 2Q \frac{\Delta\omega}{\omega_0} $$

比较(6)和(7),我们可以将耦合谐振腔在$\omega_0$附近的有效Q定义为

$$ Q_{\text{eff}} \triangleq \frac{Q}{k^2 Q^2 - (1 - k^2)^2} \cdot \frac{(1 - k^2)(k^2 Q^2 + (1 - k^2)^2)}{} $$

与传统RLC网络的Q值类似,耦合谐振器的$Q_{\text{eff}}$反映了在$\omega_0$处相位频率响应曲线的斜率。具体而言,将$k = 0.2$和$Q = 5$代入(8)式,可得$Q_{\text{eff}} = 0.042Q$。耦合谐振器降低了$Q_{\text{eff}}$,这有利于展宽频率锁定范围,下文将对此进行说明。

图5(c)绘制了在不同$k$和$Q = 5$下归一化的$|Z_{21}|$及其相位。当$k = 0.2$时,归一化的$|Z_{21}|$达到最大值,并在其3 dB带宽内实现最平坦的响应,且此时$Z_{21}$的相位响应随频率大致呈线性变化。在$|Z_{21}|$的3 dB带宽内,相移覆盖范围达到178度。相比之下,RLC谐振器在其3 dB带宽内的相移范围仅为90度。再次假设$\omega = \omega_o + \Delta\omega$和$\Delta\omega \ll \omega_0$,则

$$ |Z_{21}(\omega)| = Q\omega_0 L \left| \frac{k Q(1 + \Delta\omega / \omega_0)}{-(4Q - 2j + 2j k^2) \Delta\omega / \omega_0 + j(1 - k^2)^2 + k^2 Q^2 / (1 - k^2)} \right| $$

耦合谐振器用于注入锁定倍频器中以增强锁定范围。类似的想法已应用于次谐波注入锁定振荡器[31]中。在收发器中,宽带宽的锁定范围至关重要,原因有两点:首先,倍频器应在整个啁啾带宽范围内保持锁定,并留有足够的工艺电压温度变化裕度;其次,更宽的频率锁定范围通常意味着需要更小的输入注入功率即可使倍频器保持锁定状态,从而减少了对功耗较大的本振缓冲器的需求。

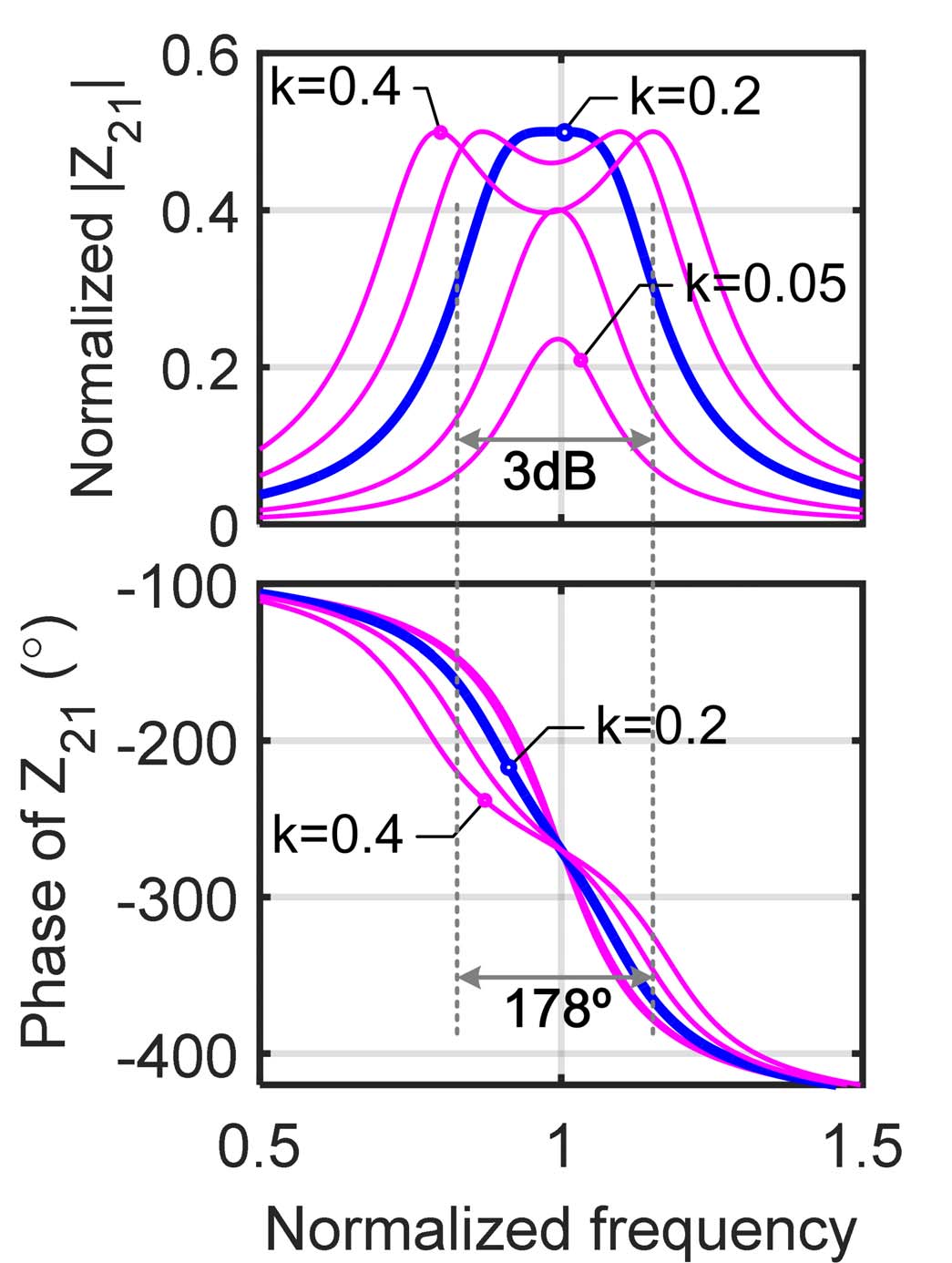

图6显示了倍频器的原理图。推挽对M1A/M1B产生二次谐波电流信号,该信号被注入到耦合谐振器的顶部。交叉耦合对M2A/M2B用于补偿耦合谐振器的损耗。推挽对和交叉耦合对的直流路径相互分离,因此可以独立优化推挽对的偏置电压,以获得最强的二次谐波电流。

耦合谐振器的简化原理图。(b) 当Q= 5时,不同k值下的仿真 Z22。(c) 当Q= 5时,不同k值下的仿真Z21)

耦合谐振器的简化原理图。(b) 当Q= 5时,不同k值下的仿真 Z22。(c) 当Q= 5时,不同k值下的仿真Z21)

当倍频器处于注入锁定状态时,由注入电流引入的相移值被耦合谐振器补偿。振荡频率偏离其自由运行值。对应于最大相移的频率偏差即为频率锁定范围。假设注入的二次谐波电流为$i_{\text{INJ}}$,振荡电流为$i_{\text{OSC}}$。根据[20]中类似的相量图分析,当倍频器锁定时,应满足以下方程:

$$ |i_{\text{INJ}} \cdot Z_{21}(\omega)| \geq |i_{\text{OSC}} \cdot Z_{22}(\omega)| \cdot \sin \phi_{\text{max}} $$

其中$Z_{21}(\omega)$和$Z_{22}(\omega)$是耦合谐振器的Z参数,$\phi_{\text{max}}$是由注入电流引起的最大相移。由(5)和(9)可得

$$ \left| \frac{Z_{21}(\omega)}{Z_{22}(\omega)} \right| \approx \frac{k Q}{1 - k^2} \cdot \frac{1}{\left| 1 + (1 + 2j / Q (1 - k^2)) \Delta\omega / \omega_0 \right|} \approx \frac{k Q}{1 - k^2} $$

方程(11)仅在频率接近$\omega_0$时成立,当频率偏离$\omega_0$时,它会高估$|Z_{21}(\omega)/Z_{22}(\omega)|$。然而,该近似仍然具有价值,因为它在不丢失主导因素的情况下,得到了频率锁定范围的一个简单而直接的表达式。在围绕$\omega_0$的9.5%频率范围内,该近似的误差小于10%。对于耦合谐振器,我们可以从(6)推导出最大频率偏差$\Delta\omega_{\text{max}}$与$\phi_{\text{max}}$之间的关系。

$$ \phi_{\text{max}} \approx \tan^{-1}(2Q_{\text{eff}} \Delta\omega_{\text{max}} / \omega_0) $$

利用(10)–(12),可以计算出锁定范围

$$ LR = 2\Delta\omega_{\text{max}} = \frac{\omega_0}{Q_{\text{eff}}} \cdot \frac{1}{\sqrt{(1 - k^2)/(kQ) \left| i_{\text{OSC}} / i_{\text{INJ}} \right|^2 - 1}} \approx \frac{k Q}{1 - k^2} \cdot \frac{\omega_0}{Q_{\text{eff}}} \cdot \left| \frac{i_{\text{INJ}}}{i_{\text{OSC}}} \right| $$

注意,(13)也可以通过在$\phi_{\text{max}}$较小时近似$\sin \phi_{\text{max}} \approx \tan \phi_{\text{max}} \approx \phi_{\text{max}}$而更容易地推导出来。它表明由于耦合谐振器的$Q_{\text{eff}}$较小,其频率锁定范围被大大增强。

引入两条数字控制的人工电介质(DiCAD)传输线[21]作为可变电容器,用于校准倍频器核心的自由运行频率和输出缓冲器的工作频率[22]。仿真得到的频率锁定范围如图6插图所示。当输入注入功率高于–12 dBm时,对于DiCAD传输线DTL1的每个控制码,频率锁定范围均大于2 GHz。

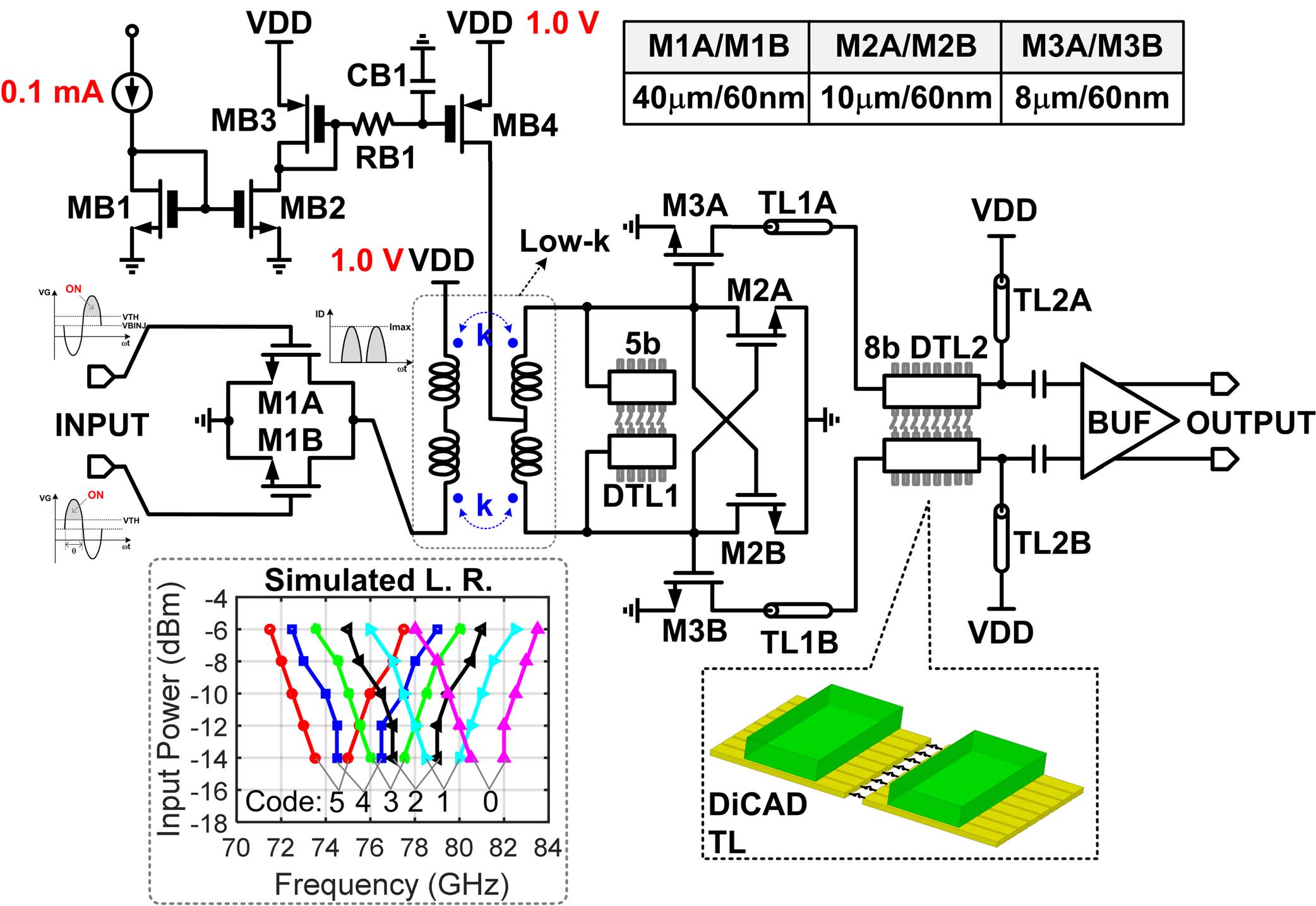

移相器的原理图如图7所示。采用了一种基于耦合谐振器的电流复用有源移相器。该耦合谐振器能够在增益变化较小的情况下增大相移范围。与开关式或反射式无源移相器[23]–[24]相比,其可提供正增益,并且在不同相移值下具有较小的增益变化,因此不再需要[23]中的可变增益放大器。与矢量叠加移相器[25]相比,本设计无需正交输入信号,从而降低了本振发生器的复杂度。

移相器由两个通过耦合谐振器连接的共源级联级组成。通过将M2A/M2B的共源极连接到低k变压器TX2初级线圈的中心抽头,实现了直流电流的复用。如图7所示,通过减小初级线圈和次级线圈的重叠面积来实现低k。次级线圈在初级线圈外部的走线引入了漏感,以简化变压器的设计,并通过折叠该走线以减小芯片面积[26]。漏感可以增加变压器的次级电感,降低k值,同时不影响初级电感。DiCAD传输线在耦合谐振器中用作可变电容器,以实现粗调和细调调谐组,如图7所示。

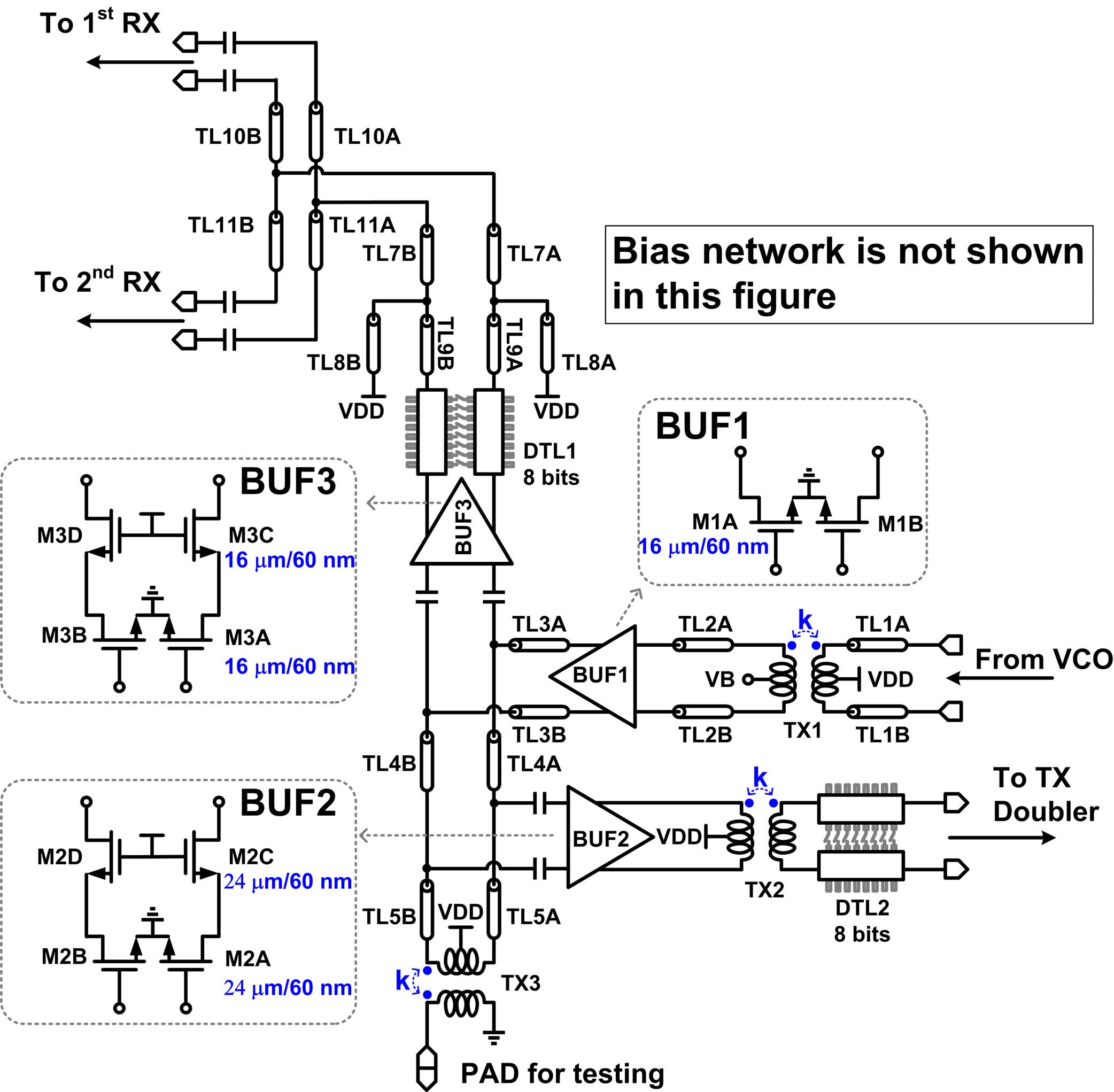

本振分配网络:图8显示了本振分配网络的原理图。如前所述,由于采用了频率倍增方案和宽锁定范围的倍频器,本振分配网络上的损耗要求得以放宽。来自压控振荡器的本振信号首先通过变压器耦合到一个共源极缓冲级(图8中的BUF1)。然后,该信号被分成三条路径:发射路径、接收路径和测试焊盘。在发射路径和接收路径中插入了共源共栅缓冲器(图8中的BUF2和BUF3)。这些缓冲器用于提供必要的反向隔离,并支持不同的测量需求。根据不同的测量要求,这些缓冲器可以独立地开启或关闭。由于倍频器所需的注入功率较小,这些缓冲器工作在低电流状态以节省功耗,总功耗为7.3毫瓦。

B. 毫米波放大器

在所提出的调频连续波收发器中,集成了两个低噪声放大器和一个功率放大器,以提高接收灵敏度和发射功率。具体细节在此介绍。

1) 低噪声放大器:

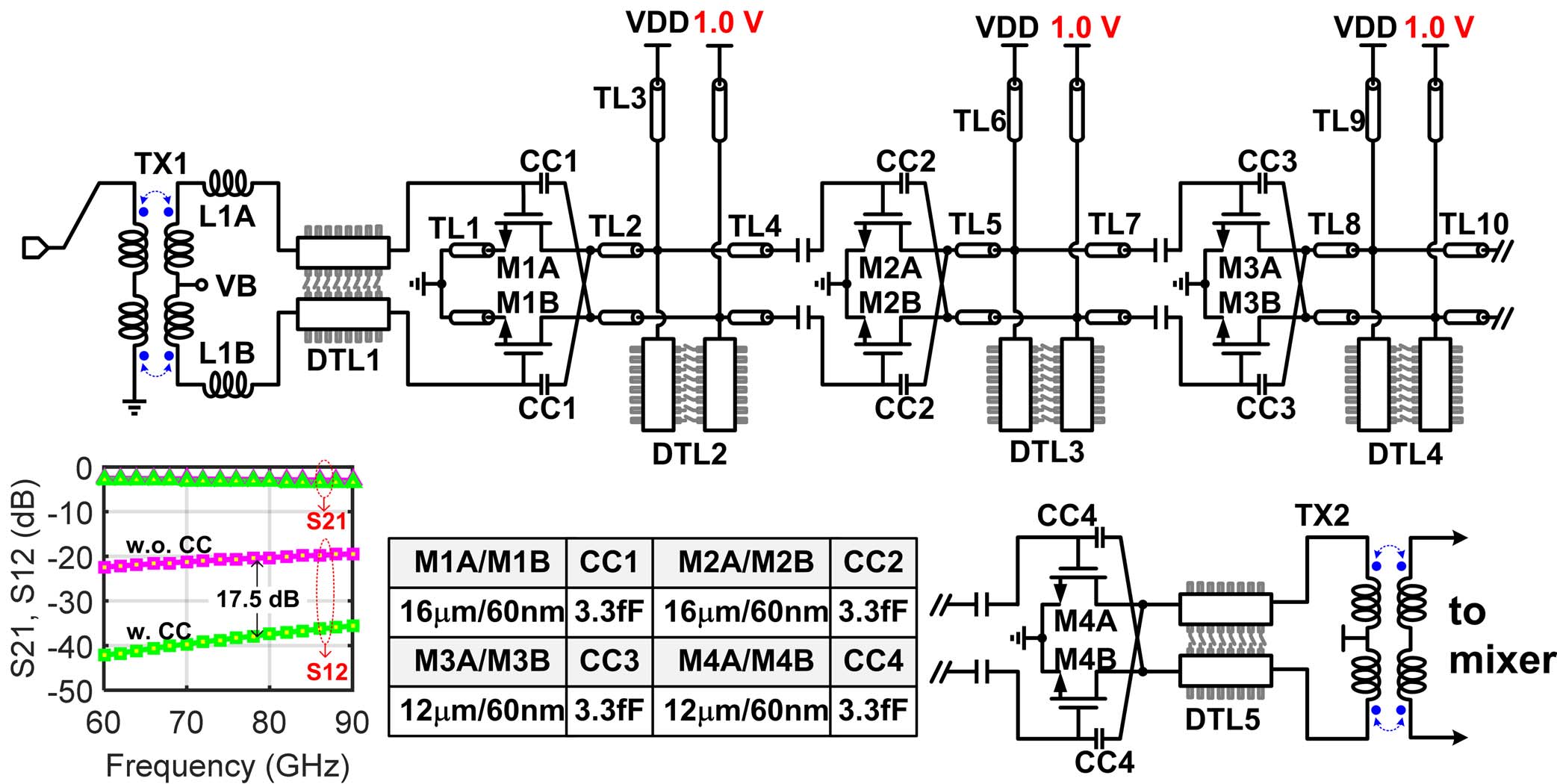

低噪声放大器的原理图如图9所示。该低噪声放大器由四个伪差分共源极放大级组成。此处引入中和电容技术[27]以提高增益、反向隔离和稳定性。如[32]所述,中和电容过大会降低稳定性。为了确保稳定性,中和电容被优化以实现最大反向隔离,而非最高增益。这些电容器采用金属层M6和M7之间的寄生电容实现。仿真结果表明,该低噪声放大器在中和电容变化至少达到50%的情况下仍保持无条件稳定。仿真结果显示,采用中和电容技术可在77 GHz下将伪差分共源对的反向隔离度提高17.5 dB。在第一级放大阶段加入了感性源极退化传输线以实现输入阻抗匹配。

通过在低噪声放大器(LNA)的每一级中插入8位DiCAD传输线,可对LNA的工作频率进行数字校准。由于工艺电压温度变化(PVT variations)或建模不准确导致的LNA频率漂移,可以采用与[28]中类似的方法进行校准。

2) 功率放大器:

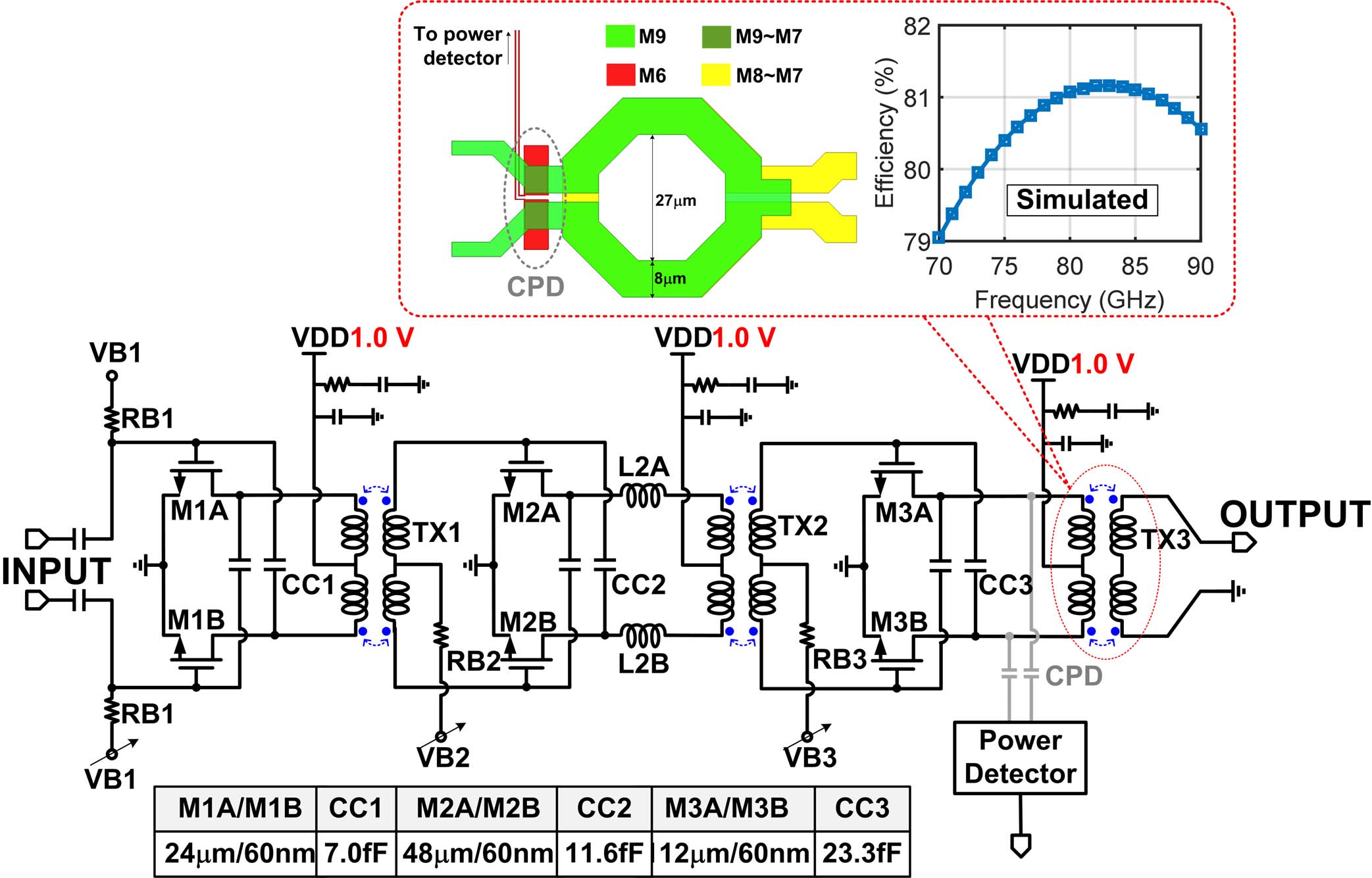

图10展示了功率放大器的原理图。它由三级共源伪差分级构成。每一级都采用了与低噪声放大器相同的中和电容技术。级间和输出阻抗匹配网络均采用基于变压器的网络实现。基于变压器的匹配网络具有紧凑的布局,并且可以通过变压器线圈的中心抽头方便地提供偏置电压。

功率放大器的输出功率可通过数字控制其偏置电压来实现可重构,以支持不同的检测范围。在高功率模式下,该功率放大器在78 GHz时的仿真饱和输出功率为14.5 dBm,最大功率附加效率为20.1%。在功率放大器的输出端集成了一

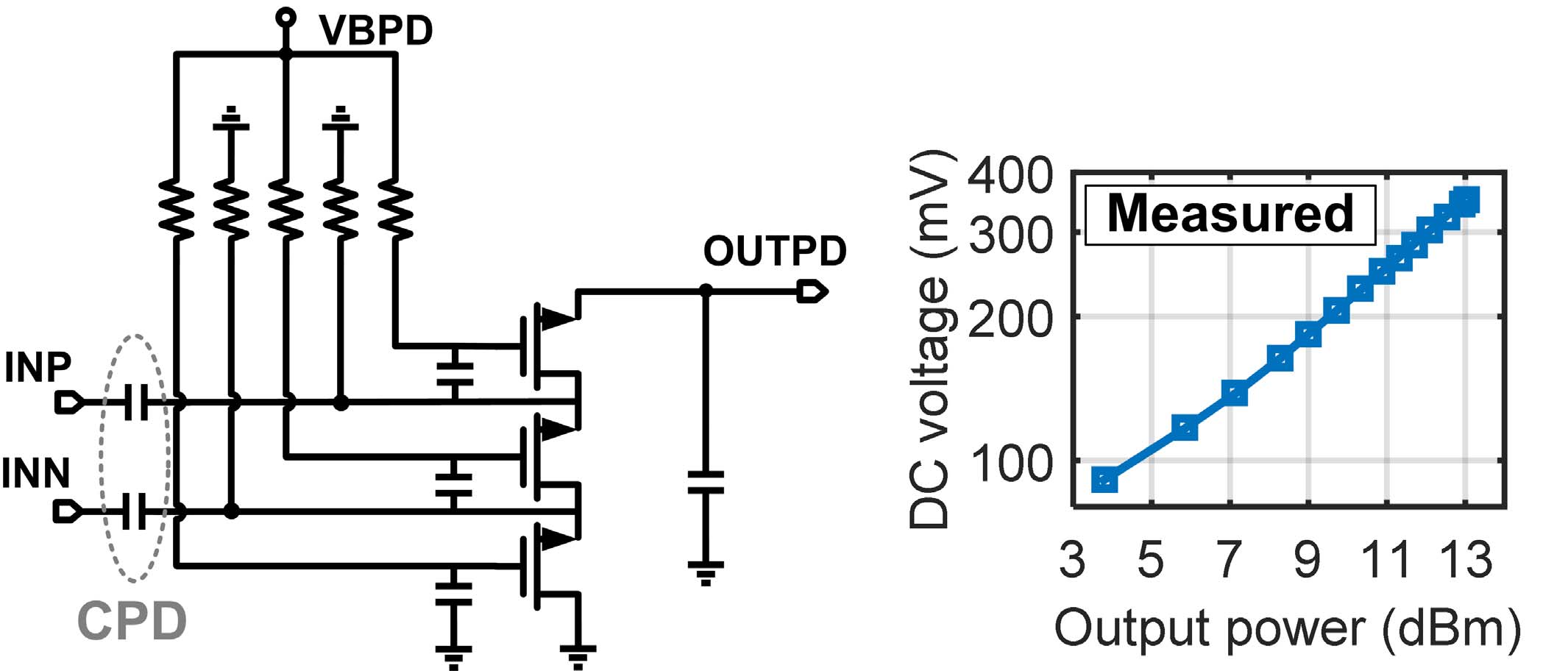

个片上功率检测器[30],以实现潜在的自适应功率控制。该功率检测器的原理图如图11所示,晶体管的漏极通过大电阻实现直流接地,而栅极端子偏置在$V_{\text{BPD}}$,该电压接近晶体管的阈值电压。因此,二极管连接的晶体管具有零有效阈值电压,从而消除了因阈值电压引起的输出电压损耗。图11还显示了功率检测器的实测直流输出电压随PA输出功率的变化情况。当PA的输出功率为9.0 dBm时,功率检测器的直流输出电压为184 mV,即使不使用额外的放大级,该电压也足以满足后处理需求。

C. 被动混频器、跨阻放大器和模拟基带

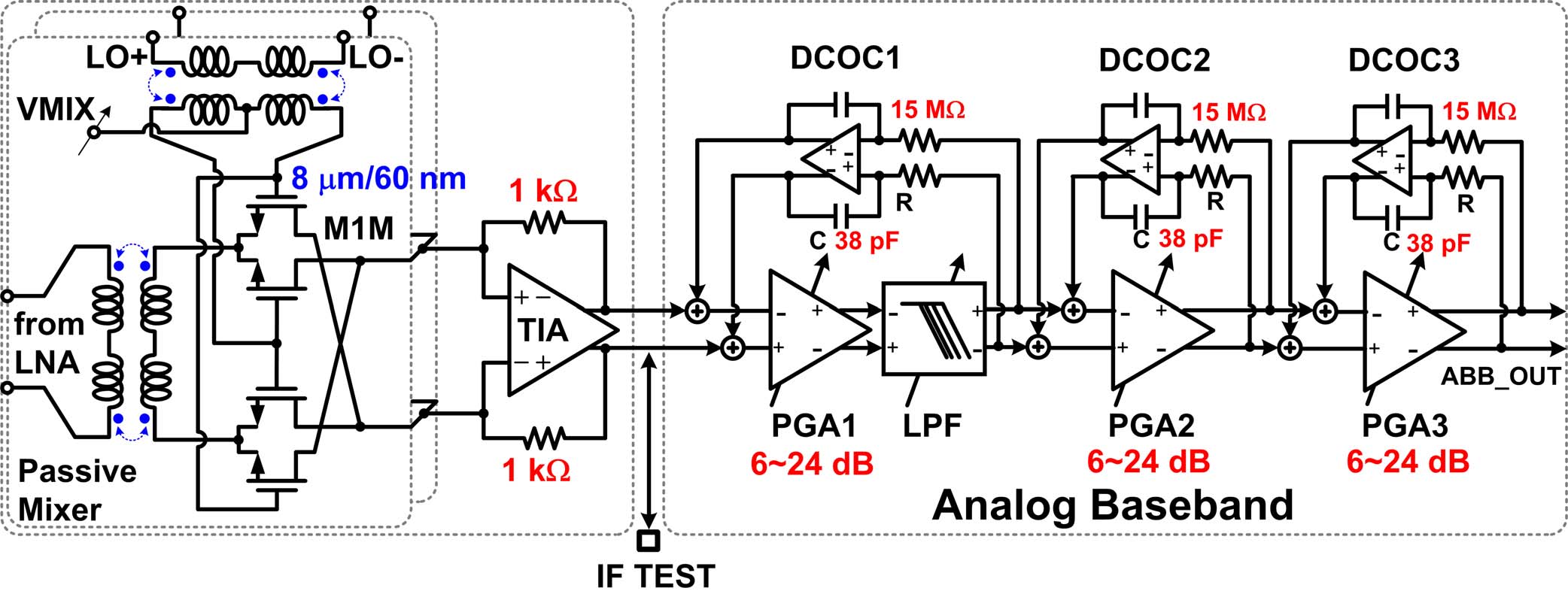

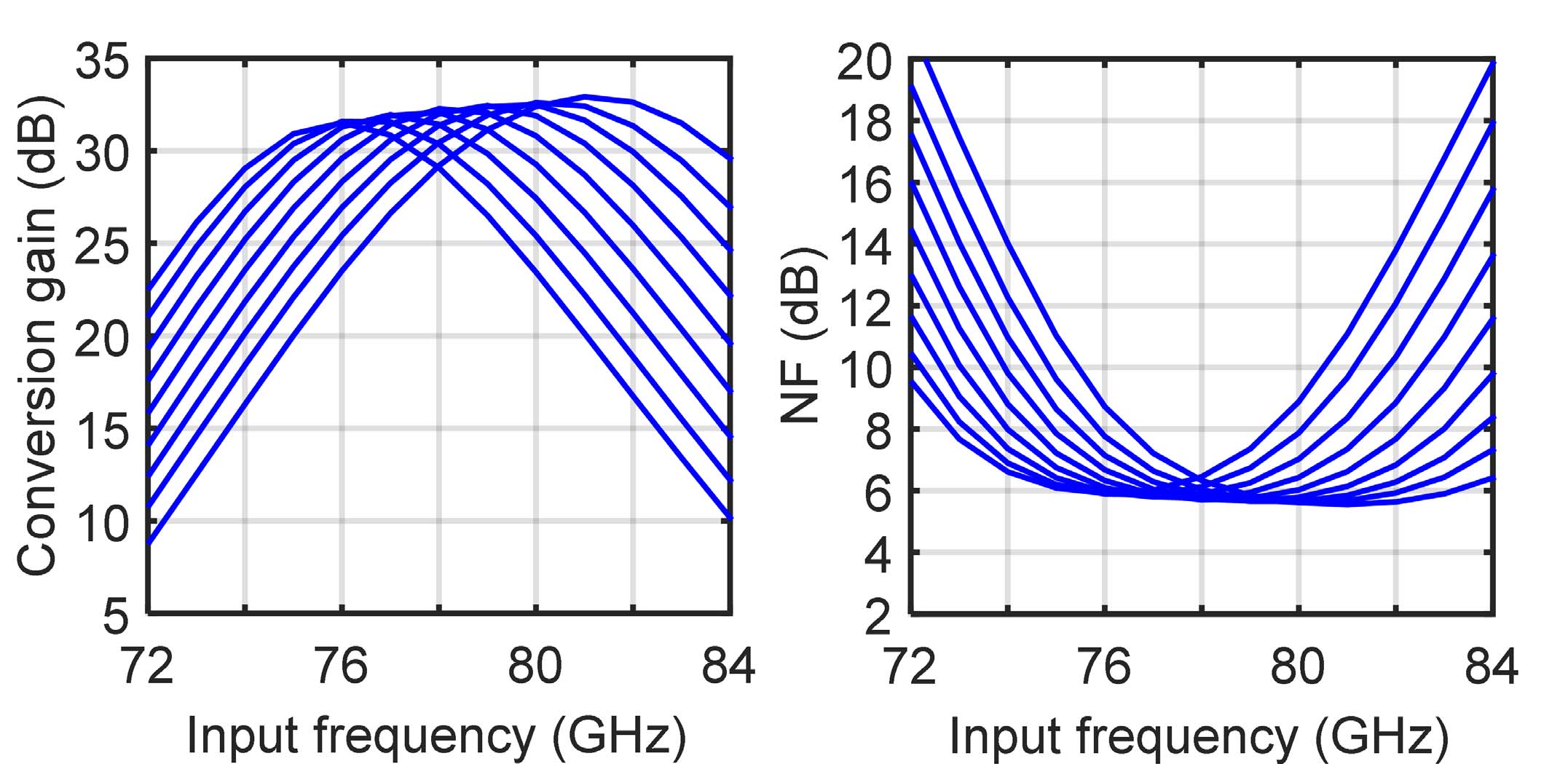

在接收路径中采用了双平衡无源电流模式混频器来实现频率转换,如图12所示。两个接收路径中混频器的电流输出被合并后连接到电阻反馈跨阻放大器(TIA)的输入端。采用无源混频器基于以下几个原因:首先,由于晶体管不承载直流电流,因此在中频输出中的闪烁噪声贡献很小。在FMCW雷达接收机中,闪烁噪声的低贡献尤为重要,因为检测到的输出中频频率可能低至数百千赫。其次,两个接收路径中无源混频器的电流输出可以在电流域直接合并,这比在电压域合并要容易得多。第三,由于无源混频器中的晶体管没有直流电流,它们可以由后续的TIA提供偏置,从而避免使用具有大时间常数的交流耦合网络。混频器中晶体管栅极的直流偏置电压由带隙提供,该电压可在0.6 V至1.0 V范围内数字调谐,以在不同本振强度下优化混频器性能。TIA将两个接收路径中无源混频器的合并输出电流转换为电压。TIA中的嵌入式放大器经过特殊设计优化以实现低闪烁噪声拐角频率以及低总噪声贡献。不同DiCAD编码下各接收链路前端(不含模拟基带)的仿真转换增益如图13(a)所示,接收机前端(不含模拟基带)的噪声系数如图13(b)所示。从仿真结果可以看出,DiCAD能够有效调节接收机的工作频率。

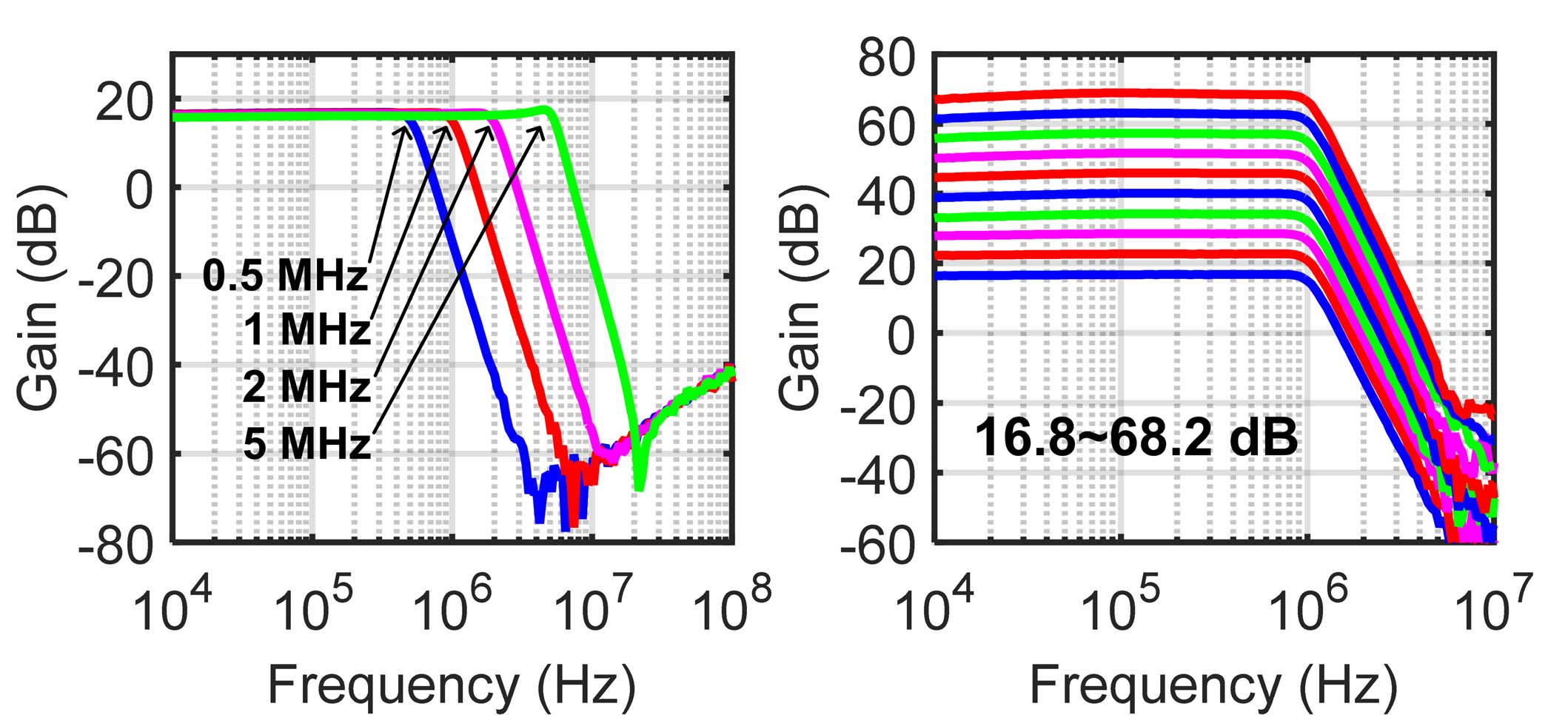

模拟基带集成在芯片上,以提供必要的动态范围和滤波功能。如图12所示,模拟基带由三级PGA、一个低通滤波器(LPF)和三个直流偏移校准(DCOC)环路组成。每级PGA提供6 dB至24 dB的可编程增益,步进为6 dB。采用电阻反馈放大器实现这三个PGA。增益通过配置反馈开关电阻阵列进行数字编程。因此,模拟基带可提供总共54 dB的动态范围。模拟基带中包含一个五阶有源RC巴特沃斯滤波器,用于滤除干扰。该滤波器的阶数选择依据是:对位于最大探测距离两倍处其他物体所产生的干扰至少衰减30 dB。为了支持不同的检测范围,可通过使用开关电阻阵列将低通滤波器的–3 dB带宽重新配置为500千赫、1 MHz、2 MHz和5兆赫。假设FMCW啁啾的斜率为1 GHz/ms,则对应于500千赫、1 MHz、2 MHz和5兆赫中频频率的可探测目标距离分别为37.5米、75米、150米和375米。集成了三个DCOC环路以消除直流偏移。仿真结果显示,在各种工艺角下,每个DCOC环路的3 dB高通截止频率均低于10千赫兹。测量结果表明,在启用DCOC环路后,直流偏移从427毫伏降低至1毫伏。

每条接收链路的转换增益和 (b) 接收机的噪声系数)

每条接收链路的转换增益和 (b) 接收机的噪声系数)

IV. 测量结果

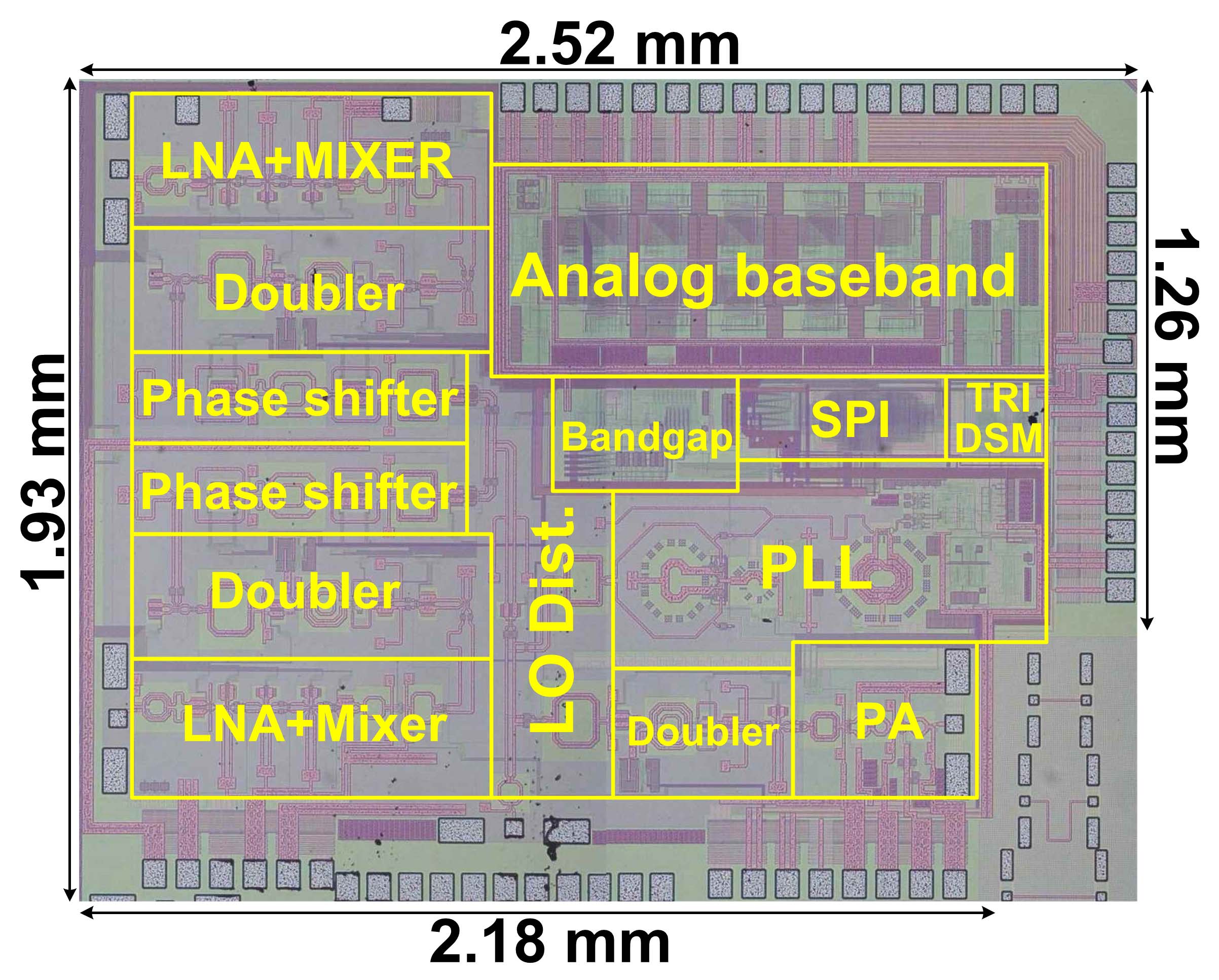

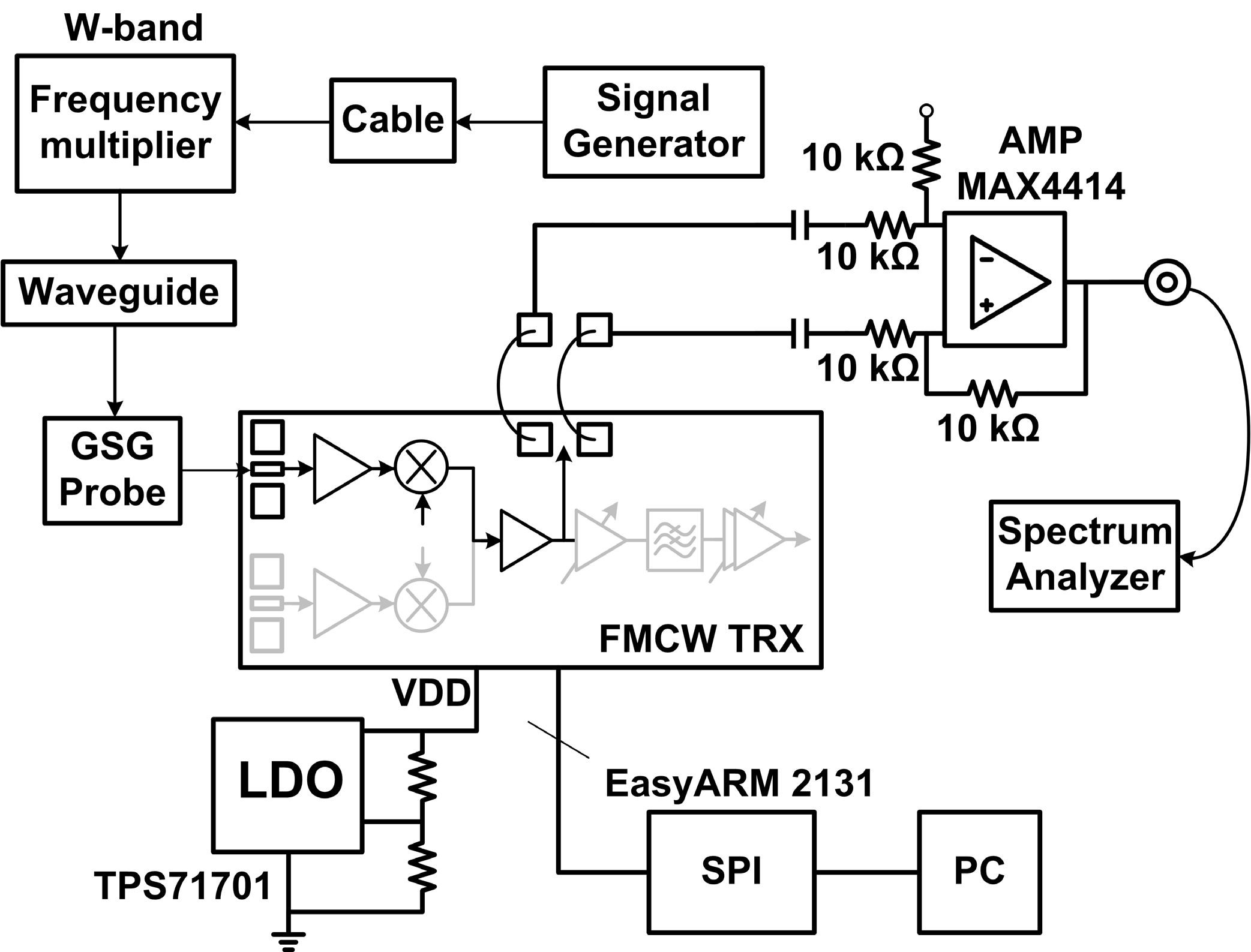

所提出的FMCW收发器已在65 nm CMOS工艺中实现。芯片的显微照片如图14所示。芯片面积为4.64 mm²,包含所有焊盘。功耗大的功率放大器被放置在远离敏感的接收前端的位置。在测量过程中,毫米波信号的焊盘通过探针台在片上进行探测,而其他焊盘则通过引线键合连接到印刷电路板。由ARM开发板通过计算机控制计算机通过SPI接口与芯片通信。

FMCW信号发生器:

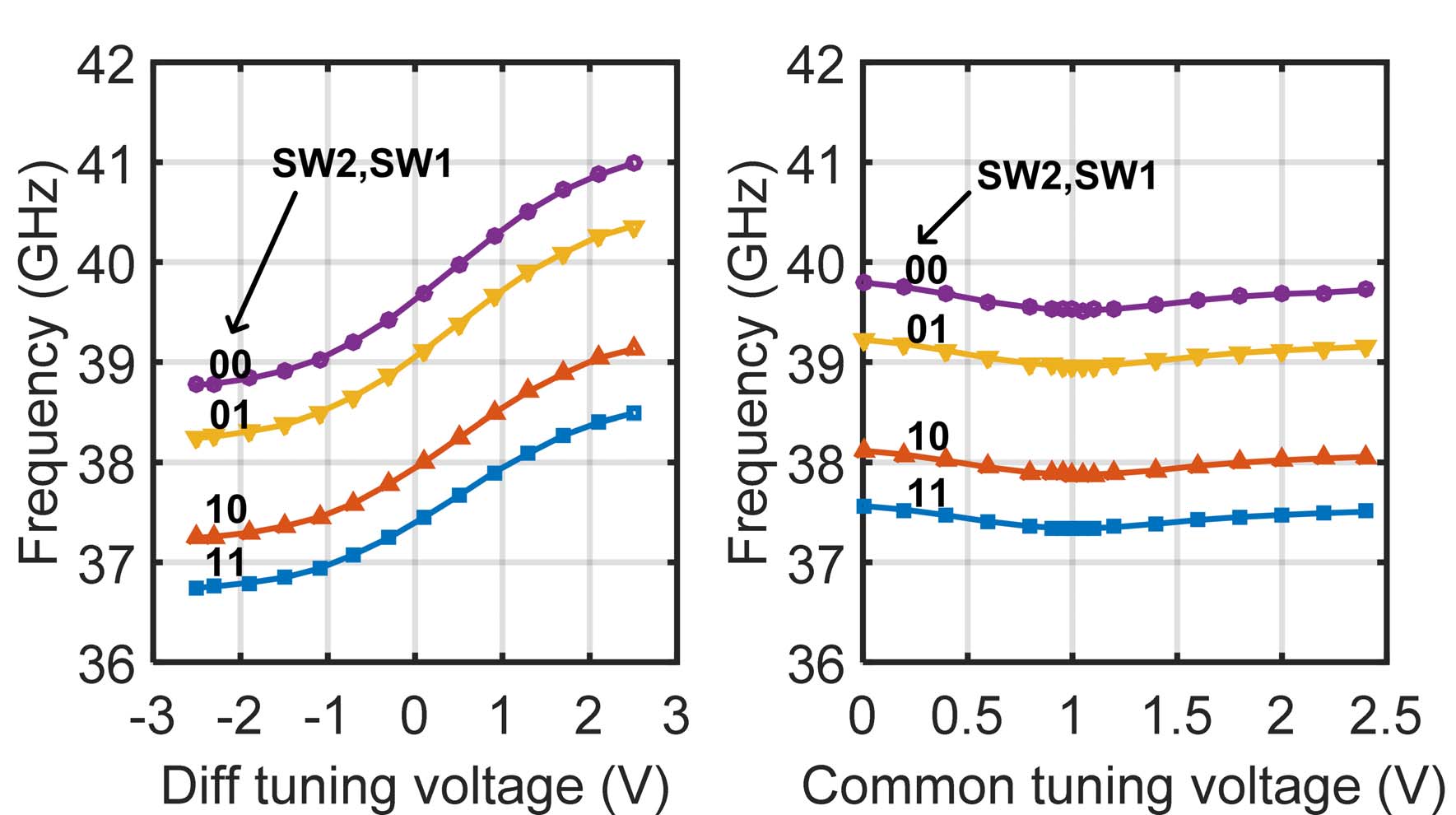

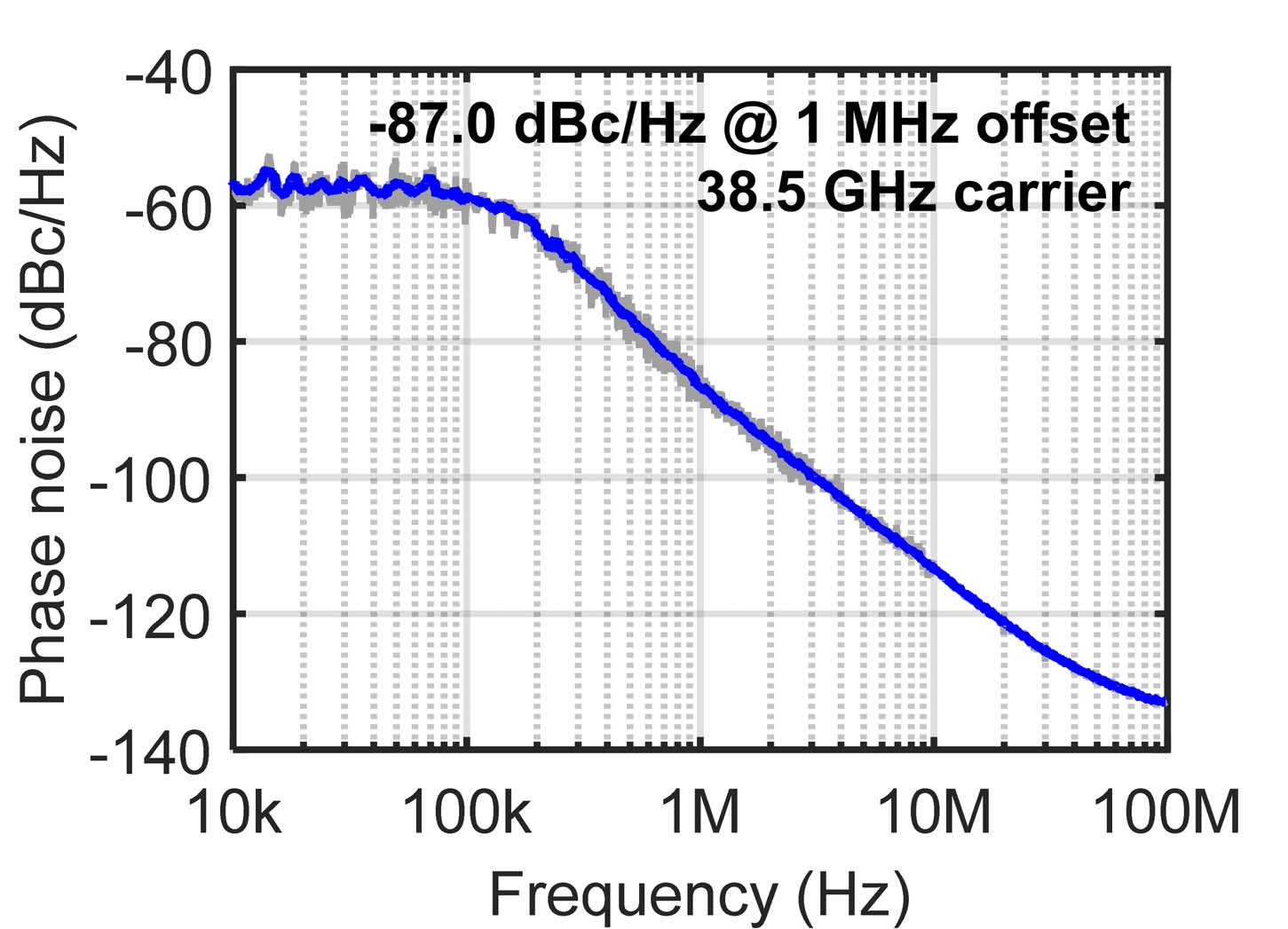

测量了差分VCO的共模和差模调谐范围,结果如图15所示。四条子调谐曲线中的每一条均覆盖1.8至2.1 GHz的频率调谐范围,整个频率调谐范围为36.7至41.0 GHz。由于每条调谐曲线必须覆盖设计的FMCW线性调频范围,并且在FMCW啁啾周期内不允许在调谐曲线之间切换,因此VCO的增益较高。当共模电压为1.0伏特时,共模增益接近零,这意味着VCO对调谐端口的共模噪声不敏感。当分数‐N PLL频率合成器锁定时,通过本振测试端口测量相位噪声性能,如图16所示。载波频率为37.4 GHz和38.5 GHz时,在1 MHz偏移处的相位噪声分别为‐89.6 dBc/Hz和‐87.0 dBc/Hz。

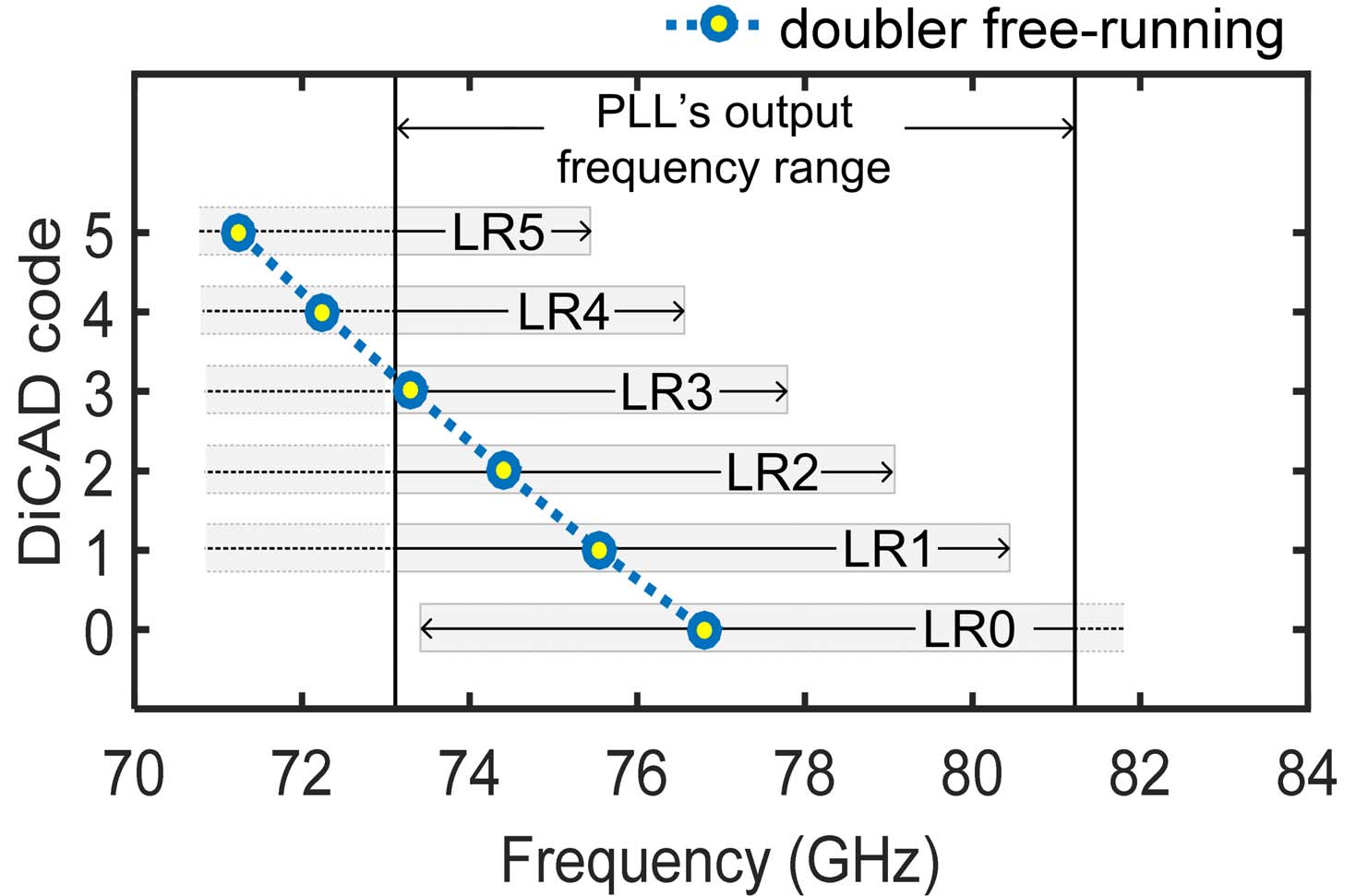

当分数‐N PLL频率合成器断电时,从功率放大器的输出端测量注入锁定倍频器的自由运行频率。如图17所示,当DiCAD传输线(图6中的DTL1)的控制码从0变化到5时,自由运行频率在71.3至76.8 GHz之间变化。在测得自由运行频率后,将分数‐N PLL频率合成器上电,以提供输入注入信号来测量注入锁定的锁定范围倍频器。由于合成器的输出频率范围有限,无法完全测量该倍频器的锁定范围。当DiCAD码为0、1或2时,锁定范围覆盖77至79 GHz的频率。由于测量设备限制以及整个系统的高集成度,无法直接测量倍频器的谐波抑制比。单独对倍频器进行仿真得到的四次谐波和六次谐波的仿真谐波抑制比分别为47.7 dBc和42.1 dBc。在倍频器核心(交叉耦合晶体管对的漏极)和倍频器的输出缓冲器处,仿真的单端峰峰值电压分别约为1.1伏特和0.7伏特,足以驱动功率放大器接近其饱和点。

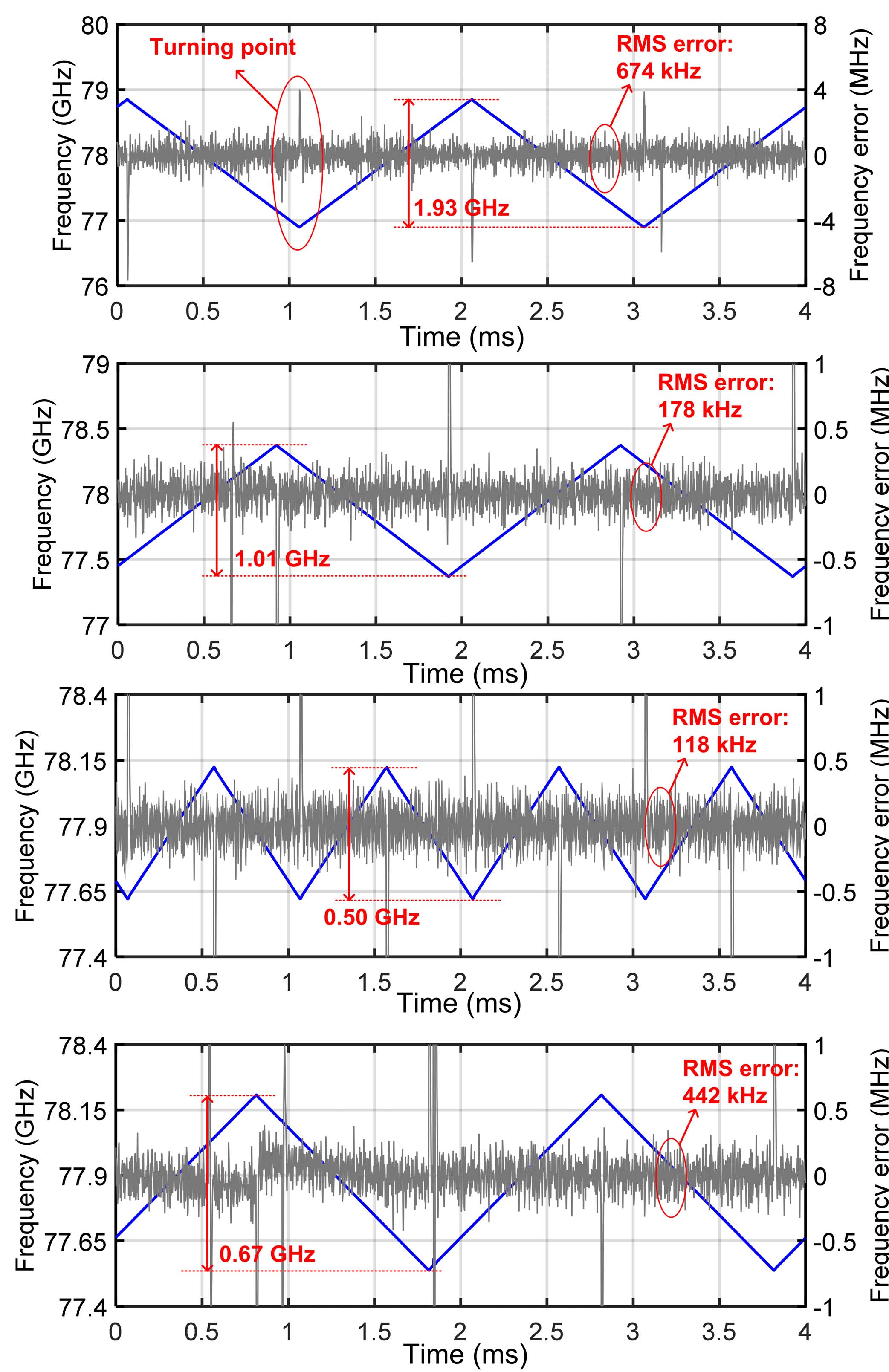

使用罗德与施瓦茨 FSW 信号与频谱分析仪,在锁相环的8分频测试端口测量瞬态调频连续波啁啾信号,其频率约为4.8 GHz。图18显示了经解调的FMCW频率‐时间波形以及频率误差,其中误差值已乘以16。啁啾带宽和斜率均为可重构。对于带宽为0.5吉赫兹、周期为1毫秒的啁啾信号,其均方根频率误差为118千赫兹;而对于带宽为1.93吉赫兹、周期为2毫秒的啁啾信号,其均方根频率误差为674千赫兹。1.93吉赫兹的啁啾带宽范围为76.92至78.85吉赫兹,通过配置三角波发生器的初始值,可轻松将其调整至77 GHz以上。

发射机:

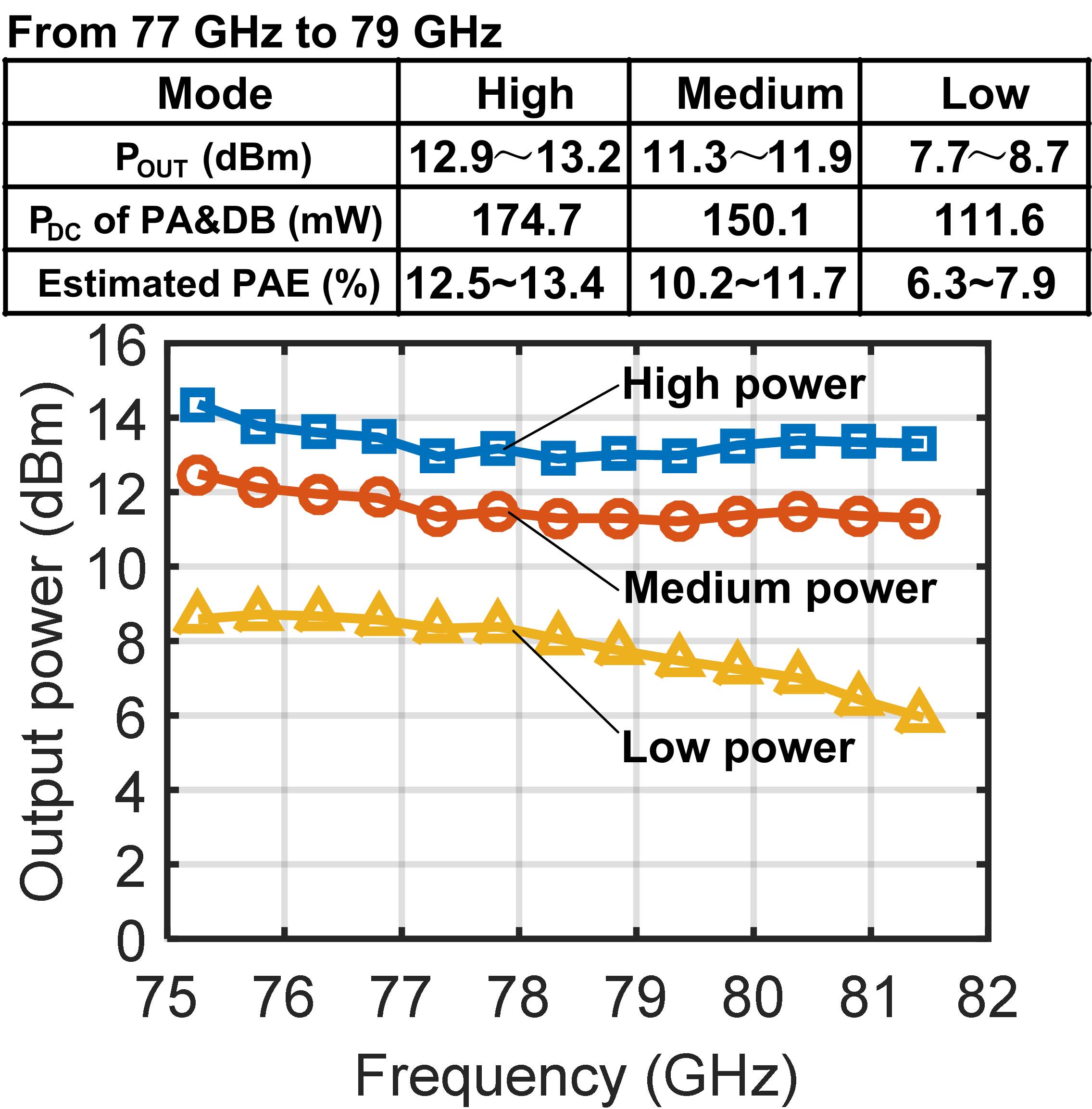

使用W波段功率传感器和功率计。已对W波段探针和波导的插入损耗进行了校准。如前所述,可通过改变偏置电压对功率放大器的输出功率进行数字可重构,以支持不同的检测范围。当功率放大器工作在高功率模式时,在75.3 GHz处的最大输出功率为14.4 dBm。在77至79 GHz频段内的输出功率为12.9至13.2 dBm,表现出较高的增益平坦度。由于功率放大器、倍频器以及二者之间缓冲器的电源在片上连接在一起,因此这些模块必须同时工作,从而无法直接测量功率放大器的输出功率和功率附加效率(PAE)。然而,PAE可通过输出功率和功耗推算得出。接收机中倍频器的功耗为7.4 mW,假设发射机中的倍频器功耗相同。倍频器与功率放大器之间的缓冲器功耗根据仿真结果为10.8 mW。假设功率放大器的增益足够高,则PAE可通过输出功率与功率放大器功耗的比值估算。当功率放大器工作在高功率模式时,PAE在频率范围内为12.5%∼ 13.4%。在75.3 GHz时,最大功率附加效率约为17.6%。图19中的表格显示了在不同模式下测得的输出功率、功耗以及估算的功率附加效率。当功率放大器从高功率模式可重构为低功率模式时,功耗节省了63.1 mW。

接收机:

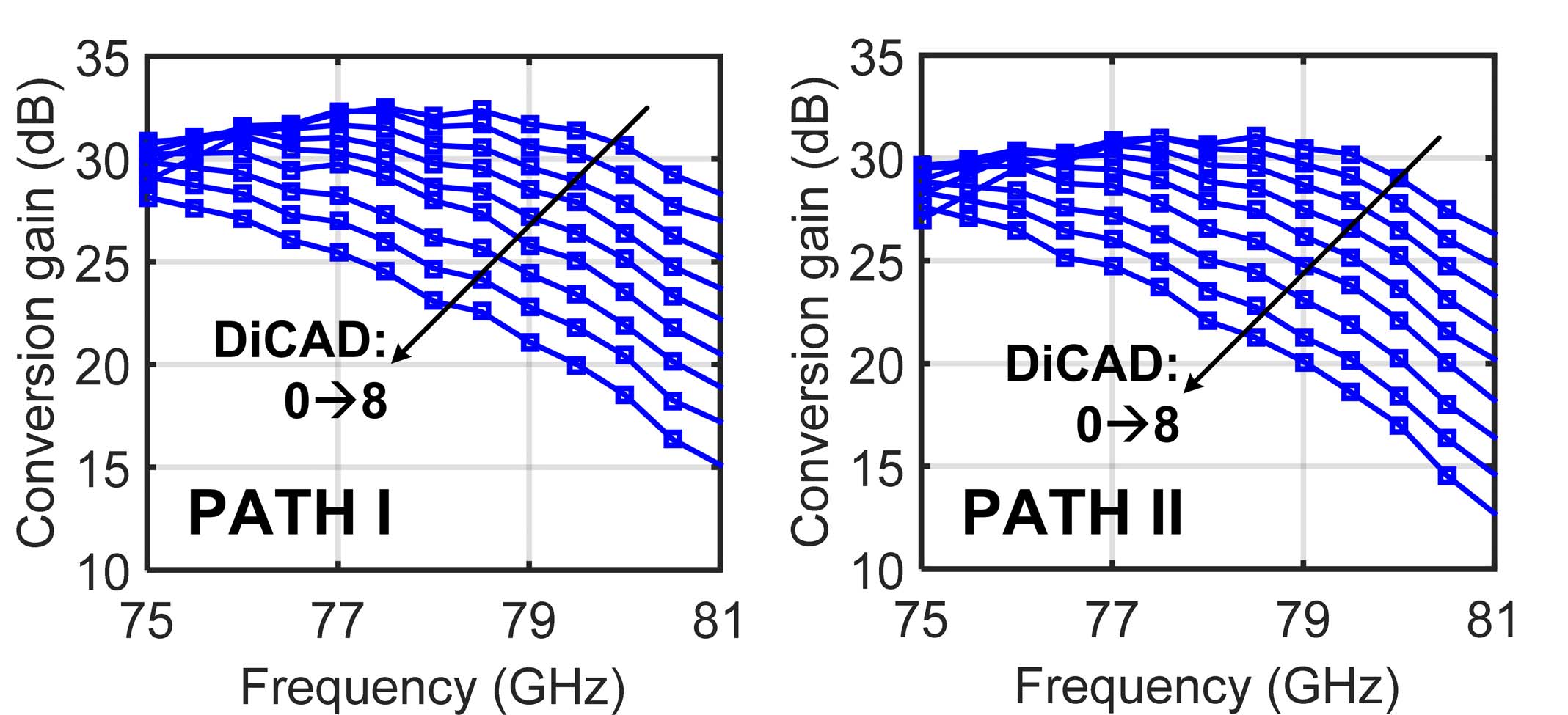

图20显示了对接收机前端转换增益的测量设置。由信号发生器和外部W波段频率倍增器产生的输入信号通过片上探测施加到接收机输入端。中频信号从TIA输出端测量得到。当测量一条接收链路时,另一条路径和模拟基带均断电。图21显示了不同DiCAD编码下各接收前端路径的测得的转换增益。通过配置DiCAD编码,可有效校准工作频率(峰值增益频率),以避免因工艺电压温度变化引起的频率漂移。第一和第二接收前端路径的峰值增益分别为32.5 dB和31.0 dB。实测频率相较于仿真结果。得益于DiCAD传输线,FMCW啁啾频率扫描范围仍被覆盖。同时测量了模拟基带的增益和低通滤波特性。图22显示了当PGA设置为最小增益时的五阶低通滤波特性,以及当低通滤波带宽设置为1 MHz时的增益。增益可在16.8分贝至68.2分贝之间可编程,而低通滤波带宽可重构为500千赫、1 MHz、2 MHz或5兆赫。

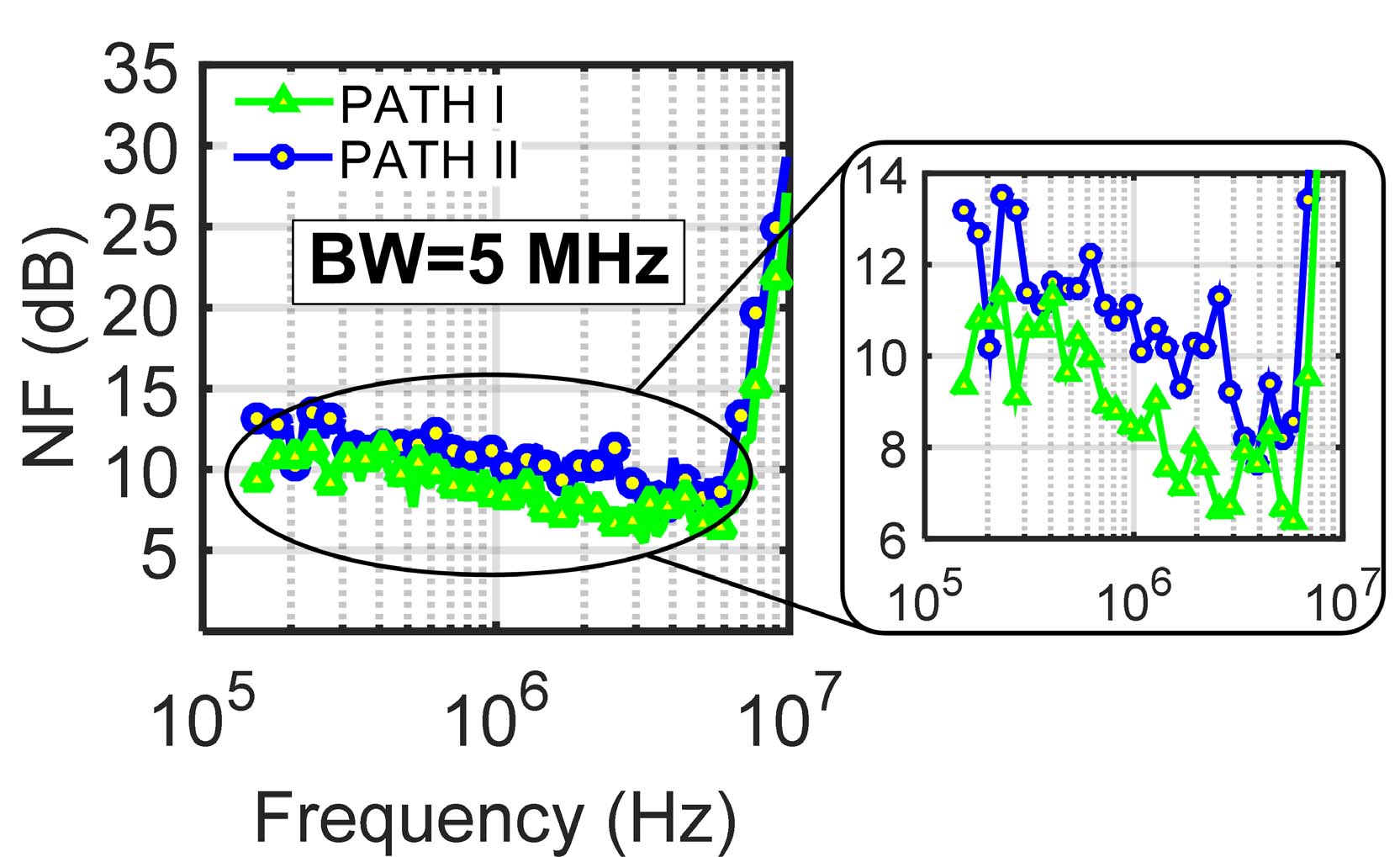

使用增益法测量接收机的噪声系数。在测量中,模拟基带被启用并设置为其最大增益。当带宽为5兆赫时,结果如图23所示。在3.33兆赫中频频率下,第一条和第二条接收路径的噪声系数分别为7.9分贝和8.2分贝。由于中频带宽限制,在5兆赫以上的频率处噪声系数急剧增加。两条接收路径之间的性能差异可能源于无源混频器的非对称本振分布和电流输出布线。当两条接收路径同时工作时,通过以下方程估算在3.33兆赫下的有效噪声系数为5.04分贝:

$$ NF_{\text{eff}} = 20 \log\left( \frac{\sqrt{A_1^2 F_1 + A_2^2 F_2}}{A_1 + A_2} \right) $$

其中$A_1$和$A_2$是两条接收路径的电压增益,$F_1$和$F_2$是噪声系数。(14)的推导见附录。由于计算方程的更新,有效噪声系数与[13]不同。

一个独立移相器也已流片,用于测量其移相性能。测得的不同粗调DiCAD码下的S21幅度和相位如图24所示。S21幅度在38∼40吉赫兹范围内大致相互重叠,仅最后三条曲线除外,这意味着在不同移相值下的增益变化较小。当粗调码从0变为8时,移相范围大于90度,同时在38∼40吉赫兹范围内的增益变化小于1分贝。当粗调码从0变为8时,相位误差在3.7至5.1度之间。假设每个接收路径使用全向天线,双接收路径的天线方向图由独立移相器测得的转换增益和移相值计算得出。结果如图25所示,与理想的双路相控阵阵列天线方向图相近。测得的独立移相器(带细调码)的相位分辨率为4度,对应于波束方向1.3度的分辨率。

主要功能模块以及整个芯片的电源电压和功耗总结于表I中。模拟基带由1.2V电源供电,以简化设计并提高线性度。模拟基带中的主要晶体管为标称器件,而关断控制开关则采用具有较高击穿电压的厚栅晶体管,从而确保即使在1.2V电源下也能安全工作。整个芯片的总功耗为343毫瓦,其中发射机中的功率放大器和倍频器消耗174.7毫瓦,超过总功耗的一半。FMCW收发器的性能在表II中进行了总结,并与CMOS工艺下的其他类似工作进行了比较。在这些工作中,该收发器实现了最高集成度和最宽带宽啁啾。它还实现了最高的输出功率,从而降低了对天线增益和接收机灵敏度的要求。其功耗高于[5]和[8]的主要原因是输出功率更高。考虑到更高的集成度和更高的输出功率,该收发器的能效具有竞争力。

V. 结论

本文提出了一种用于汽车雷达应用的完全集成77 GHz频率倍增双路相控阵FMCW收发器。该倍频方案降低了基本FMCW信号发生器的工作频率,提高了啁啾带宽,减小了移相器所需的相移覆盖范围,并降低了本振分配网络的插入损耗。采用了多种电路技术以提升收发器性能。整个FMCW收发器已在65 nm CMOS工艺中实现。其最大啁啾带宽达到1.93吉赫兹,最大发射功率为12.9∼13.2 dBm,可编程接收转换增益为47.8∼100.7 dB,总功耗为343毫瓦。所展示的FMCW收发器为汽车雷达应用提供了一种低成本解决方案。

表I 各模块的电源电压和功耗汇总

| 模块 | 电源电压 (V) | 功耗 (mW) |

|---|---|---|

| FMCW信号发生器 | 1.2 | 68.3 |

| 发射机(PA + 倍频器 + 缓冲器) | 1.2 | 174.7 |

| 接收机(LNA + 混频器 + 倍频器 + 缓冲器) | 1.2 | 55.7 |

| 模拟基带 | 1.2 | 44.3 |

| 总计 | — | 343.0 |

表II 性能总结与比较

| 参数 | 本文 | [5] | [8] | [11] | [12] |

|---|---|---|---|---|---|

| 工艺 (nm) | 65 | 65 | 90 | 65 | 40 |

2919

2919

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?