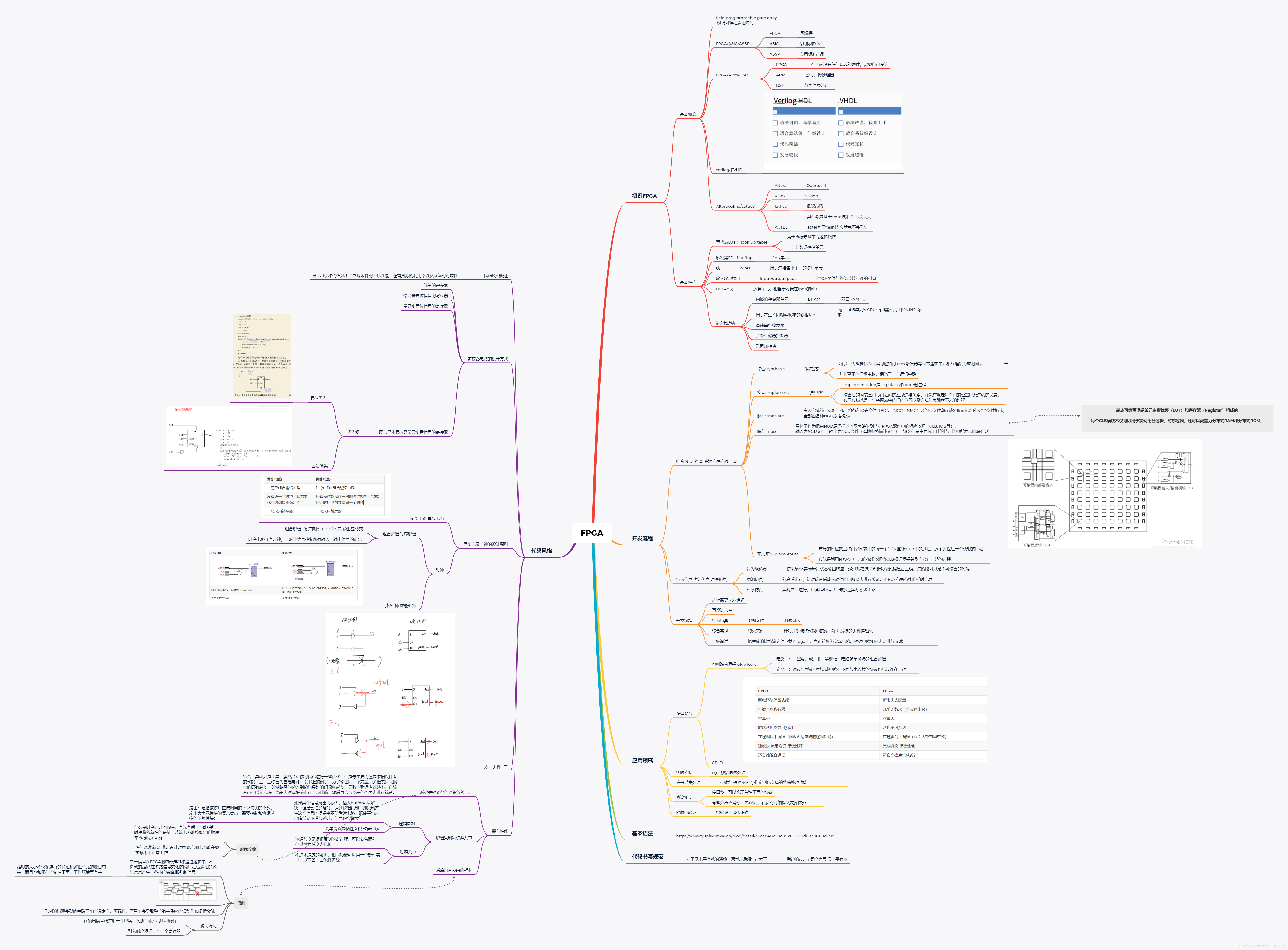

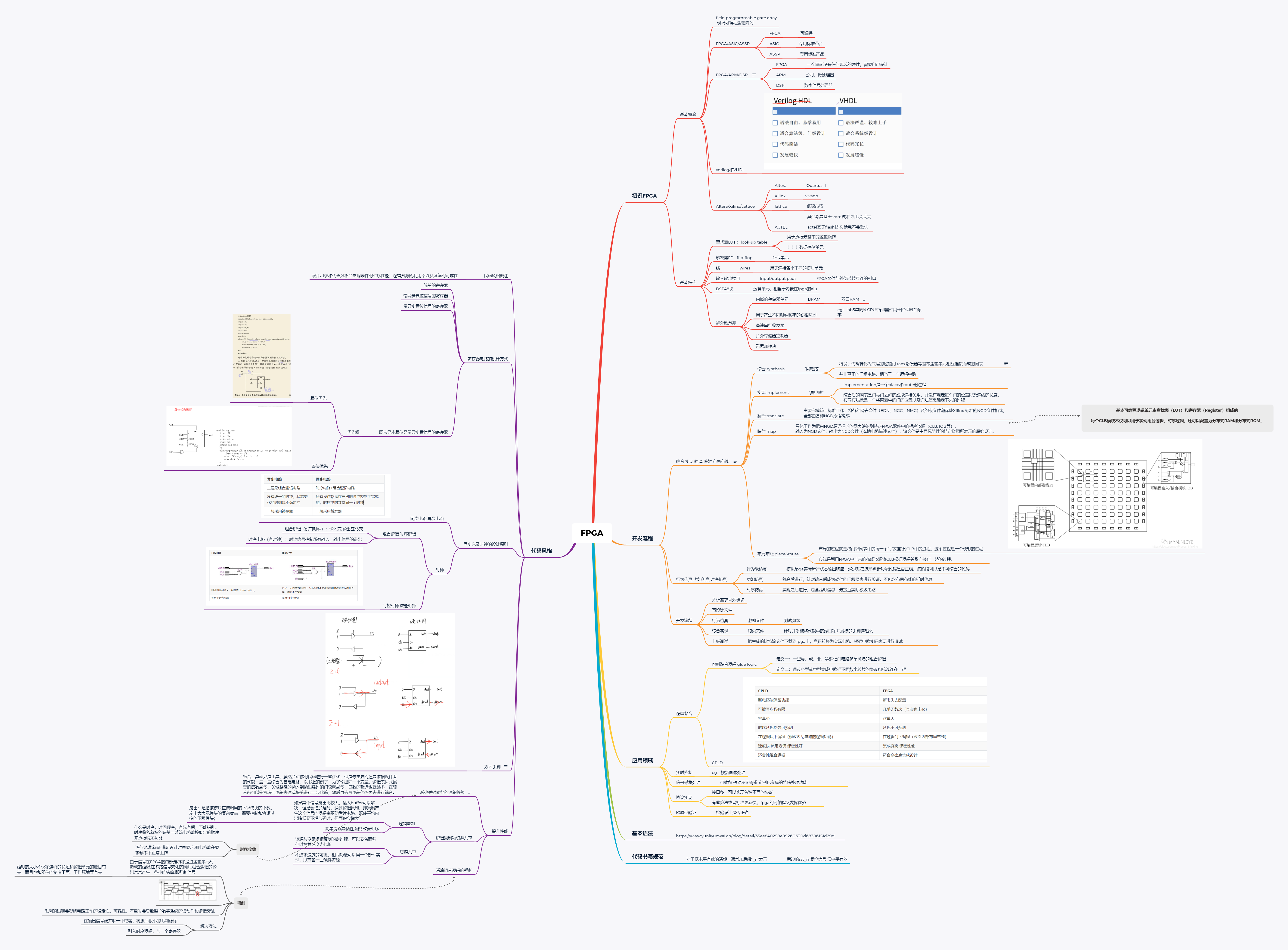

建议下载下来放大看

初识FPGA

基本概念

-

field programmable gate array

现场可编程逻辑阵列 -

FPGA/ASIC/ASSP

-

FPGA

- 可编程

-

ASIC

- 专用标准芯片

-

ASSP

- 专用标准产品

-

-

FPGA/ARM/DSP

都是可编程的

三者的区别

https://blog.youkuaiyun.com/woshiyuzhoushizhe/article/details/102815561 -

FPGA/ARM/DSP

-

FPGA

- 一个里面没有任何现成的硬件,需要自己设计

-

ARM

- 公司,微处理器

-

DSP

- 数字信号处理器

-

-

verilog和VHDL

-

Altera/Xilinx/Lattice

-

Altera

- Quartus II

-

Xilinx

- vivado

-

lattice

- 低端市场

-

ACTEL

- 其他都是基于sram技术 断电会丢失

actel基于flash技术 断电不会丢失

-

基本结构

-

查找表L

本文深入解析了FPGA的基本概念,如与ASIC和ASSP的区别,介绍了Verilog和VHDL语言,展示了Altera、Xilinx和Lattice等品牌在市场中的角色。开发流程包括综合、实现、映射和布局布线,以及时序仿真和资源利用策略。重点讲解了逻辑复制、资源共享和毛刺消除技巧。

本文深入解析了FPGA的基本概念,如与ASIC和ASSP的区别,介绍了Verilog和VHDL语言,展示了Altera、Xilinx和Lattice等品牌在市场中的角色。开发流程包括综合、实现、映射和布局布线,以及时序仿真和资源利用策略。重点讲解了逻辑复制、资源共享和毛刺消除技巧。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1467

1467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?