实验一、用1个拨码开关控制所有的LED灯亮灭

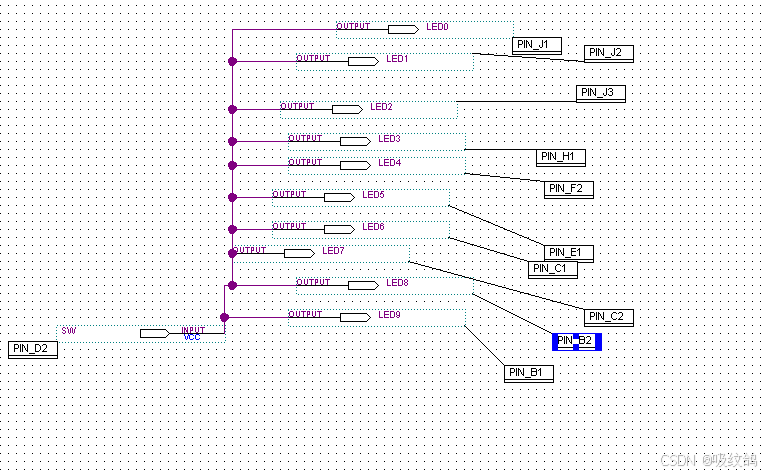

BDF文件图

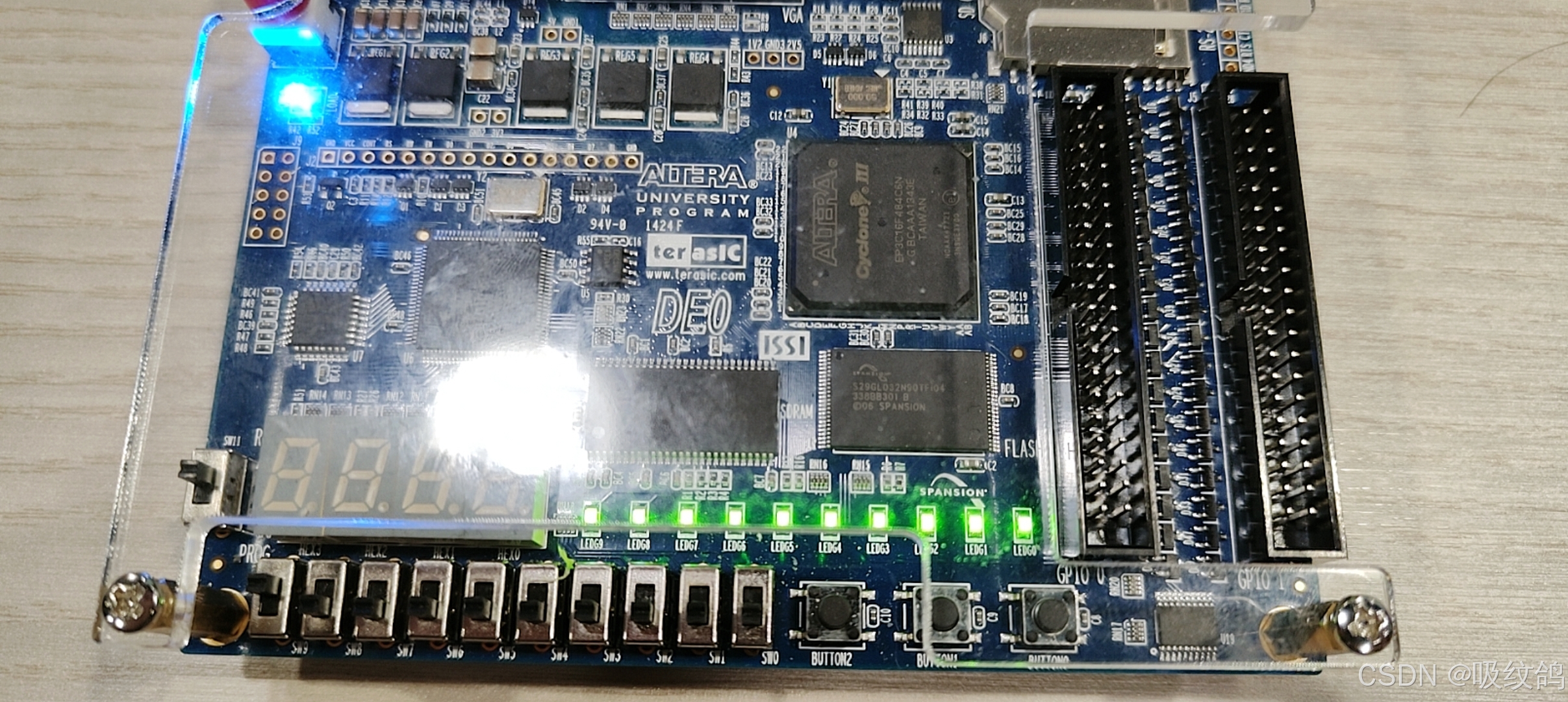

实验结果

实验结果

实验二

1.放置2个2-4译码器模块,则总共有2组SW, 每组2个,2组LED,每组4个,每组SW分别控 制其对应的LED组

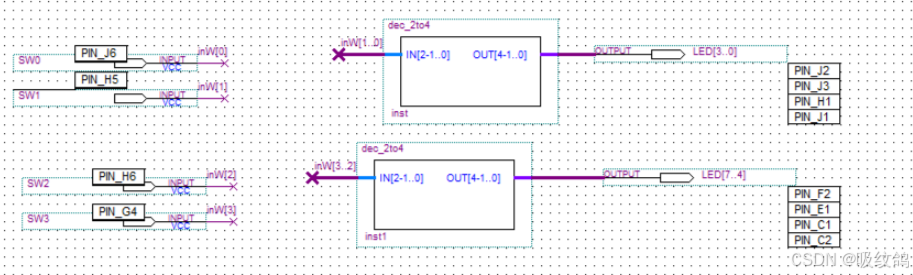

BDF如下图所示

2.参照代码,设计一个3-8译码器,完成类似 的拨码开关实验。注意代码中的信号宽度设定。

28译码器的代码如下图所示

module dec_3to8(

IN,

OUT

);

input [3-1:0] IN;

output [8-1:0] OUT;

reg [8-1:0]OUT;

always @(IN)begin

case(IN)

3'b000: OUT=8'b00_000_001;

3'b001: OUT=8'b00_000_010;

3'b010: OUT=8'b00_000_100;

3'b011: OUT=8'b00_001_000;

3'b100: OUT=8'b00_010_000;

3'b101: OUT=8'b00_100_000;

3'b110: OUT=8'b01_000_000;

3'b111: OUT=8'b10_000_000;

endcase

end

endmodule

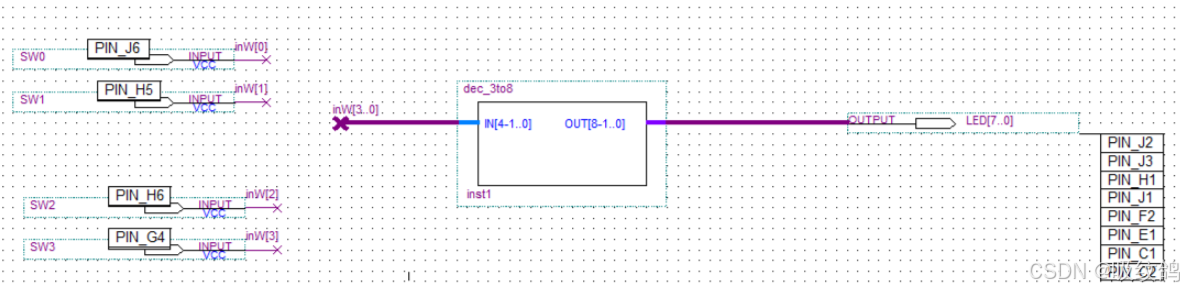

BDF图如下图所示

3.自行查阅手册中的7段译码器管脚对应关系, 用4个拨码开关控制一个7段译码器的数字,从 0-9-A-F,共16个数字和字母。

此实验需要一个4 7译码器帮助实现,实现47译码器的实现代码如下图所示:

module dec_4to7(

IN,

OUT

);

input [4-1:0] IN;

output [7-1:0] OUT;

reg [7-1:0]OUT;

always @(IN)begin

case(IN)

4'b0000: OUT=7'b1_000_000;//0

4'b0001: OUT=7'b1_111_001;//1

4'b0010: OUT=7'b0_100_100;//2

4'b0011: OUT=7'b0_110_000;//3

4'b0100: OUT=7'b0_011_001;//4

4'b0101: OUT=7'b0_010_010;//5

4'b0110: OUT=7'b0_000_010;//6

4'b0111: OUT=7'b1_111_000;//7

4'b1000: OUT=7'b0_000_000;//8

4'b1001: OUT=7'b0_010_000;//9

4'b1010: OUT=7'b0_001_000;//A

4'b1011: OUT=7'b0_000_011;//B

4'b1100: OUT=7'b1_000_110;//C

4'b1101: OUT=7'b0_100_001;//D

4'b1110: OUT=7'b0_000_110;//E

4'b1111: OUT=7'b0_001_110;//F

endcase

end

endmodule

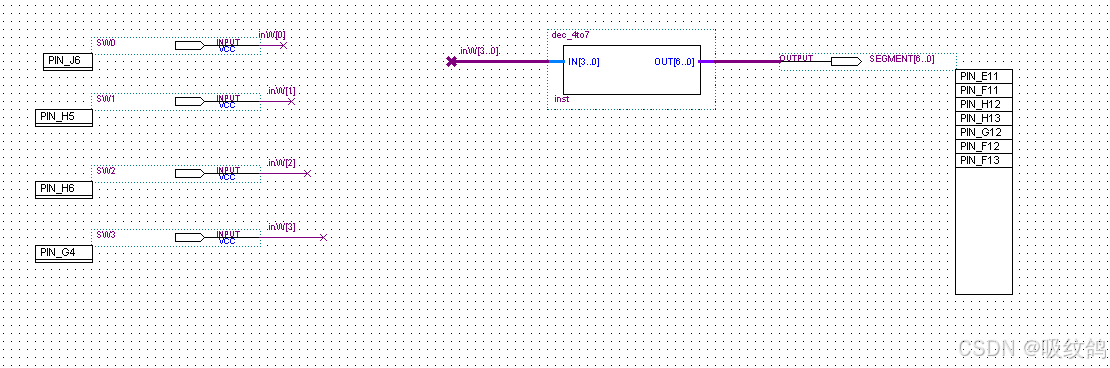

BDF文件如下图所示

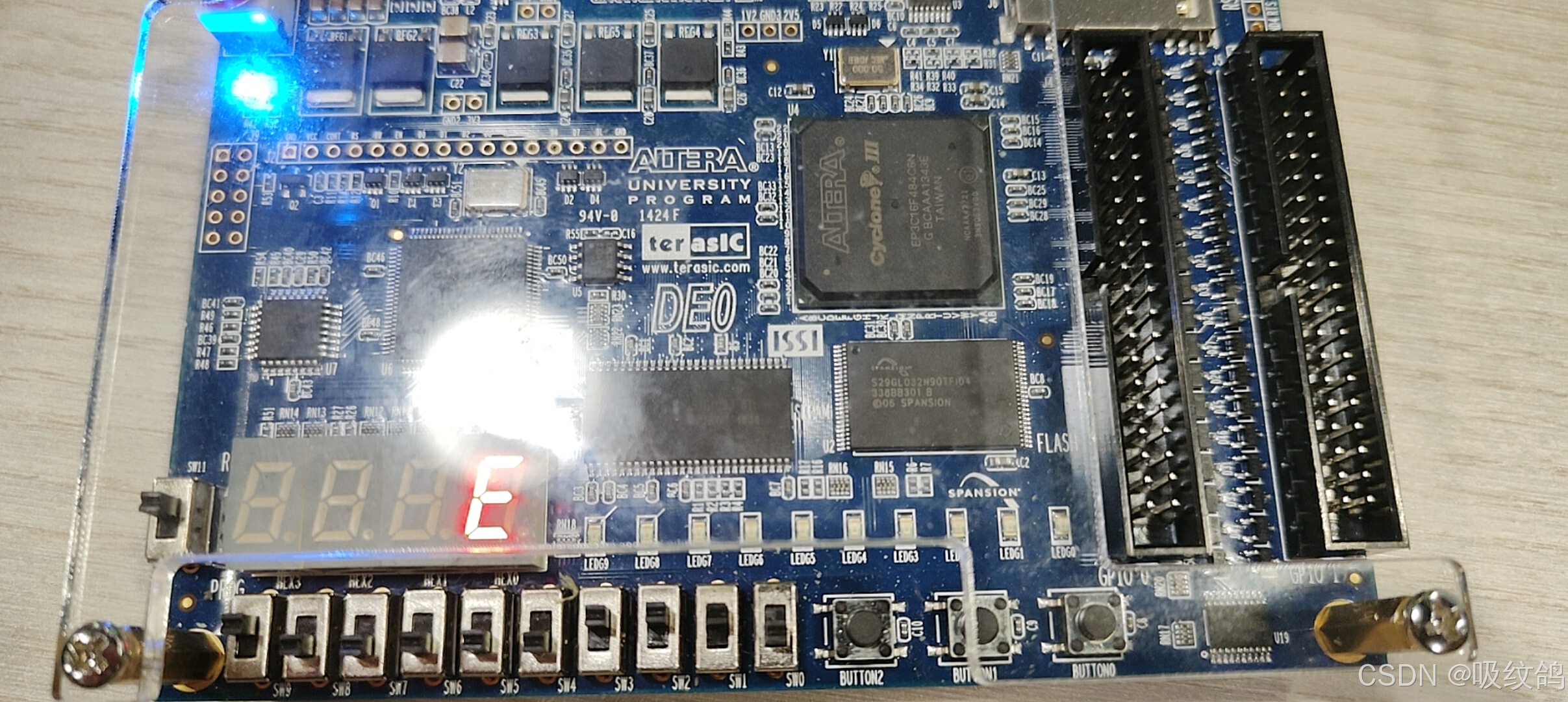

、实验现象

、实验现象

实验三

1.参照代码,设计一个0-17的计数器,当 计数值为17的时候,OV输出1,其他输出0, 注意设定合理的信号位宽。

0-17的计数器代码如下

module rtl_module(

CLK,

CNTVAL,

OV

);

input CLK;

output [5-1:0]CNTVAL;

output OV;

reg [5-1:0]CNTVAL;

reg OV;

parameter cntmax=17;

always @(posedge CLK)begin

if(CNTVAL>=cntmax)begin

CNTVAL<=0;

end

else begin

CNTVAL<=CNTVAL+1'b1;

end

end

always @(CNTVAL)begin

if(CNTVAL==cntmax)begin

OV=1;

end

else begin

OV=0;

end

end

endmodule

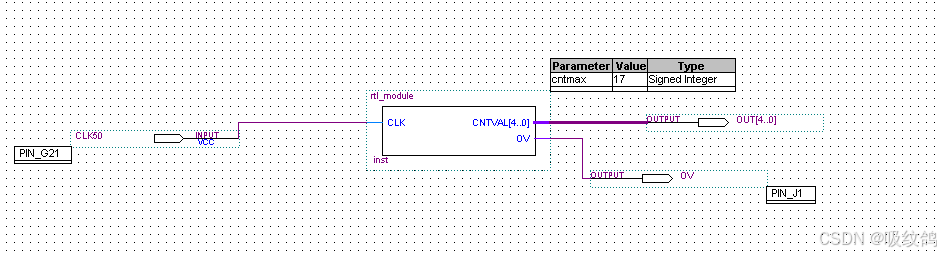

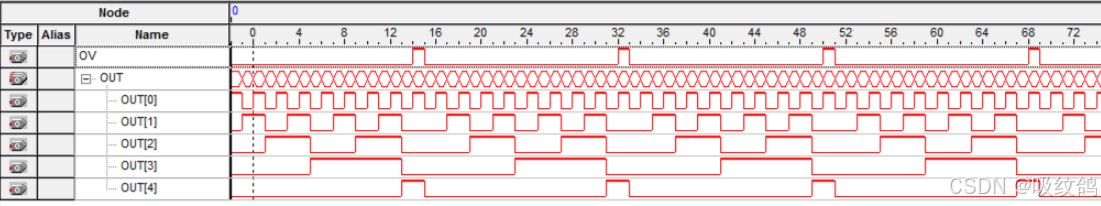

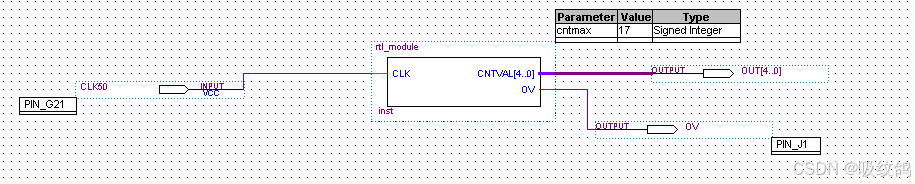

BDF文件如下:

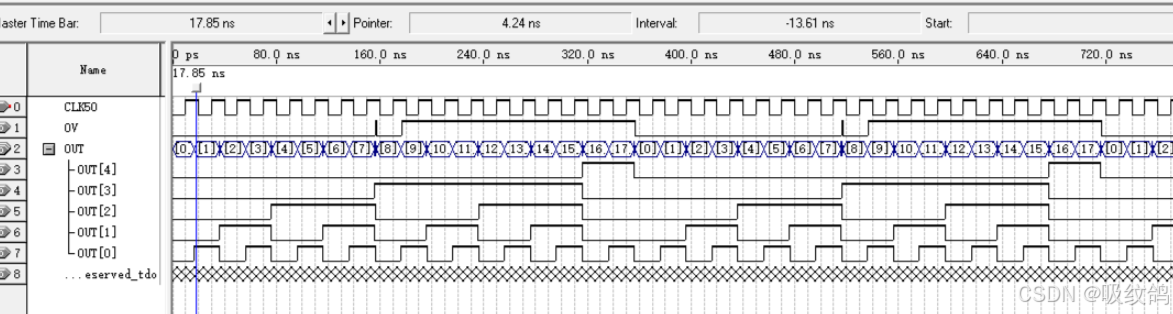

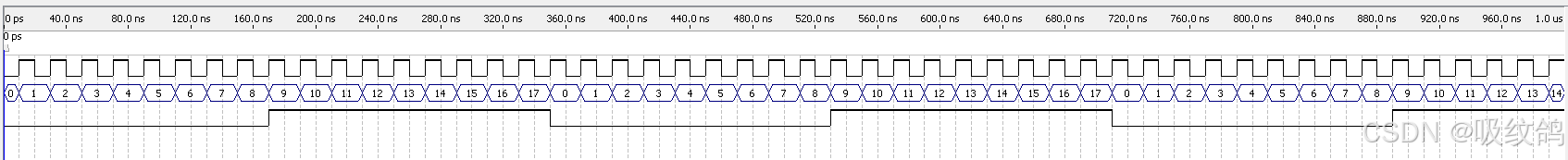

仿真图

signaltap抓取图

问题:观察毛刺,为什么会有毛刺?

运行仿真,把波形时域展宽,可以看到,3和4之间还有5, 而2、3之间没有别的数目,因为过渡状态的原因。从3过度到4,二进制代码从011到101到100,而2到3可以直接从010到011。

2.针对以上计数器,修改输出逻辑,当计 数值为0-8时,OV输出0,9-17时OV输出1

实验代码

module rtl_module(

CLK,

CNTVAL,

OV

);

input CLK;

output [5-1:0]CNTVAL;

output OV;

reg [5-1:0]CNTVAL;

reg OV;

parameter cntmax=17;

always @(posedge CLK)begin

if(CNTVAL>=cntmax)begin

CNTVAL<=0;

end

else begin

CNTVAL<=CNTVAL+1'b1;

end

end

always @(CNTVAL)begin

if(CNTVAL<=cntmax&&CNTVAL>=9)begin

OV=1;

end

else begin

OV=0;

end

end

endmodule

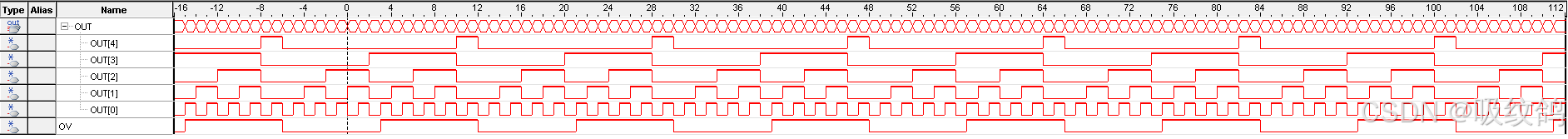

BDF文件

仿真结果

signaltap抓取结果

3.如果时钟是50MHz,把OV接 到一个LED上,能看见什么现象,为什么?

结果·:频率太高,看不出灯在闪烁,灯一直常亮。

816

816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?