写在前面:本篇内容来自胡振波先生所著的《手把手教你设计CPU——RISC-V处理器》,并附加个人学习心得,纯用以个人学习笔记。强烈推荐想要系统学习RISC-V处理器的同学们去看一下这本书,深入浅出、干货满满。

处理器流水线结构,是处理器微架构最基本的一个要素,承载并决定了处理器其他微架构细节。

目录

概述

1. 流水线概念起源

流水线概念起源于工业制造领域。以汽车制造为例,装配一辆汽车有四个步骤:

冲压、焊接、涂装、总装。

在第一辆汽车完成前一项工序,进入后一项工序时,第二辆汽车进入前一项工序,以此类推。这种生产方式如流水一般不息不止,故名流水线。

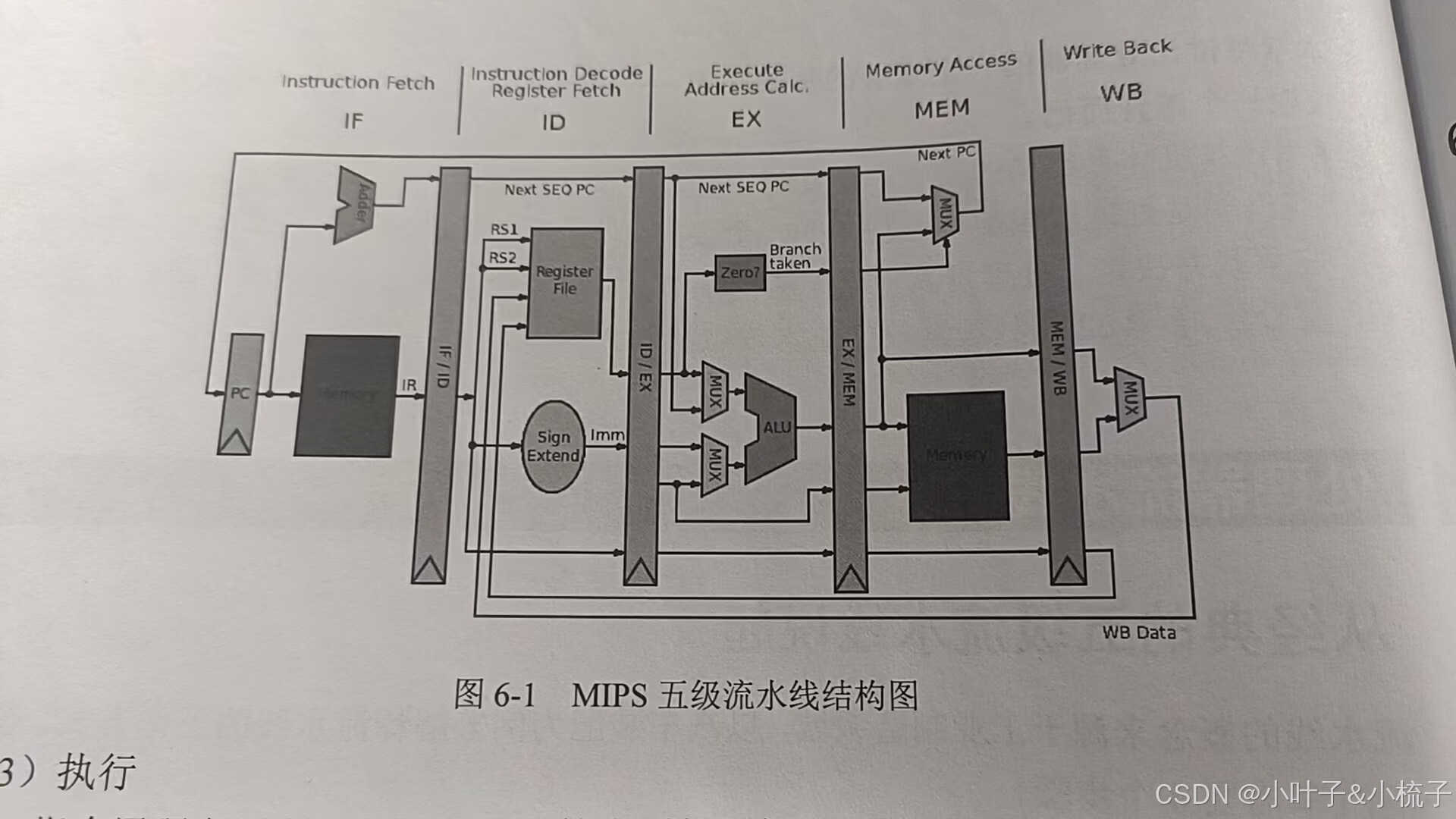

2. 经典MIPS五级流水线

一条指令的生命周期可以分为如下步骤:

(1). 指令取值(IF):将指令从存储器中读出来。

(2). 译码(ID):将取出的指令进行翻译。译码后,得到指令所需的操作数寄存器索引,使用索引从通用寄存器组中读出操作数。

(3). 执行(IE):译码后已知计算类型和操作数,即可对指令执行运算。如:指令为一条加法运算指令,则对操作数加法操作。此阶段一般需要用到算法逻辑部件运算器(ALU),作为执行运算的硬件单元。

(4). 访存(MEM):使用存储器访问指令,将数据从存储器中读出或写入。

(5). 写回(WB):将指令执行的结果写回通用寄存器组。对于普通运算指令,结果为“执行”后的计算值;对于存储器读指令,结果为“访存”时从存储器中取出的数据。

理论上,如果流水线没有停顿,每个时钟周期都可以完成一条指令。

3. 流水线VS状态机

ASIC电路广泛采用流水线思想,其本质上是以面积换性能、以空间换时间的方法。如:五级流水线增加了五组寄存器,每一流水线级数内部都有各自的组合逻辑数据通路,彼此间无复用资源,面积开销较大。但不同流水线级数可以同时做不同任务,优化了性能、时序,增加了吞吐率。

状态机是流水线的“取反”,也被大部分ASIC采用,本质是以性能换面积、以时间换空间的方法。

因此,具体设计中考虑侧重面积还是侧重性能,来决定选择哪一种方式。

4. 流水线深度(级数)

流水线每一级都由寄存器组成。级数越多,每一级流水线内部硬件逻辑越少,可以实现更高主频、更高吞吐率、更高性能,但会消耗更多的寄存器与面积。

由于每一级流水线需要握手,最后一级的反压信号可能会串扰最前一级造成时序问题。

流水线冲刷(PF):取值阶段无法知道条件跳转结果,因此只能预测。到流水线末端,通过实际运算才能知道该分支跳转结果。如果预测值和实际跳转结果不同,也就是预测失败,需要将预取的错误指令流丢弃,重新取正确指令流。流水线深度越深,预测失败的功耗就越大,浪费严重。

| 流水线越深 | |

| 益处 | 弊处 |

| 高频、高吞吐率、高性能 | 寄存器/面积消耗大 |

| 最后一级反压信号引起时序问题 | |

| 预测失败的功耗浪费严重 | |

注:书中在此处举例剖析了市场上流水线级数两种变化趋势,感兴趣的朋友自行查阅。

流水线中反压问题

对于流水线最后一级的反压可能引起的时序问题,通常有如下三种方法解决:

1. 取消握手

可杜绝反压问题,时序表现好,但可能造成功能错误或指令丢失。因此,这种方法一般要配合其他机制(如:重执行、预留大缓存等),故整体硬件复杂度较高,仅用于高级处理器设计。

2. 加入乒乓球缓存

此方法采用面积换时序的思想,通过使用乒乓缓存(两个表项)替换普通一级流水线(一个表项),使此级流水线向上一级流水线握手时只关注是否有空的表项,无需后一级握手接收信号串扰上一级。

3. 加入前向旁路缓存

此方法采用面积换时序的思想,通过额外增加旁路缓存(一个表项),将后向握手信号时序路径切断,对前向路径无影响。蜂鸟E200设计中采用此方法,可以有效解决反压时序问题。

流水线中冲突

1. 资源冲突

指流水线中硬件资源冲突,最常见运算单元冲突,如:除法器需要多个时钟周期完成运算,前一条除法指令未完成时,后一条除法指令需要除法器,则造成资源冲突。

解决方法:复制硬件资源或流水线停顿等待硬件资源。

2. 数据冲突

指不同指令间操作数存在数据相关性造成的冲突,主要有以下三种:

(1). WAR(先读后写)相关性:“后序执行的指令需要写回结果寄存器索引”与“前序执行的指令需要读取源操作数寄存器索引”相同时。后序指令不能比同WAR相关性的前序指令先执行,否则会使前序指令读取到错误索引。

(2). WAW(先写后写)相关性:“后序执行的指令需要写回结果寄存器索引”与“前序执行的指令需要写回结果寄存器索引”相同时。后序指令不能比同WAW相关性的前序指令先执行,否则前序指令的写回结果会覆盖后序指令的写回结果。

(3). RAW(先写后读)相关性:“后序执行的指令需要读取源操作数寄存器索引”与“前序执行的指令需要写回结果寄存器索引”相同时。后序指令不能比同RAW相关性的前序指令先执行,否则会使后序指令读取到错误索引。(真数据相关:无法通过寄存器重命名解决)

对WAR、WAW相关性解决方法:寄存器重命名。如:在Tomasulo算法中通过保留站和ROB(Re-order Buffer)完成,或采用纯物理寄存器。

对RAW相关性解决方法:通过动态调度尽可能减少流水线停顿等待时间。一方面,采用数据旁路传播技术,尽可能让前序指令计算结果更快地旁路传播给后序相关指令操作数;另一方面,尽可能让后序相关指令在等待过程中不阻塞流水线,使无关指令顺利执行。

实现上述动态调度两方面的手段:在每个运算单元前配置乱序发射队列,发射队列仅追踪RAW相关性而不存放操作数,可以做到很深(如:16个表项)。在发射队列中的指令解除相关性后发射,读取物理寄存器组,再发送给运算单元计算。

蜂鸟E200处理器流水线总览

主要含有的流水线级数为:IFU(第一级,取指)、EXU(第二级,译码、执行)、WB(第二级,写回,与EXU位于同一个时钟周期)、LSU(第三级,访存)。

严格说,蜂鸟E200为变长流水线结构,因为第三级的LSU需要第二级的WB写回结果。

665

665

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?