一、AXI简介

AMBA3.0中新增加了一种总线——AXI(Advanced eXtensible Interface,高级扩展接口)。

AMBA AXI 协议的目标是高性能、高频的系统设计,其包含了若干特性。

-

适合高带宽和低延迟的设计

-

提供高频操作,无需使用复杂的桥

-

满足各种组件的接口要求

-

适合具有高初始延迟的存储控制器

-

为互连架构实现提供灵活性

-

向后兼容现有 AHB 和 APB 接口

AXI 协议的关键特征有:

-

分离的地址/控制和数据通道

-

使用字节选通的方式实现非对齐传输(byte strobes选通byte有效)

-

采用基于突发的传输,主机只提供起始地址(brust传输)

-

分离的读写数据通道,提供低成本的 DMA 访问

-

支持发送多个 outstanding 地址(注:outstanding 是指,地址和数据传输并没有严格的先后要求,即在处理两个不同的事务时可以不必等待一个 transaction 处理完之后再处理另一个,大大提高系统处理效率)

-

支持乱序(out-of-order transaction)传输(注:out-of-order 是指,数据传输时可以根据不同 ID 而对顺序没有要求,但是相同 ID 的 transaction(事务) 必须按顺序传输。所以重要的是通过 ID 来区分,而 outstanding 则与 ID 无关)

-

易于通过添加寄存器达到时序收敛(满足时序要求)

二、AXI架构

AXI 协议是基于突发(burst)的。

每个事务在地址通道上都具有地址和控制信息,来描述要传输的数据特性。

在主机和从机之间传输的数据,使用一个到从机的写数据通道,或一个到主机的读地址通道。

在写事务中,所有数据流是从主机到从机的, AXI 协议有一个附加的写响应通道,可以让从机通知主机写事务完成。

AXI 协议允许:

-

允许在实际数据传输之前发送地址信息

-

支持多个 outstanding 传输

-

支持乱序(out-of-order)传输

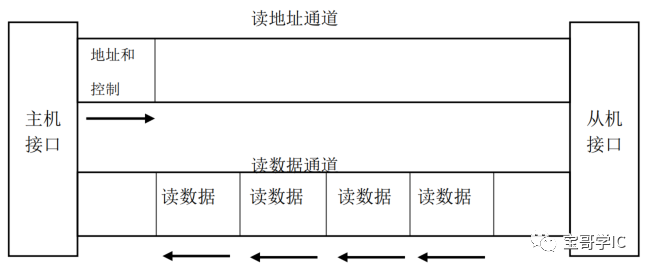

读操作

对于读操作,主机(master)通过AR通道发送读事务地址,从设备(slave)通过R通道返回给主机所需要的数据,如下图:

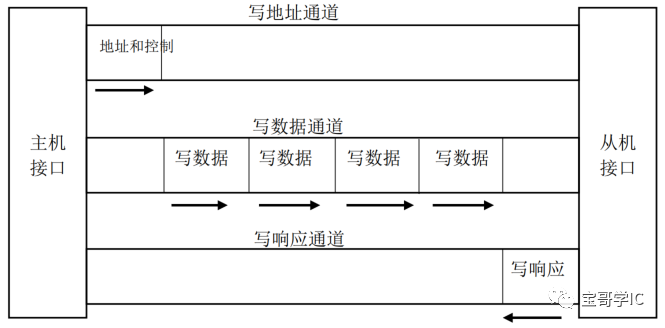

写操作

对于写操作,主机通过AW通道发送写事务地址,并通过W通道把数据发送给从设备,而从设备接收到数据后,需要通过B通道返回一个响应给主机,整个过程结束。

AXI的五个通道是单方向的,这样做的好处是可以对每个通道单独优化,而且当经过复杂的片上网络时,能够优化时序减少延迟。

AXI支持突发(burst)传输,乱序(out of order)传输,极大地提高了数据吞吐能力,在满足高性能要求的同时,又减少了功耗。

读和写的不同之处,一是数据方向不一样,读数据没有响应通道。

2.1通道定义

每个独立的通道都采用的VALID/READY握手机制。正是因为有了这个机制,发送方(Source)和接收方(Destination)才都有能力控制传输。

发送方通过职位VALID信号,来告诉接收方,自己已经将地址、数据或控制信息信息准备好;

而接收方通过置位READY信号,来告诉发送方,自己准备好了接收数据。只要有任何一方没准备好,传输就不能进行。

读数据通道和写数据通道都包含一个 LAST 信号来表示一个事物中最后一个数据项的传输何时发生。

注意:发送方不总是主机,比如读数据通道上,发送方就是从设备,主机是接收方。

AXI有五个独立的事务通道,分别是:

读地址(Read Address,简称AR)

读数据(Read Data,简称R)

写地址(Write Address,简称AW)

写数据(Write Data,简称W)

写响应(Write response,简称B)

读和写地址通道

读和写事物都各自有自己的地址通道。地址通道用于传送一次传输所需的所有地址和控制信息。

AXI 协议支持以下机制:

-

长度可变的突发,每个突发中的数据传输个数可以从 1 到 16 个

-

突发中一个数据传输的大小可以是 8-1024 bits

-

回环,增量或固定长度突发模式

-

使用独占或锁定访问的原子操作

-

系统级高速缓存和缓存控制

-

安全和特权访问

读数据通道

读数据通道用于从从机向主机返回读数据和任何读响应信息。读数据通道包含:

-

数据总线,宽度可以是 8, 16, 32, 64, 128, 256, 512 或 1024 bits

-

一个表示读事物完成状态的读响应信号

写数据通道

写数据通道用于从主机向从机传输写数据,包括:

-

数据总线,宽度可以是 8, 16, 32, 64, 128, 256, 512 或 1024 bits

-

每 8 bits 数据一个字节选通信号,用来表示数据的哪个字节有效WSTRB[3:0]

写数据通道的信息通常是被缓存的,以便主机在没有得到从机前一次写事物确认的情况下可以执行新的写事物。

写响应通道

从机使用写响应通道来响应写传输。所有写传输都要求在写响应通道上返回完成信号。

对每个突发,完成信号只产生一次,而不是突发中每个单个的数据传输都会产生一次完成信号。

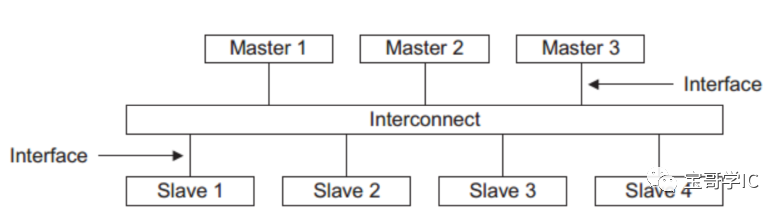

2.2典型系统

三、信号

3.1全局信号

| 名称 | 来源 | 描述 |

| ACLK | Clock source | 全局时钟信号。所有信号都在时钟的上升沿采样。 |

| ARESETn | Reset source | 全局复位信号,低电平有效。 |

3.2写地址通道信号

| 名称 | 来源 | 描述 |

| AWID[3:0] | 主机 | 写地址 ID。该信号为写地址组信号的 ID tag |

| AWADDR[31:0] | 主机 | 写地址。在一个写突发事务中,写地址总线给出了第一个传输的地址。 |

| AWLEN[3:0] | 主机 | burst长度。突发长度给出了一个突发中准确的传输个数。 |

| AWSIZE[2:0] | 主机 | burst大小。该信号表示突发中每个传输的大小。 |

| AWBURST[1:0] | 主机 | burst类型。brust的类型和大小决定了突发中每个传输的地址是怎么计算的。 |

| AWLOCK[1:0] | 主机 | 锁定类型。 |

| AWCACHE[3:0] | 主机 | Cache类型。这信号指明事务的可缓存、可高速缓存、write-through、write-back、allocate attributes信息。 |

| AWPROT[2:0] | 主机 | 保护类型。 |

| AWVALID | 主机 | 写地址有效。该信号表示有效写地址和控制信息准备好: 1 = 地址和控制信息有效。0 = 地址和控制信息无效 , 这个信号会一直保持,直到AWREADY变为高。 |

| AWREADY | 从机 | 写地址准备好。这个信号用来指明从机已经准备好接受地址和控制信息了。 1 = 从机准备好,0 = 从机没准备好 |

3.3写数据通道信号

| 名称 | 来源 | 描述 |

| WID[3:0] | 主机 | 写 ID tag。该信号为写数据传输的 ID tag。 WID 值必须和写事务的 AWID 值相同。 |

| WDATA[31:0] | 主机 | 写数据。写数据总线可以是 8、16、32、64、128、256、1024bits宽 |

| WSTRB[3:0] | 主机 | 写选通信号。该信号表示 memory 中哪个字节通道被更新。 写数据总线的每8 位具有一个写选通位。 |

| WLAST | 主机 | 最后一次写。该信号表示一个写突发中的最后一次传输。 |

| WVALID | 主机 | 写有效。该信号表示写数据和选通信号有效: 1 = 写数据和选通信号有效 ;0 = 写数据和选通信号无效 |

| WREADY | 从机 | 写准备好。该信号表示从机可以接收写数据: 1 = 从机准备好;0 = 从机没有准备好 |

3.4写响应通道信号

| 名称 | 来源 | 描述 |

| BID[3:0] | 从机 | 响应 ID tag。该信号是写响应的 ID tag。 BID 值必须和从机响应的写事物的AWID 值相同。 |

| BRESP[1:0] | 从机 | 写响应。该信号表示写事物的状态。 允许的响应有:OKAY,EXOKAY,SLVERR 和 DECERR。 |

| BVALID | 从机 | 写响应有效。该信号表示一个写响应有效: 1 = 写响应有效;0 = 写响应无效 |

| BREADY | 主机 | 响应准备好。该信号表示主机可以接收一个写响应: 1 = 主机准备好;0 = 主机没有准备好 |

3.5读地址通道信号

| 名称 | 来源 | 描述 |

| ARID[3:0] | 主机 | 读地址 ID。该信号是读地址组信号的 ID tag。 |

| ARADDR[31:0] | 主机 | 读地址。读地址总线给出了一个读突发事物中的第一个传输的地址。主机只提供突发的第一个地址,和地址一起被发送的控制信号决定了突发中剩余传输的地址是怎么计算的。 |

| ARLEN[3:0] | 主机 | 突发长度。该信号给出一个突发中准确的传输个数。 该信息决定了与地址相对应的数据传输次数。 |

| ARSIZE[2:0] | 主机 | 突发大小。该信号表示突发中每个传输的大小。 |

| ARBURST[1:0] | 主机 | 突发类型。 突发类型和突发大小决定了突发中每个传输的地址是怎么计算的。 |

| ARLOCK[1:0] | 主机 | 锁定类型。 |

| ARCACHE[3:0] | 主机 | cache 类型。 |

| ARPROT[2:0] | 主机 | 保护类型。 |

| ARVALID | 主机 | 读地址有效。该信号表示,当为高时,读地址和控制信息有效,并会保持稳定,直到地址确认信号 ARREADY 拉高。 1 = 地址和控制信息有效;0 = 地址和控制信息无效 |

| ARREADY | 从机 | 读地址准备好。该信号表示从机准备好接收地址和相应的控制信号: 1 = 从机准备好;0 = 从机没有准备好 |

3.6读数据通道信号

| 名称 | 来源 | 描述 |

| RID[3:0] | 从机 | 读 ID tag。该信号是从机产生的读数据组信号的 ID tag。 RID 的值由从机产生,必须与从机响应的读事物的 ARID 值相同。 |

| RDATA[31:0] | 从机 | 读数据。 |

| RRESP[1:0] | 从机 | 读响应。该信号表示读传输的状态。 允许的响应有:OKAY、EXOKAY、SLVERR 和DECERR。 |

| RLAST | 从机 | 最后一次读。该信号表示一个读突发中的最后一次传输。 |

| RVALID | 从机 | 读有效。该信号表示请求的读数据有效,并且可完成读传输: 1 = 读数据有效;0 = 读数据无效 |

| RREADY | 主机 | 读准备好。该信号表示主机可以接收读数据和响应: 1 = 主机准备好;0 = 主机没有准备好 |

AXI是AMBA3.0中引入的高级扩展接口,目标是实现高性能和高频系统设计。它提供了分离的地址/控制和数据通道,支持非对齐传输、突发传输、多outstanding地址、乱序传输和灵活的互连架构。AXI协议包括读写操作,每个操作都有独立的通道,通过VALID/READY机制控制传输,并有写响应确认。这种设计优化了数据吞吐量,同时减少了功耗。

AXI是AMBA3.0中引入的高级扩展接口,目标是实现高性能和高频系统设计。它提供了分离的地址/控制和数据通道,支持非对齐传输、突发传输、多outstanding地址、乱序传输和灵活的互连架构。AXI协议包括读写操作,每个操作都有独立的通道,通过VALID/READY机制控制传输,并有写响应确认。这种设计优化了数据吞吐量,同时减少了功耗。

417

417

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?