目录

1. 饱和失真(Saturation Distortion)

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-优快云博客

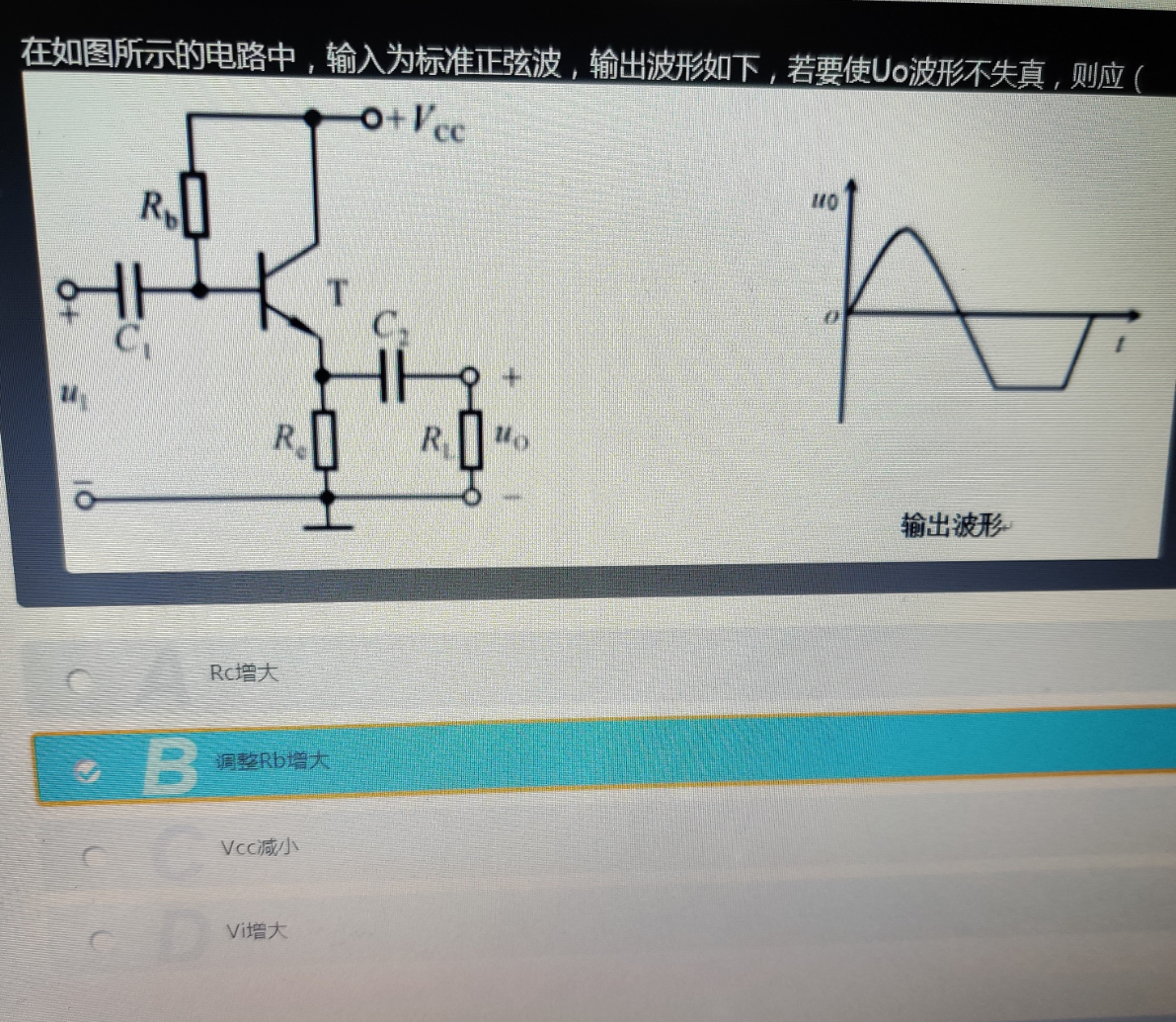

【硬件-笔试面试题】硬件/电子工程师,笔试面试题-8,(知识点:放大器的饱和失真与截止失真)

这是一道大疆笔试题

1、题目

2、解答

NPN型:如果波形Uo顶部失真(变平),则属于截止失真Q小。底部失真代表饱和失真Q大。

PNP型:Uo顶部失真代表饱和失真Q大,底部失真是截止失真Q小。Ube、Uce极性为−导致的Ube、Uce极性为−导致的

截止失真Q小说明Ib太小,你可以通过减少Rb来增大Ib。

如果是饱和失真Q大,说明Ib(Ic)太大,必须用增大Rb来减少失真。

后面两点,对于NPN还是PNP都是适用的。

步骤一:分析输出波形失真原因

从输出波形可以看出,波形出现了饱和失真。在晶体管共射放大电路中,饱和失真通常是由于静态工作点过高,导致晶体管在输入信号负半周时进入饱和区而产生的。

步骤二:提出解决办法

截止失真Q小说明Ib太小,你可以通过减少Rb来增大Ib。

如果是饱和失真Q大,说明Ib(Ic)太大,必须用增大Rb来减少失真。

3、相关知识点

1. 饱和失真(Saturation Distortion)

定义

当晶体管的工作点进入饱和区时,集电极电流 ICIC 不再随基极电流 IBIB 线性增加,导致输出信号顶部被“削平”,称为饱和失真。

原因

-

输入信号幅度过大,使晶体管进入饱和区(VCEVCE 过小,无法维持放大状态)。

-

偏置电路设计不合理,静态工作点(Q点)过高(靠近饱和区)。

表现

-

输出波形:信号的正半周(或负半周,取决于电路类型)被压缩或削平。

-

晶体管状态:VCE≈0.2VVCE≈0.2V(硅管),ICIC 达到最大值且不再受 IBIB 控制。

2. 截止失真(Cut-off Distortion)

定义

当晶体管的工作点进入截止区时,基极电流 IBIB 为零或反向,导致输出信号底部被“削平”,称为截止失真。

原因

-

输入信号幅度过大,使晶体管在部分周期内完全截止(IB≤0IB≤0)。

-

偏置电路设计不合理,静态工作点(Q点)过低(靠近截止区)。

表现

-

输出波形:信号的负半周(或正半周,取决于电路类型)被压缩或削平。

-

晶体管状态:IB=0IB=0,IC≈0IC≈0,晶体管处于关断状态。

3. 对比总结

| 特性 | 饱和失真 | 截止失真 |

|---|---|---|

| 发生区域 | 晶体管进入饱和区(VCEVCE 极小) | 晶体管进入截止区(IB=0IB=0) |

| 波形表现 | 信号顶部被削平 | 信号底部被削平 |

| 原因 | Q点过高或输入信号过大 | Q点过低或输入信号负向过大 |

| 解决方法 | 降低Q点或减小输入信号幅度 | 提高Q点或减小输入信号幅度 |

4. 如何避免失真?

-

合理设置静态工作点(Q点):

-

确保Q点位于负载线中点,使信号在放大区内对称摆动。

-

-

限制输入信号幅度:

-

避免输入信号过大导致晶体管进入饱和或截止区。

-

-

使用负反馈:

-

引入负反馈电路可扩展线性放大范围,减少失真。

-

题目汇总:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-优快云博客

5368

5368

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?