(1)ic产业分为:设计、测试、制造、封装

(2)硬件描述语言(HDL)是一种高级程序设计语言,通过对数字电路和系统的语言描述,可以对数字集成电路进行设计和验证。应用于建模、仿真、设计和验证、综合等各个阶段。

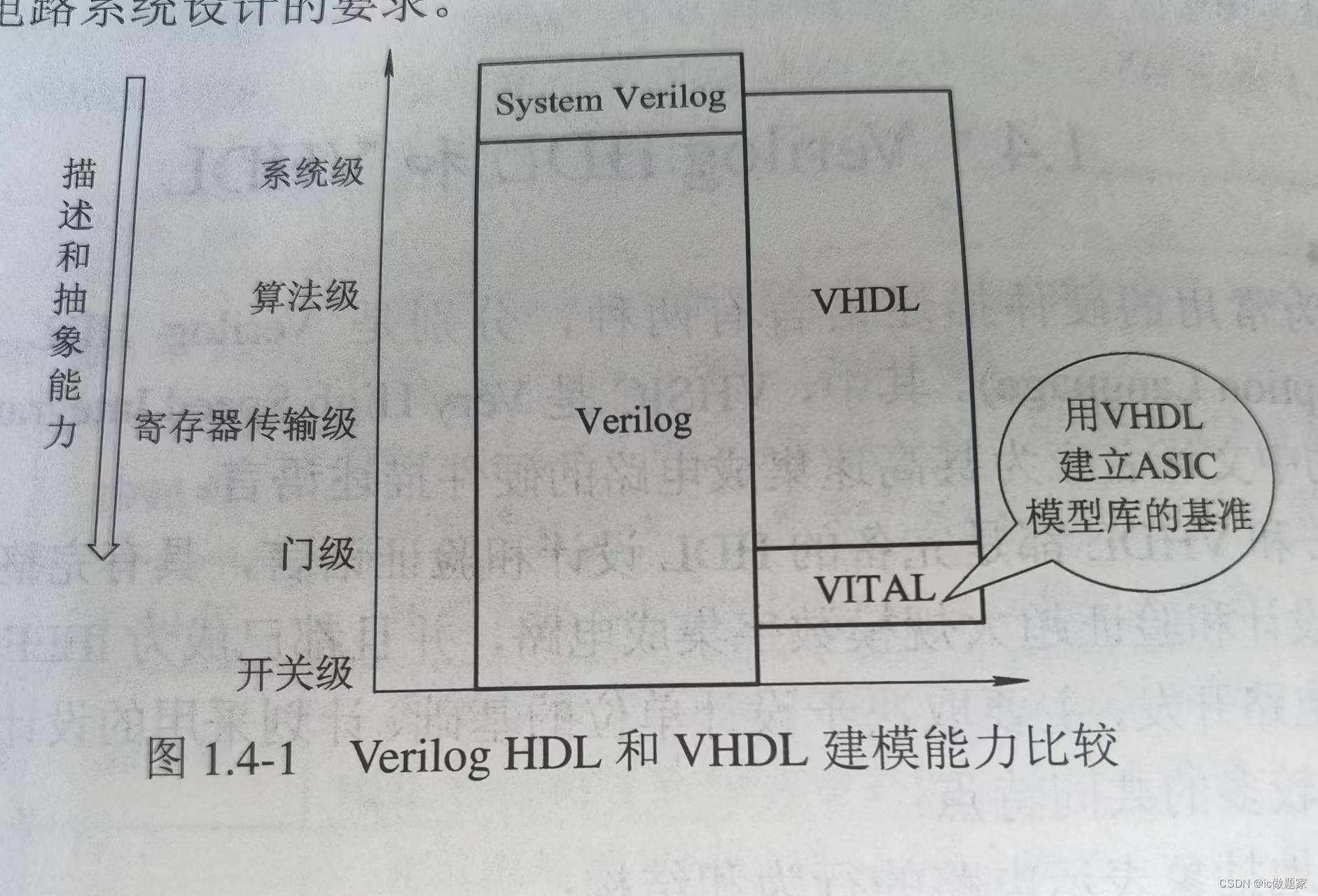

(3)verilog与VHDL是目前主要的HDL。都被采纳为IEEE国际标准。

(4)verilog与VHDL的区别:

1)在设计方法方面,VHDL灵活性差、设计规则繁琐,但由于VHDL语言规则缜密,其可综合性和代码一致性很强。

2)在设计范围方面,如图可知, VHDL不具备开关级电路描述语言。

(5)verilog在ic设计中的优缺点:

1)优点: 高效性、灵活性

代码易于维护、可移植性强

测试和仿真功能强大

2)缺点:依赖于相应的EDA工具,且相对于高级语言可读性不好。

(6)软核:是指经过功能验证、5000门以上的可综合verilog H

本文介绍了IC产业的四个主要环节,并详细阐述了硬件描述语言HDL的作用,尤其是Verilog和VHDL的特点。内容涵盖Verilog在IC设计中的优缺点,软核、固核和硬核的概念,以及IP核的重要性。此外,还提及了常见的IC设计、仿真和综合工具,如Cadence、Synopsys和Mentor公司的产品。

本文介绍了IC产业的四个主要环节,并详细阐述了硬件描述语言HDL的作用,尤其是Verilog和VHDL的特点。内容涵盖Verilog在IC设计中的优缺点,软核、固核和硬核的概念,以及IP核的重要性。此外,还提及了常见的IC设计、仿真和综合工具,如Cadence、Synopsys和Mentor公司的产品。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1449

1449

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?